262 Computer Architecture and Organization

the highest priority. The next default priority is assigned to RST7.5 interrupt. Then it is RST6.5, RST5.5

and nally the INTR, the interrupt with lowest priority. So, we see from this analogy that some priority

to be assigned for different devices attached to any bus for the purpose of arbitration.

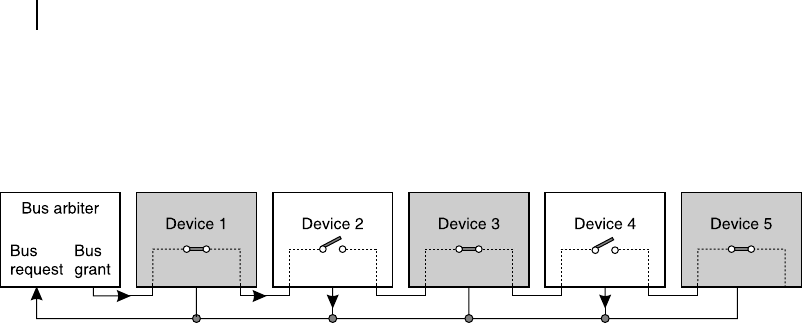

Figure 8.19 Bus arbitration by daisy chaining

A simpler method of bus arbitration is to go for daisy chaining , as shown in Figure 8.19 . In this case,

assuming several devices are attached with the bus and the bus-arbiter, all need to share the common

bus-request as well as bus-grant signal lines. Note that the bus-grant signal line, unlike bus-request

signal line, is generated from the bus-arbiter and passes through the switch of each device to the next

device. What is the purpose of this mechanism?

Let us assume that device 2 and device 4 have simultaneously placed the bus-request to the bus

arbiter. Note that as soon as a device places a bus request, it opens its internal switch for the daisy

chained bus-grant signal line, as shown in Figure. 8.18. As the bus arbiter grants the bus by activating

the bus-grant line, the bus-grant signal reaches up to device 2 and is unable to travel further because of

the opened switch of device 2. Therefore, device 4 is denied the bus-grant at that moment and device 2

uses the bus. After its requirement is complete, device 2 closes its internal switch and then device 4 has

a turn to use the bus. Therefore, in this mechanism, closer the device is to the bus arbiter, higher would

be its priority to use the bus.

In some arbitration scheme, multiple bus request and multiple bus-grant lines are provided with

pre-assigned priority levels. There may be 2, 4, 8 or even 16 lines to allow different priority to different

group of devices.

8.12 I/O PROCESSOR

During early days of computers, the system was primitive and the norm was to entrust the processor to

communicate with simple I/O devices directly. This method exists even today in small microprocessor

based systems. The method adopted in this case is the polling method and the processor remains tied up

with the concerned I/O device until the communication is complete.

To release the processor from the burden of waiting for I/O communication to be complete, interrupt

driven I/O was the next improvement where the processor would react only when it is essential and for

the remaining time it stays free to look after its other duties.

Here also, we observe that even the interrupt driven data communication consumes some amount

of processor time, which becomes larger with the quantity of data transaction. At the next stage of

improvement, DMA was introduced so that the processor simply initiates the transaction procedure and

released thereafter.

M08_GHOS1557_01_SE_C08.indd 262M08_GHOS1557_01_SE_C08.indd 262 4/29/11 5:15 PM4/29/11 5:15 PM

..................Content has been hidden....................

You can't read the all page of ebook, please click here login for view all page.