278 Computer Architecture and Organization

Even if we discard the complexity of interrupts, we must provide some mechanism in our example

system to fetch instructions. For that, we have to include additional registers and data paths in Figure 9.2 .

Moreover, we shall need additional control signals to be generated to operate these extra features. As it is

already indicated, all these may be implemented either by hardware or by software method.

9.4 HARDWIRED CONTROL

In hardwired control method, all relevant control signals are generated through hardware by directly

decoding the opcode. For the purpose of sequencing, each instruction have to be divided into smaller

relevant steps, related to each control signal, already nalized by us. Instruction-wise these details are

presented in Table 9.2 , 9.3 , 9.4 and 9.5 .

9.4.1 Working of Hardwired Control

Schematically, basic structure of hardwired control for a processor is shown in Figure 9.5 . Its nal

output is the set of control signals generated by the control unit (CU). In our example case, we have

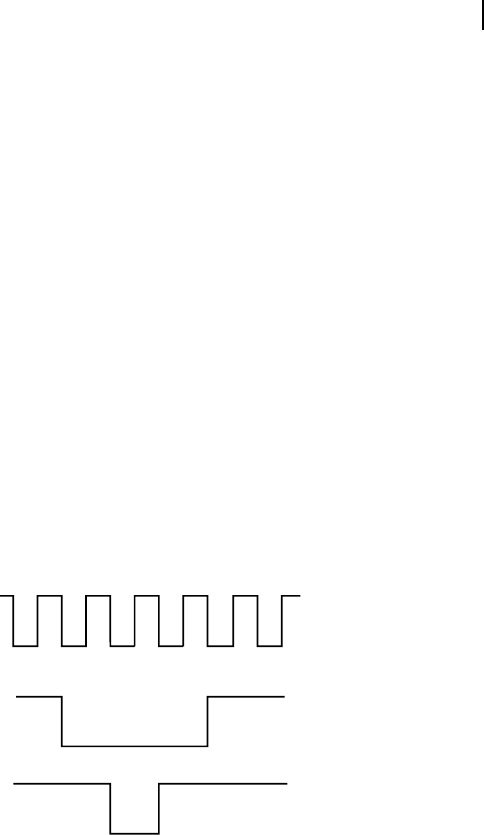

Figure 9.4 Simplified duty-cycle of a processor

Figure 9.5 Basic structure of hardwired control

M09_GHOS1557_01_SE_C09.indd 278M09_GHOS1557_01_SE_C09.indd 278 4/29/11 5:16 PM4/29/11 5:16 PM

Microprogramming and Microarchitecture 279

designated these control signals as S1, S2, ENX and so on. This control unit is assisted by two separate

functional blocks (inputs). The rst one is related with system timings and is shown at the top of control

unit in Figure 9.5 . Basic input for this block is the system clock, and by using a counter, it generates all

necessary timing signals and feeds the control unit.

The second functional block is shown at the left of the CU. Input for this block is the data from IR,

which holds the current or ongoing instruction. This is decoded by the instruction decoder and the nec-

essary outputs are generated for the control unit. The hardware of the control unit is designed to generate

all necessary control signals for the ongoing instruction in proper sequence.

To clarify some details, let us take the example of execution of an instruction from our set of instruc-

tions presented at the beginning of this chapter. Let us take the instruction Load accumulator by R0 , the

instruction whose control signal details are presented at the top of Table 9.2 . Figure 9.6 shows the timing

diagram of all control signals (only two in this case) to execute this instruction, along with the system

clock timings. This clock timing is used to generate ENA0 and S5, as shown in Figure 9.6 . Observe

from Figure 9.5 that the clock is fed to the counter, whose output is received by the CU along with the

output from instruction decoder.

Referring the opcode for Load accumulator by R0, which is 0000B, its least signi cant two bits may

be used to target the relevant register (one from R0 – R3) and most signi cant two bits may be decoded

to generate the instruction Load accumulator by . With the help of counter output and the decoded

instruction, the control unit generates the required signals in proper sequence, through hardware logic

circuits, which we have explained in Chapter 3. For a complete hardware design of a control unit, please

refer the solved example at the end of this chapter.

Figure 9.6 Timing diagram of control signals for the instruction

load A by R0

Clock

ENA0

S5

9.4.2 Advantages of Hardwired Control

The major advantage of hardwired control is that it works much faster than software control (micro-

programmed control). We shall discuss later why this additional time is necessary for software control.

9.4.3 Disadvantages of Hardwired Control

The major disadvantage of hardwired control is its modi cation. Note that if any minor change has to

be incorporated in any instruction, the necessary hardware design need to be redesigned and changed,

resulting in discarding of the already completed hardware design and related circuit details. Therefore,

once nalized, further modi cations are dif cult and expensive in this case.

M09_GHOS1557_01_SE_C09.indd 279M09_GHOS1557_01_SE_C09.indd 279 4/29/11 5:17 PM4/29/11 5:17 PM

..................Content has been hidden....................

You can't read the all page of ebook, please click here login for view all page.