456 Computer Architecture and Organization

The special feature of Format 3 (branch instructions) is bit-29, the annul bit . This bit-information

helps in compensating the delay generated during execution of conditional branches. If this bit is

cleared, then the instruction following the branch instruction is always executed regardless of whether

the branching has taken place or not. If the bit is set, then the branch-instruction-following-instruction

would be executed only if the branching takes place, otherwise not. In Format 3, four bits are reserved

to test four condition ags and any combination of these four bits may be considered for branching. A

24-bit wide two’s complement PC-relative address for branching is generated from the 22-bit address

within the instruction and adding two zeros at the least signi cant end of these 22 bits.

The last format, i.e., Format 4, is exclusive for call instruction supplying 30-bit relative address. Just

like the previous case, two zeros are added at the end of these 30 bits to obtain the target address. To

conclude our discussions, the complete integer instruction set of UltraSPARC is presented now.

B.8 INSTRUCTION SET

All user available instructions of UltraSPARC are presented in following six tables. Floating point

instructions, processor reset instructions and cache management instructions are not included here. Note

that all arithmetic and Boolean instructions are register oriented without any need to get operand from

memory or store the result of the operation in memory. In these cases processor registers are to contain

necessary operands and accommodate results. Moreover, these instructions allow three-register format.

So two source registers and one destination register (result storing register) may be accommodated

within these instructions, using Format 1a.

Table B.1 presents load and store instructions dealing with 8-, 16-, 32- and 64-bit data sets. When

smaller number of data set bits 8 or 16 are loaded within 32-bit registers, most signi cant bits may be

lled with either all 1s or all 0s. In this and all other tables, ADDR indicates a valid memory address,

DST indicates the name of the destination register and SRC indicates the source register.

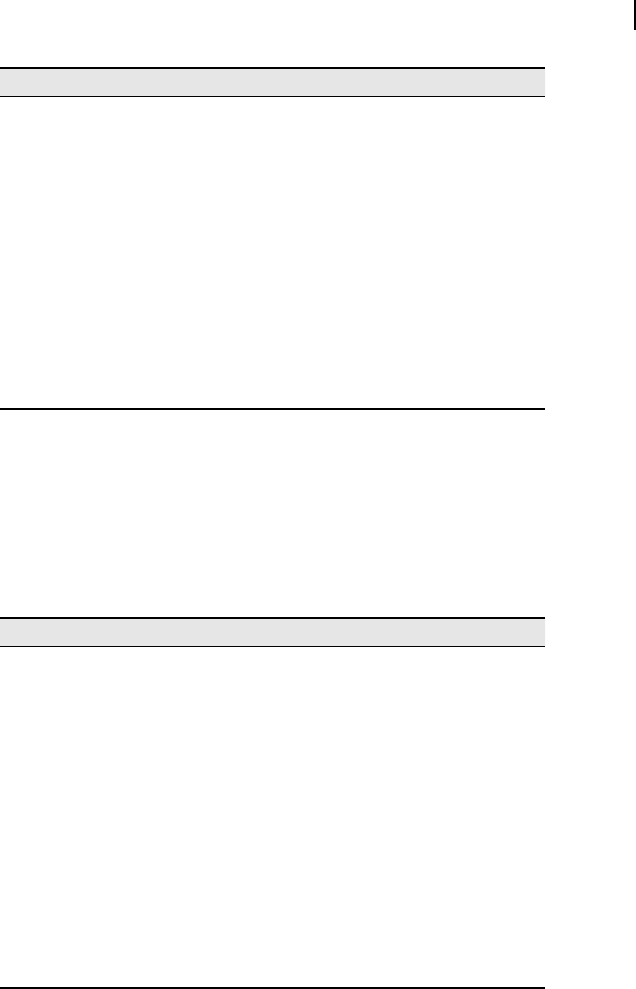

Figure B.5 Instruction formats of UltraSPARC

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Destination Opcode Source 1 Source 2

3-Register

Format 1a

Floating point operator

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Destination Opcode Source 1

Immediate

Format 1b

Immediate constant

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Destination

A

Condition

Opcode

PC-relative displacement

PC-relative displacement

Opcode

SETHI

Format 2

Immediate constant

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Branch

Call

Format 3

Format 4

0

1

Z02_GHOS1557_01_SE_C17_App_B.indd 456Z02_GHOS1557_01_SE_C17_App_B.indd 456 4/29/11 5:40 PM4/29/11 5:40 PM

SPARC and UltraSPARC 457

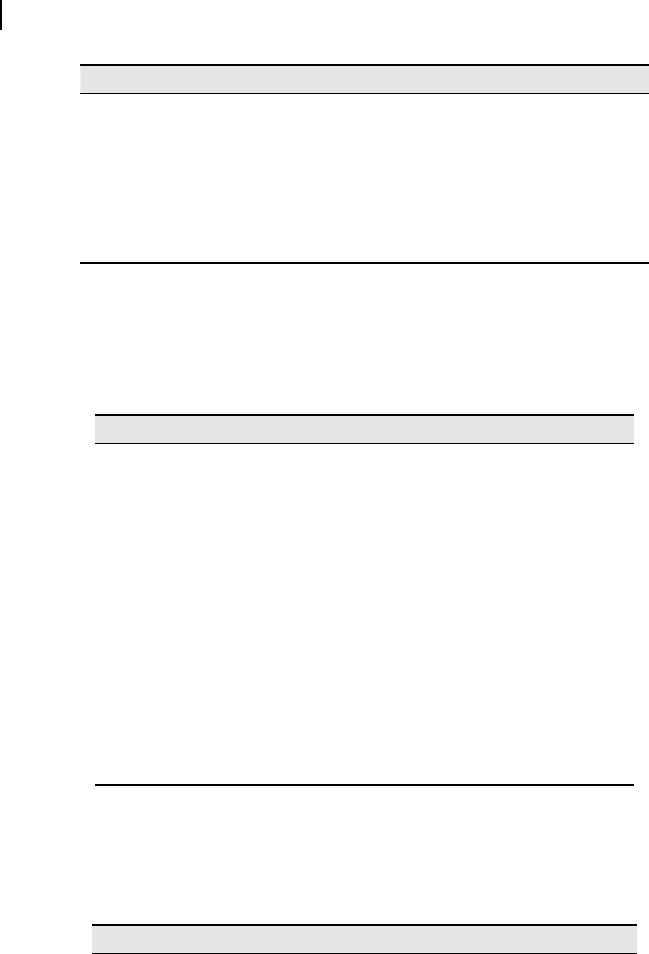

Instruction Brief description

LDSB ADDR, DST Load signed byte (8 bits)

LDUB ADDR, DST Load unsigned byte (8 bits)

LDSH ADDR, DST Load signed halfword (16 bits)

LDUH ADDR, DST Load unsigned halfword (16 bits)

LDSW ADDR, DST Load signed word (32 bits)

LDUW ADDR, DST Load unsigned word (32 bits)

LDX ADDR, DST Load extended (64 bits)

STB SRC, ADDR Store byte (8 bits)

STH SRC, ADDR Store halfword (16 bits)

STW SRC, ADDR Store word (32 bits)

STX SRC, ADDR Store extended (64 bits)

Table B.1 Load and Store instructions

Table B.2 presents the arithmetic instructions. Note the absence of increment by one and decrement

by one type instruction as those may be implemented by other available instructions for addition and

subtraction. In these and all other instructions, R1 indicates a source register and S2 indicates either a

source register or an immediate data.

Instruction Brief description

ADD R1, S2, DST Add

ADDCC R1, S2, DST Add and set icc

ADDC R1, S2, DST Add with carry

ADDCCC R1, S2, DST Add with carry and set icc

SUB R1, S2, DST Subtract

SUBCC R1, S2, DST Subtract and set icc

SUBC R1, S2, DST Subtract with carry

SUBCCC R1, S2, DST Subtract with carry and set icc

MULX R1, S2, DST Multiply

SDIVX R1, S2, DST Signed divide

UDIVX R1, S2, DST Unsigned divide

TADCC R1, S2, DST Tagged add

Table B.2 Arithmetic instructions

All shift and rotate type instructions are placed in Table B.3 . Note that in case of shift right logical ,

the least signi cant bit is shifted to most signi cant position after the shift operation, whereas for shift

right arithmetic , the least signi cant bit is lost and the most signi cant bit is copied to its old position

after shifting operation.

Z02_GHOS1557_01_SE_C17_App_B.indd 457Z02_GHOS1557_01_SE_C17_App_B.indd 457 4/29/11 5:40 PM4/29/11 5:40 PM

458 Computer Architecture and Organization

Instruction Brief description

SLL R1, S2, DST Shift left logical (32 bits)

SLLX R1, S2, DST Shift left logical extended (64 bits)

SRL R1, S2, DST Shift right logical (32 bits)

SRLX R1, S2, DST Shift right logical extended (64 bits)

SRA R1, S2, DST Shift right arithmetic (32 bits)

SRAX R1, S2, DST Shift right arithmetic extended (64 bits)

Table B.3 Shift and Rotate instructions

Six types of Boolean operations, namely AND, NAND, OR, NOR, XOR and XNOR are available

within Boolean instruction set presented in Table B.4 . In each case the operation may store the generated

conditions of the result if desired so.

Instruction Brief description

AND R1, S2, DST Boolean AND

ANDCC R1, S2, DST Boolean AND and set icc

ANDN R1, S2, DST Boolean NAND

ANDNCC R1, S2, DST Boolean NAND and set icc

OR R1, S2, DST Boolean OR

ORCC R1, S2, DST Boolean OR and set icc

ORN R1, S2, DST Boolean NOR

ORNCC R1, S2, DST Boolean NOR and set icc

XOR R1, S2, DST Boolean XOR

XORCC R1, S2, DST Boolean XOR and set icc

XNOR R1, S2, DST Boolean XNOR

XNORCC R1, S2, DST Boolean XNOR and set icc

Table B.4 Boolean instructions

Table B.5 presents all instructions related with program branching. Note that JMPL instruction may

also be used to implement a CALL instruction.

Instruction Brief description

BPcc ADDR Branch with prediction

BPr SRC, ADDR Branch on register

CALL ADDR Call procedure

RETURN ADDR Return from procedure

JMPL ADDR, DST Jump and link

SAVE R1, S2, DST Advance register windows

(Continued)

Z02_GHOS1557_01_SE_C17_App_B.indd 458Z02_GHOS1557_01_SE_C17_App_B.indd 458 4/29/11 5:40 PM4/29/11 5:40 PM

..................Content has been hidden....................

You can't read the all page of ebook, please click here login for view all page.