504 Computer Architecture and Organization

E.8 PIPELINE

As already mentioned earlier, MIPS processors are based on eight-stage pipeline, and the stages are

indicated as follows

R IF: Instruction Fetch, rst half

R IS: Instruction fetch, second half

R RF: Fetch operand from register

R EX: Execute the instruction

R DF: Data fetch, rst half

R DS: Data fetch, second half

R TC: Data cache tag check

R WB: Write back

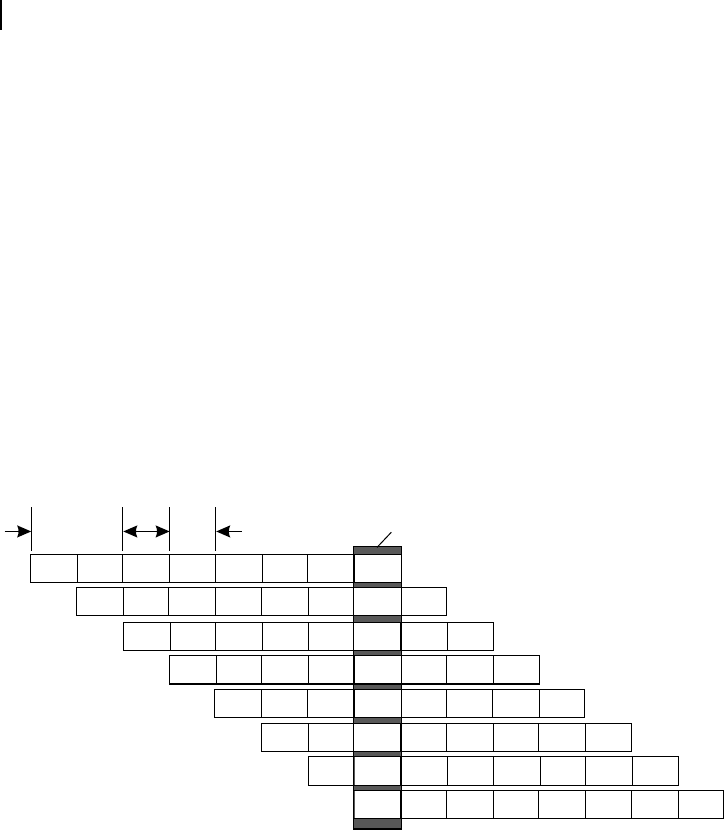

Typically, the pipeline operation, in general, would be as depicted in Figure E.7 , for general instruc-

tions execution.

Figure E.7 Instruction pipeline stages of MIPS R4000 (Courtesy: MIPS Technologies,

Inc.)

IF IS RF EX DF DS TC

IF IS RF EX DF DS WB

IF IS RF EX DF TC WB

IF IS RF EX DS TC WB

IF IS RF DF DS TC WB

IF IS EX DF DS TC WB

IF RF EX DF DS TC WB

IS RF EX DF DS TC WB

One master

clock cycle

One

P cycle

Current CPU cycle

WB

TC

DS

DF

EX

RF

IS

IF

During IF and IS, the virtual-to-physical address translation by the instruction TLB is completed.

In RF stage, the instruction is decoded by the instruction decoder and any eventual operand is fetched

from the relevant register. The next stage is the instruction execution stage and at this stage the virtual

branch target address for any eventual branch instruction is calculated by the ALU. Normal arithmetic

or logical operation is also completed at this stage by the ALU itself, for register to register instructions.

For register to register instructions, no operations are performed during next three stages, namely

DF, DS and TC. However, for load/store type instruction the relevant data is fetched and for branch type

instructions address translation and TLB update are initiated at this stage of DF. These are completed at

the next stage that is DS, including the storing operation for load/store type instructions.

Z05_GHOS1557_01_SE_C20_App_E.indd 504Z05_GHOS1557_01_SE_C20_App_E.indd 504 4/29/11 5:46 PM4/29/11 5:46 PM

..................Content has been hidden....................

You can't read the all page of ebook, please click here login for view all page.