MIPS R4000 505

The tag check for load/store type instructions and branch type instructions are performed at the TC

stage. Finally, during WB stage, the result of operation is written back to the register for register to reg-

ister instructions. No operation is performed at this stage for branch type instructions.

E.9 MEMORY MANAGEMENT

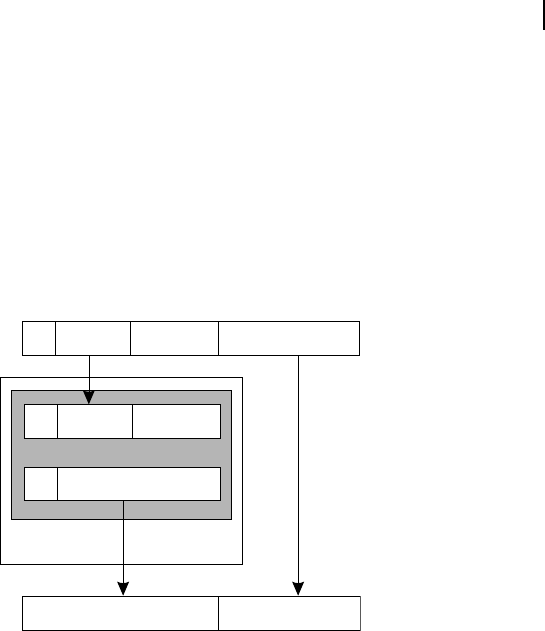

MIPS R4000 is provided with an ef cient on-chip memory management unit to help the processor to

translate the virtual address to physical address using its TLB. Schematically, it is represented through

Figure E.8 .

Figure E.8 Address conversion scheme of R4000 (Courtesy: MIPS Technologies, Inc.)

Virtual address

G ASID VPN

G

G

ASID VPN

PFN

Offset

TLB entry

TLB

PFN

Physical address

Offset

MIPS R4000 takes the help of its Translation Lookaside Buffer (TLB) for generating the physical

address from the virtual address. The method of translation is slightly different in 32-bit mode with

respect to 64-bit mode. First we discuss the general procedure adopted in both cases and then highlight

the related differences. The reader may note that in 32-bit mode, the available virtual memory is 2 GB

while in 64-bit mode it is 1 TB.

The TLB is a fully set associative memory capable of accommodating 48 different entries. Note that

each of the entry provides a mapping of an odd-even page-pair. Therefore, 48 entries within TLB are

capable of representing 48 page-pairs or 96 pages. At this stage we must keep in mind that the page size of

MIPS R4000 is variable and may be xed as any one of 4K, 16K, 64K, 256K, 1M, 4M and 16M locations.

When a virtual address to be converted to its physical address, each TLB entry is checked simultane-

ously for a match with the virtual address, extended by an address space identi er (ASID, stored in the

EntryHi register). If the entry is found within the TLB (a match or a hit), then the page frame number

(PFN) is available from the TLB, which, along with the offset, denotes the physical address. Note that

the offset part of the virtual address does not pass through TLB. If it is not found within TLB (mismatch

or miss), then the TLB is updated from the page table resident within memory. The new information

may be written at a software-selected location or at a random location identi ed by the system hardware.

An interesting fact may be noted here that in case of multiple matches, which would generate error, the

TLB is temporarily disabled by setting the TS (TLB-Shutdown) bit of the status register.

Z05_GHOS1557_01_SE_C20_App_E.indd 505Z05_GHOS1557_01_SE_C20_App_E.indd 505 4/29/11 5:46 PM4/29/11 5:46 PM

..................Content has been hidden....................

You can't read the all page of ebook, please click here login for view all page.