102 Computer Architecture and Organization

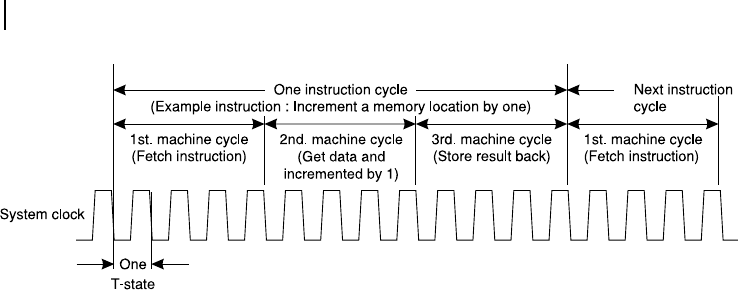

is carried out immediately after receiving the instruction byte within the processor. In other words, for every

case, instruction decoding is done at the end of the rst machine cycle. Does it not demand any extra time?

Well it depends. If it is a hardware-based decoding, then it does not need any extra time. However, in case of

micro-programming, it would consume one or two extra T-states. For example, Intel 8085 spends four T-states

for fetching the rst instruction byte during its rst machine cycle, while for subsequent machine cycles it

spends only three T-states. As a matter of fact, in its rst machine cycle rst three T-states are suf cient for

fetching the rst byte of instruction. Next T-state of the rst machine cycle is devoted for instruction decoding.

As the answer of the second question, we can say that the data would be incremented either at the end

of second machine cycle or at the beginning of the third machine cycle, depending upon the processor.

Here also, the adopted technique plays an important role.

5.3.6 Timings, Control and Response

Through the above discussions, it must be clear to the reader that timing and control play very important

roles in smooth and ef cient functioning of any processor. To further explain this concept, we may take

up the example of interrupt .

Although we shall have a detailed discussions on interrupt in Section 5.6, it may be introduced here

as an external asynchronous signal, which forces the processor to carry out something special for it by

branching to a pre-de ned address and, thus, executing a special program segment, known as inter-

rupt service routine (ISR). As this is an asynchronous signal, it may be activated at any time during

the execution of any instruction by the processor. However, the processor cannot leave an instruction’s

execution half-way to start doing something else for the sake of such an interrupting signal.

To solve this problem, processors reserve a particular time-slot for checking the existence of any inter-

rupt input signal during the execution of each and every instruction. For example, Intel 8085 processor

had reserved the penultimate T-state of the last machine cycle of any instruction for this interrupt signal

checking. If it is present, then the next instruction would not be executed immediately and the processor

would start executing from the interrupt’s ISR. We shall discuss more about it in the Section 5.6. However,

the modi ed owchart of the instruction cycle is presented in Figure 5.9 , where the previously explained

portion is shaded. The reader may compare it with Figure 5.6 .

5.4 REGISTER SET

To perform internal operations, all processors offer some internal registers, which can store temporary

information or some operands. Similar to read/write memory, these registers are nothing but a combina-

tion of several ip- ops. Most of these registers are user (programmer) accessible and a few are not.

The number of user accessible registers varies from processor to processor. Those processors that are

Figure 5.8 Example of instruction cycle, machine cycle and T-state correlation

M05_GHOS1557_01_SE_C05.indd 102M05_GHOS1557_01_SE_C05.indd 102 4/29/11 5:06 PM4/29/11 5:06 PM

Processor Basics 103

memory oriented (e.g., Motorola 6800) offers lesser number of internal registers as it expects the data or

operands would mainly be stored and manipulated within the read/write memory (RAM) of the system.

On the other hand, some processors are register oriented (e.g., Zilog Z80), which offers a larger number

of internal registers for the user. It may be noted that the program execution time for a processor would

be less if the data are available within itself rather than looking outside for them. However, more inter-

nal registers means more complexity in instruction decoding as each register would demand a separate

instruction to be provided by the instruction set of the processor.

So far, we have been discussing about the general purpose registers. However, other types of registers

are also available within the processors. They are accumulator or result register, status register, stack

pointer, program counter, interrupt register and so on. Most of these registers, in most processors, would

be user accessible. Apart from these, there are some registers that are purely for processor’s own use, e.g.,

temporary registers. We shall now have a brief discussion about some of these special purpose registers.

5.4.1 Status Register

Every processor performs some arithmetic or logical operations generating some results. Depending

upon whether the result is zero or negative or produced a carry or odd/even parity, some additional

actions might have to be taken by the programmer. Status register solves this problem by offering the

result status of the last performed arithmetic or logical operation through its pre-assigned bits. Gener-

ally, each bit of this status register is assigned for one particular indication, e.g., carry, parity, zero,

over ow and so on. These bits act as ags and their conditions (true or false) help the program to decide

further course of actions and dictate the conditional program branching.

Figure 5.9 Modified flowchart for simplified instruction cycle

M05_GHOS1557_01_SE_C05.indd 103M05_GHOS1557_01_SE_C05.indd 103 4/29/11 5:06 PM4/29/11 5:06 PM

..................Content has been hidden....................

You can't read the all page of ebook, please click here login for view all page.