138 Computer Architecture and Organization

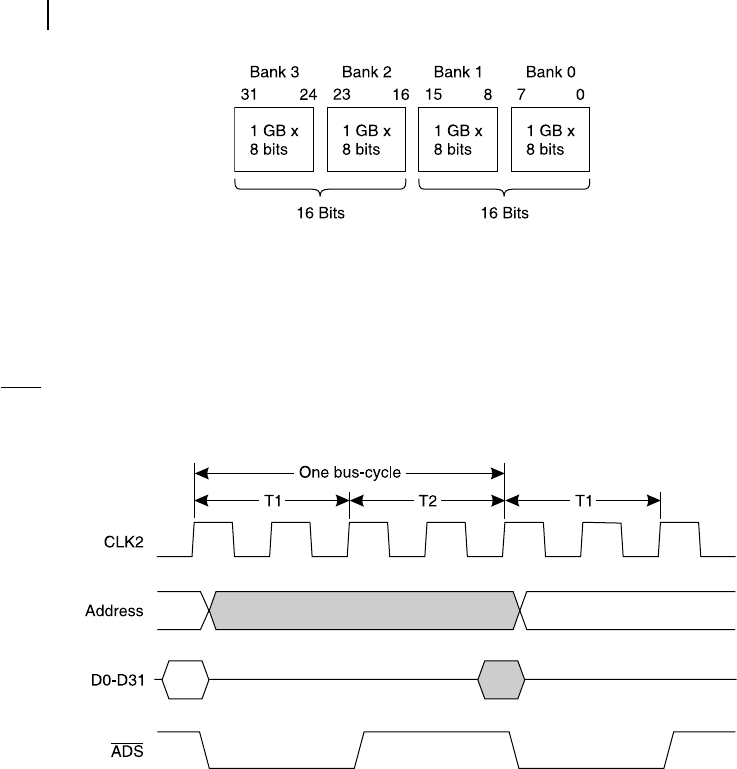

Any bus-cycle of 80386 must have two T-states, T1 and T2, if no wait-states are involved. By the

term bus-cycle, the time required to transact a byte or word (as per the available width of data bus) to or

from memory or I/O is indicated. The address remains valid throughout the bus-cycle, as shown by the

shaded area in Figure 5.36 and the related data transaction is also shaded in the same diagram. Note that

ADS output remains low during the rst half of the bus-cycle indicating the output to be an address and

goes high during the second half of the bus-cycle indicating the data communication.

Figure 5.35 Memory banks of 80386 processor

Figure 5.36 Timing diagram for 80386 (Non-pipelined read operation)

5.11.5 Special Features

Intel 80386 was the rst Intel processor capable of multi-tasking, i.e., running more than one program at

the same time. It has a built-in self test (BIST) routine, which is capable of checking most of its internal

circuits during power-on reset, if it is necessary. It has a page directory and supports the paging system.

External cache was introduced for the rst time in Intel 80386 processor.

5.12 INTEL PENTIUM 4 PROCESSOR

After the introduction of 80186, 80286, 80386 and 80486, the logical conclusion for the numbering

sequence might have been 80586. However, as it was not possible to own the trademark of any number,

Intel decided to introduce a new scheme of designating the next processor, which became famous as

Pentium (Pente = ve). With further improvements, we obtained processors similar to Pentium Pro,

M05_GHOS1557_01_SE_C05.indd 138M05_GHOS1557_01_SE_C05.indd 138 4/29/11 5:07 PM4/29/11 5:07 PM

Processor Basics 139

Pentium II, Pentium III and Pentium 4. Note the change in suf x expressed from roman to arabic numeral

for the last case. In this section, we shall have a brief discussion about some of the salient features of

Pentium 4, popularly known as simply P4 . Before introducing other relevant details, let us look back and

observe the series of processors from Intel, starting from 4004. In Table 5.1 , all major processors of Intel

from 4004 till Pentium 4 and beyond are presented with some of their important fi rst-time features.

5.12.1 RISC-like CISC Design

As we all know, the silent revolution was initiated by 4004, the 4-bit processor designed to be used

in calculators and small control systems. Incidentally, some 4-bit processors are still being used by

industry for cost-effective solution for very small systems. Note the logical improvement from 4-bit

to 8-bit processor in 8008 with a leap in addressable memory size of 16K-bytes. Next improvement

was in the instruction set available in 8080, and the era of small computer started. The address-

able memory space also expanded to 64 kB. Further improvement was from the power supply side

introduced in 8085, which operated with a single +5V DC power supply. Note that during this era,

the market was ooded with microprocessors from nearly all manufacturers, however, only a few

survived at a later stage.

The demand of market initiated the design of 8086, the 16-bit processor with 1 MB addressable

memory space. As we have already discussed, many new features were introduced for the rst time in

Processor Year Memory Remarks

4004 1971 4 K nibbles First 4-bit microprocessor.

8008 1972 16 kB First 8-bit microprocessor

8080 1974 64 K Improved instruction set available till P4

8085 1976 64 K Last 8-bit microprocessor

8086 1978 1 M First 16-bit processor

80286 1982 16 M

80386 1985 4 GB First 32-bit processor

80486 1989 4 GB

Pentium 1993 4 GB Introduction of superscalar architecture

Pentium Pro 1995 64 GB 64-bit data bus

Pentium II 1997 64 GB MMX technology for multimedia

Pentium III 1999 64 GB Additional oating-point instructions

Pentium 4 2000 64 GB Last of the Pentium series

Itanium 2001 64 GB IA-64 architecture introduced

Xeon 2001 64 GB With additional cache memory

Itanium 2 2002 64 GB Enhanced features

Core 2 Duo 2006 64 GB Two cores in one die

Dual Core 2007 64 GB Two Pentium CPUs in one die

Core i7 2009 64 GB Hyper threading included

Table 5.1 Intel Processors

M05_GHOS1557_01_SE_C05.indd 139M05_GHOS1557_01_SE_C05.indd 139 4/29/11 5:07 PM4/29/11 5:07 PM

140 Computer Architecture and Organization

8086, which existed till Pentium 4. Note that the direction of growth and improvement were more or

less xed by that time, and the essential targets were

R Faster processing speed

R More addressable memory size

R Greater processing power for number crunching.

These targets are still valid and after 8086, we nd 80386, the 32-bit processor with the concept of

cache. Internal cache was introduced for the rst time in the next processor, 80486 and by that time the

addressable memory area was enhanced to 4 GB.

After 80486, we nd the introduction of superscalar architecture in Pentium. We shall discuss its

details in Chapter 13. However, it may be mentioned here that superscalar architecture allows a pro-

cessor to execute more than one instruction in parallel. This not only allows faster execution but also

makes multi-user multi-tasking easier. GUI and video graphics demands have risen, during this period,

to initiate the introduction of MMX technology through Pentium II. With the introduction of Pentium

4, a long series, starting from 8080 dealing with backward compatibility, ended, which was one of the

reasons for the phenomenal success of these processor-series from Intel.

Intel introduced a brand name ‘Xeon’ during 1998, which included Pentium II, III and so on. How-

ever, from 2001, Xeon became an individual brand of CPUs aimed basically for embedded systems and

non-consumer workstations and servers market. Incidentally, Xeon was selected to be adopted in Apple

Mac pro workstation (announced in March 2009).

Intel introduced I-64 microarchitecture with Itanium and then introduced the NetBurst microar-

chitecture, after which it started the ‘ Core ’ microarchitecture, which was nally changed to Nehalem

microarchitecture. Before I-64, the microarchitectures might be designated as I-32. Finally, it may be

mentioned that each of the processor from Intel offers various variations related to operating speed,

cache memory and other features.

The above discussion is necessary to highlight one important feature of Pentium-series proces-

sors, in general, and Pentium 4, in particular. From the days of 8080, the trend of Intel proces-

sors was similar to CISC architecture. By comparing the instruction sets of 8085 and 8086, it may

be clear to the reader that the processor design stressed on incorporating complex instruction sets

to ease the development of software and specially the related operating system. However, after

the introduction of 8086, the popularity and ef ciency of RISC architecture became evident to the

designers. In successive processors, especially from the Pentium series, Intel incorporated some

major characteristics of RISC architecture within its CISC processors, thus creating RISC-like CISC

architecture . These are visible through the following characteristics of Intel processors, starting

from 8086 till Pentium 4:

R Pipeline architecture

R Cache memory (L1, L2 and L3)

R Larger set of internal registers

R Superscalar architecture.

A study of Table 5.1 would reveal that Intel processors till Pentium 4 were aimed for providing compre-

hensive set of instructions together with many basic features of RISC architecture. However, in the case

of IA-64 architecture introduced through Itanium series, the genuine RISC architecture was adopted by

Intel. We shall discuss more about it in Chapter 12.

M05_GHOS1557_01_SE_C05.indd 140M05_GHOS1557_01_SE_C05.indd 140 4/29/11 5:07 PM4/29/11 5:07 PM

Processor Basics 141

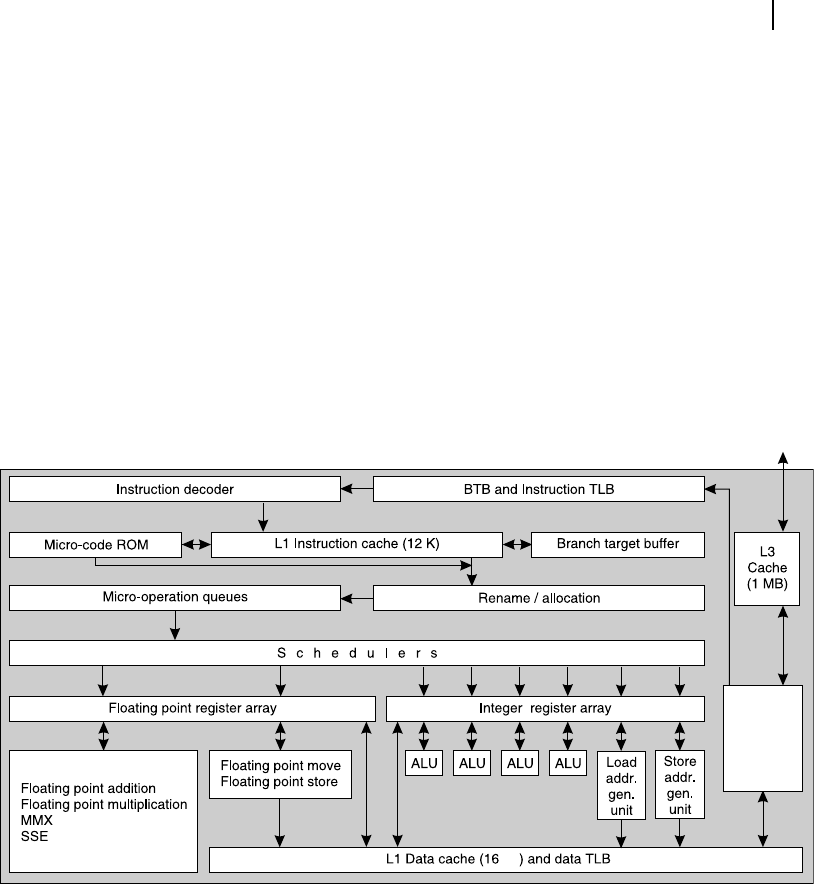

Figure 5.37 Simplified internal architecture of Pentium 4

L2

Cache

(512 kB)

and

control

From/to system interface

kB

5.12.2 Internal Architecture

There are several versions of Pentium 4 available in the market and two popular versions contain

478 pins and 423 pins through PGA package. Interested readers may consult manufacturer’s data

sheets for individual signal details and pin descriptions. All Pentium 4 versions offer 32 address

lines and 64 data lines (without any multiplexing) to directly address 64 GB of memory. A simpli-

ed version of internal architecture of Pentium 4 is presented in Figure 5.37 . As compared with

80386, there are several new features included in Pentium 4, which we shall discuss in the follow-

ing sections.

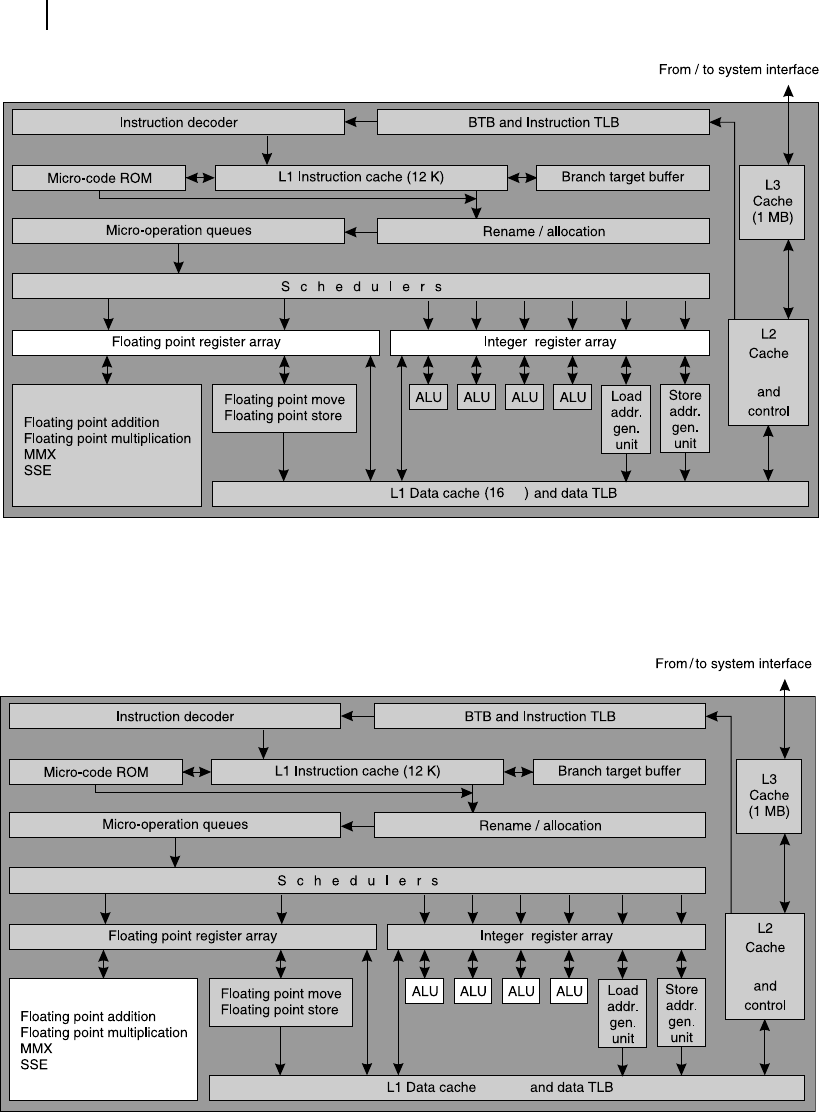

It was already pointed out that superscalar architecture (Chapter 13 for further details) was adopted

in the case of Pentium 4. In other words, multiple instructions may be concurrently executed by the

processor in real-time basis. To achieve this, there are two sets of registers within Pentium 4, one for the

integer operations and another for the oating-point operations. These two register arrays are indicated

in Figure 5.38 .

By carefully allocating these register sets for individual operations, Pentium 4 is capable of

simultaneously executing integer as well as floating-point operations with the help of dedicated

ALUs, as shown in Figure 5.39 . Note that for integer operations there are four ALUs, which are

capable of functioning independently and thus help in avoiding the structural hazards (Chapter

12 for further details). The floating-point ALU is capable of addition, multiplication and divi-

sion with floating-point numbers in single stage, as the data bus and register-width are always

of 64-bit. Apart from this feature, the related operations pertaining to MMX are also supported

by this unit.

M05_GHOS1557_01_SE_C05.indd 141M05_GHOS1557_01_SE_C05.indd 141 4/29/11 5:07 PM4/29/11 5:07 PM

142 Computer Architecture and Organization

(16 kB)

(512 kB)

Figure 5.39 Multiple ALU of Pentium 4

Figure 5.38 Two different register array of Pentium 4

(512 kB)

kB

M05_GHOS1557_01_SE_C05.indd 142M05_GHOS1557_01_SE_C05.indd 142 4/29/11 5:07 PM4/29/11 5:07 PM

..................Content has been hidden....................

You can't read the all page of ebook, please click here login for view all page.