152 Computer Architecture and Organization

6.3 FUNCTIONS AND CHARACTERISTICS

OF INSTRUCTIONS

It was already mentioned that the instructions directly executable by any processor are very primitive in

nature. In general, they are as simple as: ‘copy a byte from here to there’ or ‘add contents of these two

registers’, or something similar to these. It was also indicated that the instruction set of any processor

depends completely on the architecture of that processor. Why is it so? This is because the architecture

is developed from the instruction set as one of its guiding parameter. For example, a multiply instruc-

tion would be ineffective for a processor without a multiplying module. Or to put it in other way, if

the multiply instruction has to be included within the instruction set of the processor, there must be a

multiplication-module within the processor as one of its architectural feature.

In a generalized manner, instructions offered by any processor may be placed in three main catego-

ries (there may be more sub-categories), as follows:

R Data move type instructions

R Arithmetic and logical instructions and

R Program ow control and machine control instructions.

We may include a fourth category, indicating miscellaneous instructions, although it is not essential.

Some of the important characteristics of these three categories of instructions are discussed below.

6.3.1 Data Move Type

These instructions are most frequently used to copy data from one place to another. The source and

destination of movements may be registers within the processor or some external memory locations or a

combination of both. Immediate data, presented as a part of the instruction, may also be loaded to some

destination de ned by these instructions. The method by which any data are targeted is known as its

addressing mode , which we shall discuss in details. It may be noted here that status ags of processors

generally remain unaffected by the data move type instructions.

When the data are transacted between external memory and registers, external data bus is used.

However, during internal communications, internal bus of the processor takes the responsibility of com-

munication. There is no reason to take it for granted that the width of external and internal data bus of

a processor would be identical. For example, Intel 8088 (used as the processor of rst IBM PC) had

an external data bus of 8-bit while its internal data bus was 16-bit. However, the time required for data

transaction using external data bus (data between memory and registers) would always be more than the

time necessary for transactions using only internal bus (register to register).

This is one of the major points that forced the implementation of RISC architecture, offering

larger number of internal registers within the processor to minimize the memory to register

data transaction, and thereafter making the processor to work faster. If due to technological

advancement this difference of access time is eliminated, a major advantage of RISC

architecture would also be non-existent.

F

O

O

D

F

O

R

T

H

O

U

G

H

T

M06_GHOS1557_01_SE_C06.indd 152M06_GHOS1557_01_SE_C06.indd 152 4/30/11 2:55 PM4/30/11 2:55 PM

Instruction Set and Assembly Language Programming 153

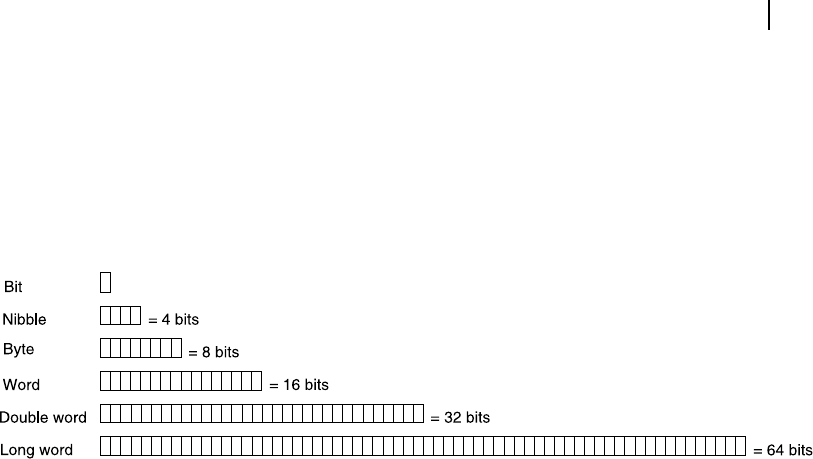

The data type, permitted by the processor, may vary widely, depending upon the processor. Some allow

8 and 16 bits of data. Others may allow 8, 16 and 32 bits of data. In some processors, even 1 bit of data

may be handled alongwith 8 or 16-bit data. There are some processors allowing 4-bit of data handling.

The bit-wise nomenclature of data is presented in Figure 6.1 . We have already indicated in Chapter 3 that

bit is the smallest storage cell, generally a ip- op, which can store either 1 or 0 in electrical form. Note

that the term ‘word’ is also used to denote the general number of bits used by the processor. For example,

a 32-bit processor might be referred as accommodating instruction set of word length of 32-bit. However,

the de nitions of bit, nibble, and byte remain unchanged and are not controversial (so far).

Figure 6.1 Bit-wise designation of data

Some special type of data transfer instructions are always present in all processors, related with

some special memory segment. For example, PUSH and POP instructions are always related with data

movements in connection with system stack area, pointed by the stack pointer. Finally, it is not true that

all internal registers of a processor may be accessed by data transfer instructions. For example, the pro-

gram counter register of 8051 cannot be accessed by any instruction directly, to read its value. However,

instructions are available in 8051 instruction set to reload its program counter by some speci c data.

6.3.2 Arithmetic and Logical Type

This group of instructions of any processor is responsible for number crunching. As we shall observe,

most processors offer instructions for four basic arithmetic operations (add, subtract, multiply and divide)

with signed and unsigned integers and essential logical operations, e.g., AND, OR, XOR, NOT, with shift

and rotate instructions. In Chapter 4, we have discussed about the representation of various types of data.

Using these instructions all types of data manipulations become possible for any processor.

For BCD arithmetic, some processors offer special instructions like decimal adjust . As most of the

need would be on decimal number processing, this type of instruction helps the program to quickly

solve the problem of BCD manipulation using binary representation.

In case of data move operations, the condition ags of the processor generally remain unaffected.

However, in general, arithmetic and many logical operations re ect their results’ conditions through

different ags, for further processing and for deciding the program- ow.

6.3.3 Program Flow Control Type

Program ow control instructions form the third major group of processor instructions. Generally, they

are sub-divided as conditional and unconditional branching and subroutine call and return. As indicated

earlier, it is the status of processor ags that decides the conditional branching. Depending upon the

processor, there may be very few or very large number of branching instructions.

M06_GHOS1557_01_SE_C06.indd 153M06_GHOS1557_01_SE_C06.indd 153 4/29/11 5:09 PM4/29/11 5:09 PM

154 Computer Architecture and Organization

Carry and zero are most widely used branching conditions. Instructions related with branching as

per the condition of carry ag or zero condition are offered by all processors. Next widely used branch-

ing instruction depends upon the comparison of two numbers (that is greater than or less than condi-

tion). Instructions pertaining to comparison are also offered by all processors (in some form or other).

Subroutines form major modules of any standard program and are extremely useful for software

developers. Therefore, subroutine call and return instructions are also a must for any processor’s

instruction set. Generally, a special return instruction is included in this case for returning from inter-

rupt service routines (ISR).

Although some minor details vary from processor to processor, the general form of these instructions

are more or less identical. In the following Tables (from Table 6.1 to Table 6.4 ) a general form of these

instructions are presented group-wise. Note that all instructions may not be available within all processors.

Instruction Function

Copy Copy data from register to register

Load Load data from memory to register.

Load immediate data in register

Store Save data from register to memory

Clear Load register by 0s

Set Load register by 1s

Exchange Exchange data between two registers or between a register and a memory location

Push Save data on stack-top indicated by stack pointer

Pop Load data from stack-top into register

Input Read data from input port and store within indicated register

Output Write data from indicated register into output port

Table 6.1 Common data transfer type instructions for processors

Instruction Function

Add Add two operands

Add with carry Add two operands and content of carry ag

Subtract Subtract one operand from another

Subtract with carry Subtract one operand from another along with carry

Multiply unsigned Unsigned multiplication of two operands

Multiply signed Signed multiplication of two operands

Divide unsigned Unsigned division of two operands

Divide signed Signed division of two operands

Increment by one Increment an operand by one. Generally used for address manipulations.

Decrement by one Decrement an operand bby one. Generally used for address manipulations.

Table 6.2 Common arithmetic type instructions for processors

M06_GHOS1557_01_SE_C06.indd 154M06_GHOS1557_01_SE_C06.indd 154 4/29/11 5:09 PM4/29/11 5:09 PM

..................Content has been hidden....................

You can't read the all page of ebook, please click here login for view all page.