Instruction Set and Assembly Language Programming 155

Instruction Function

AND Logically AND two operands

OR Logically OR two operands

XOR Logically XOR two operands

NOT Complement the operand

Shift right Shift operand right one bit. LSB is lost. New constant introduced at MSB.

Shift left Shift operand left one bit. MSB is lost. New constant introduced at LSB.

Rotate right Shift operand right one bit. LSB is shifted to MSB.

Rotate left Shift operand left one bit. MSB is shifted to LSB.

Compare Compare two operands and re ect the result through ags

Test Test ag bit(s)

Table 6.3 Common logical type instructions for processors

Instruction Function

Branch unconditional Jump to the indicated address

Branch conditional Test condition and if condition is true then jump to indicated address

Call a subroutine Save PC on stack-top and branch to indicated address

Return from subroutine Reload PC by address saved on stack-top

Return from interrupt Enable interrupts and reload PC from stack-top

No operation Do nothing

Wait Wait for a signal input

Halt Stop functioning of the processor

Skip next instruction Execute the instruction immediately after the next instruction

Branch relative to PC Add PC with an offset and branch there

Table 6.4 Common program flow control type instructions for processors

6.4 ADDRESSING MODES

Addressing modes are generally related with data transfer type instructions and indicates the method by

which the data are targeted by the instruction. For example, we need to load a set of data in a register.

However, the concerned data might be a part of the instruction itself or it might be already available

at some external memory address or within an internal register of the processor. Depending upon the

method by which it is located, it would be the addressing mode of that instruction that loads that data

in the register. The following are some of the widely used addressing modes by different processors:

R Immediate

R Direct

R Register direct

M06_GHOS1557_01_SE_C06.indd 155M06_GHOS1557_01_SE_C06.indd 155 4/29/11 5:09 PM4/29/11 5:09 PM

156 Computer Architecture and Organization

R Register indirect

R Relative

R Implicit

R Indexed

Brief discussions of these modes are presented below. Remember that all addressing modes are not

offered through all processors. Moreover, maximizing the number of addressing modes would make the

instruction decoding procedure of the processor more complex. It is on account of this reason for RISC

processors to offer lesser number of addressing modes.

6.4.1 Immediate

In an immediate addressing mode, the target data are a part of the instruction. As it is so, to change the

data, the instruction itself has to be changed. That is the reason for which the immediate addressing

mode is referred to as loading a ‘ constant ’. Depending upon the processor, these data might be integers

(unsigned or signed) or real. An example of immediate addressing mode instruction for 8085 processor

may be

LXI H, 1234H,

which loads the register pair HL by 16-bit data 1234H.

The student should note that addressing mode is not applicable for all instructions. For

example, the NOP (no operation) instruction can not have any addressing mode as it has noth-

ing to do with any data, either loading or storing it. Addressing modes are important for the

instruction set architecture level and particularly for instruction decoding. However, ‘every

instruction of a processor must be having an addressing mode’ is a false notion.

F

O

O

D

F

O

R

T

H

O

U

G

H

T

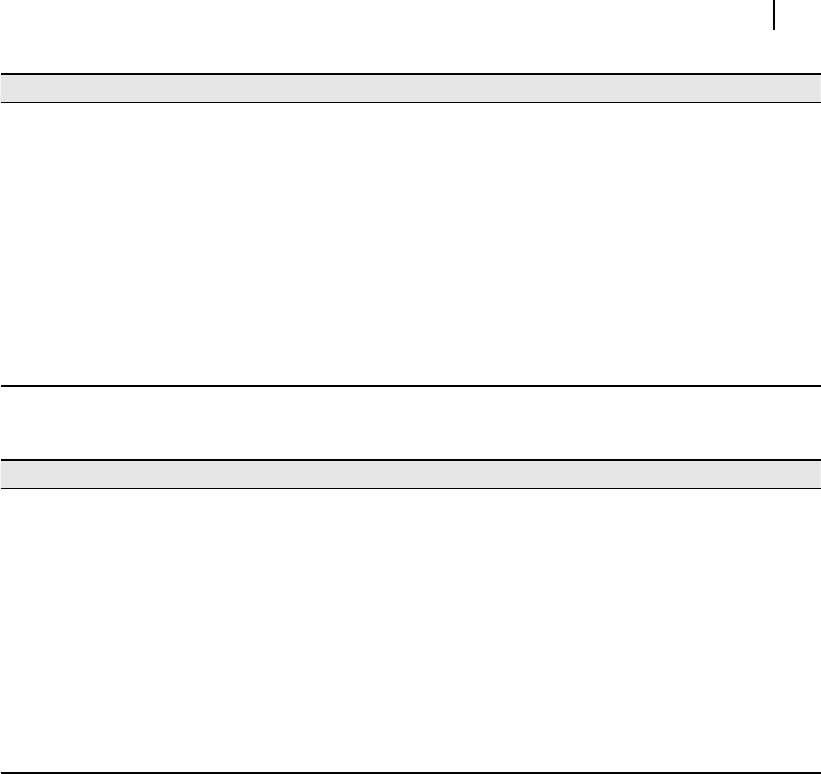

Figure 6.2 Example of immediate addressing mode

M06_GHOS1557_01_SE_C06.indd 156M06_GHOS1557_01_SE_C06.indd 156 4/29/11 5:09 PM4/29/11 5:09 PM

Instruction Set and Assembly Language Programming 157

Figure 6.2 illustrates the immediate addressing mode using an imaginary processor as an example

case. In this case, the instruction Load R1 by immediate data is executed by loading R1 by the data,

which is a part of the instruction itself.

6.4.2 Direct

In a direct addressing mode the target data’s location or the present address of data becomes a part of the

instruction. In other words, the data we are interested about are already available in a memory location

and the address of that memory location is already known to us. In the data loading instruction, we refer

that address and the processor, during execution of the instruction, retrieves that data from the known

address and places it at a proper place, as intended. In majority of cases, this type of data would be vari-

ables, as we may store or change the data located within that known address. Using 8085 instruction set,

an example of direct addressing mode would be

LDA 1234H,

which loads the accumulator directly from the content of the memory location whose address is 1234H.

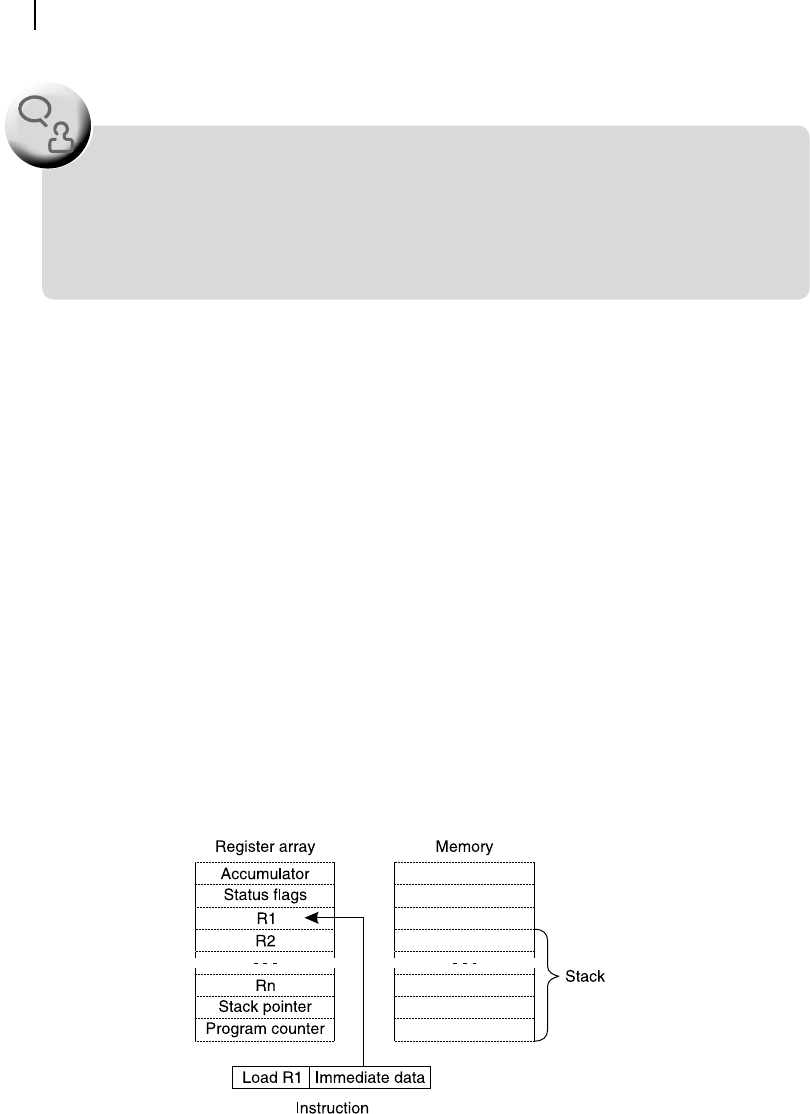

Figure 6.3 Example of direct addressing mode

Figure 6.3 illustrates the direct addressing mode, where the address of the data is shown as a part

of the instruction itself. According to the instruction, the processor copies the content of the addressed

location to the destination register, which is R1 in this case.

6.4.3 Register Direct

In register direct addressing mode, the name of the register, bearing or holding the target data, is indi-

cated in the instruction. In general these instructions are shortest in length as they need not contain a

complete address or complete data, necessary in direct and immediate addressing modes respectively.

However, in case of those processors, which offers multiple register banks with identical register names,

proper bank must be selected before implementing such instructions. An example of register direct

addressing mode from 8085 instruction set may be

MOV A, C,

which would copy the data from register C to the accumulator.

For some processors, three registers are used in the register direct addressing mode. The third regis-

ter in that case is indicated to hold the result. For example, we need to add two integers present in two

M06_GHOS1557_01_SE_C06.indd 157M06_GHOS1557_01_SE_C06.indd 157 4/29/11 5:09 PM4/29/11 5:09 PM

158 Computer Architecture and Organization

registers and place the result in a third register. Names of all three registers would be indicated by the

instruction in such a situation. However, this facility is not available in all processors.

Register direct addressing mode is illustrated in Figure 6.5 , where the source and destination regis-

ters are indicated for the data-copy operation. In this case, the accumulator is considered as the source

of data to be copied to the general purpose register R1.

6.4.4 Register Indirect

In register indirect addressing mode, also, the instruction indicates a register’s name. However, unlike

the previous case, the indicated register holds the address of the target data. Instead of providing the

complete address of the data (as done in direct addressing mode), indicating just the name of the reg-

ister that holds that address makes the length of the instruction shorter. An example of register indirect

addressing mode for 8085 instruction set may be

MOV A, M.

Execution of this instruction would load the accumulator from the memory location whose address is

available in register pair HL of the processor.

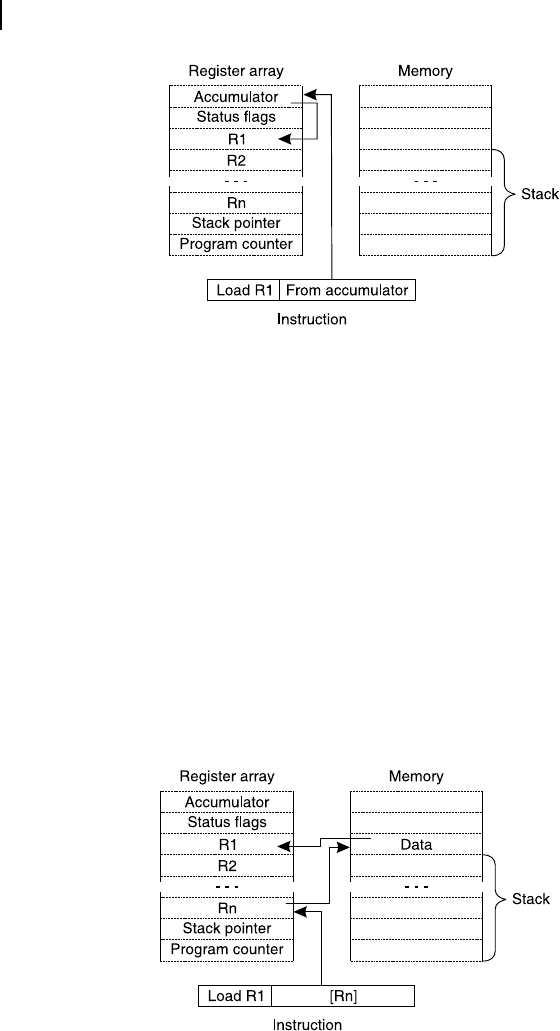

Figure 6.4 Example of register direct addressing mode

Figure 6.5 Example of register indirect addressing mode

In Figure 6.6 , an example of register indirect addressing mode is illustrated, where it is assumed that

the register R

n

is capable of holding the address of the source data. During the execution of the instruc-

tion, the data available within the address as indicated by the content of Rn are copied into R1.

M06_GHOS1557_01_SE_C06.indd 158M06_GHOS1557_01_SE_C06.indd 158 4/29/11 5:09 PM4/29/11 5:09 PM

Instruction Set and Assembly Language Programming 159

6.4.5 Relative

In relative addressing mode the location of target data is speci ed with respect to the current position

of the program counter (PC). In other words, the instruction would be similar to, e.g., nd the data after

20 bytes from now. Here, now means present content of PC. Generally, this type of addressing mode is

used for a table look up in a suitable subroutine.

An example of relative addressing mode is illustrated in Figure 6.6 , where the instruction indicates

to load a byte of data into register R1. The location of the data is expressed in relative addressing mode,

which, in this example case, is seven locations away from the current value of the program counter

of the processor. Therefore, to get the data, the current value of PC is incremented by 7 (PC remains

unchanged) and the resultant location is used as the source of the data to be copied to R1.

Figure 6.6 Example of relative addressing mode

The relative addressing mode offers one advantage. Even when the address of the program is

changed, it would still correctly nd the data out as the location of data is expressed as an offset of the

current value of PC. Relative addressing mode is used extensively in conditional jump instructions of

8051. However, it is not used in 8085 instruction set.

6.4.6 Implicit

In implicit addressing mode, the location of data is not indicated in the instruction because, for the implicit

instruction, the location of data is prede ned. For example, an imaginary processor might offer an instruction

CLEAR, which is applicable only for the accumulator of that processor. Whenever the accumulator has to be

loaded with 0s, this CLEAR instruction may be used. As we see, no operand is indicated in the instruction

as the name of the accumulator is implied and no other location would be cleared by this instruction. Widely

used instruction RETURN (or RET in some cases) falls under this category. In this case, it is implied to get

the relevant data (to be used as return address) from the stack top as pointed by the stack pointer (SP).

Another frequently used instruction using implicit addressing mode is POP, i.e., to restore a data

from stack-top to some indicated location. The source of data to be POPed is implicitly indicated as the

present stack-top location. This is illustrated through Figure 6.7 by the instruction POP R1. According

to the instruction, the data are located with the help of the stack pointer (SP) at the stack-top and then

M06_GHOS1557_01_SE_C06.indd 159M06_GHOS1557_01_SE_C06.indd 159 4/29/11 5:09 PM4/29/11 5:09 PM

..................Content has been hidden....................

You can't read the all page of ebook, please click here login for view all page.