3

BJT Circuits

Figure 3.1 Classification of transistors.

Transistor stands for ‘transfer’ + ‘resistor’, meaning that the basic operation of a transistor is to transfer an input signal from a resistor to another resistor. Transistors are broadly classified into two groups, i.e. Bipolar Junction Transistors (BJTs) and Field Effect Transistors (FETs). The two groups of transistors are further classified as depicted in Figure 3.1.

3.1 BJT (Bipolar Junction Transistor)

The (NPN/PNP) BJT is a three‐terminal device formed from two P‐N junctions (like diodes) which share a common (P/N‐type) semiconductor and is widely used for various purposes including amplification and switching.

3.1.1 Ebers‐Moll Representation of BJT

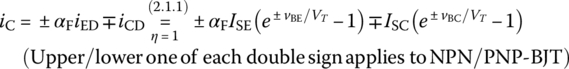

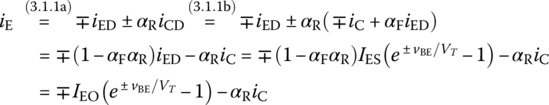

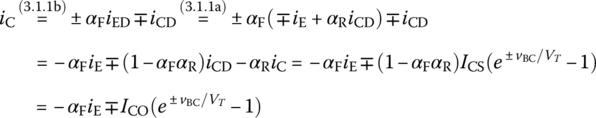

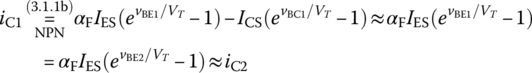

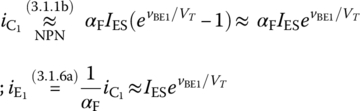

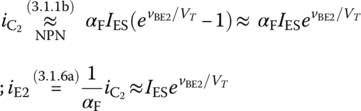

Figure 3.2(a1)/(a2), (b1)/(b2), and (c1)/(c2) shows the symbols, the basic structures, and the Ebers‐Moll models for NPN/PNP types of BJT, respectively. According to the Ebers‐Moll models, the emitter and collector currents of NPN/PNP‐BJTs are described as

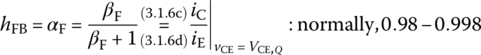

where the typical values of ISE (reverse saturation current of B‐E junction) and ISC = αFISE/αR (reverse saturation current of B‐C junction) are in the order of 10−15∼10−12 and those of αF and αR are as follows:

Note that the forward and reverse saturation leakage currents are the same as each other and the transistor saturation current IS:

Figure 3.2 Symbols, basic structures, and models for NPN/PNP‐type Bipolar Junction Transistors (BJTs).

We can use these equations to write the relations between the emitter current iE and the collector current iC as

where IEO = (1 − αFαR)ISE/ICO = (1 − αFαR)ISC is the reverse emitter/collector current, which flows through the B‐E/B‐C junction when the junction is highly reverse biased and the collector/emitter terminal is open so that iC = 0/iE = 0, respectively.

Also, we can apply Kirchhoff's Current Law (KCL) to the BJT or the closed surface including its three terminals to write

Noting that the reverse emitter/collector currents IEO/ICO are negligibly small, the relationships among the three currents iC, iE, and iB of NPN‐BJT with vBE ≥ 0.7 (forward biased) and vBC < 0.4 (not forward biased enough) can be written as

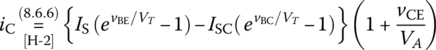

According to [H-2], the collector and base currents of an NPN‐BJT can be expressed as

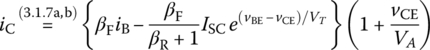

where IS = αFIES, ISC = IS/αR (typically within 10IS), and VA is the Early voltage, whose typical value is 10∼100 V. Here, compared with Eq. (3.1.1), the additional term proportional to vCE/VA has been included to account for the Early effect (also called the base‐width modulation effect) that IS increases as increasing vCE results in a decrease in the effective base width of BJT. Noting that based on these equations, the collector current iC can be expressed in terms of vCE, vBE, and iB as

we can run the following MATLAB script “plot_iC_vs_vCE.m” to plot iC versus vCE (with vBE = 0.7 V) for several values of iB as shown in Figure 3.3 where the (dotted) extrapolation of every iC curve intersects the vCE‐axis at common point vCE = −VA.

Figure 3.3 The iC‐vCE characteristic curves for different values of constant iB (with vBE = 0.7V).

3.1.2 Operation Modes (Regions) of BJT

Table 3.1 shows the four operation modes (regions) of NPN‐BJT(Si) determined by the bias conditions of B‐E and B‐C junctions. Note the following:

- When vBE = 0.7 V and vCE > 0.3 V so that vBC = vBE − vCE < 0.4, the BJT operates in the forward‐active region.

- vCE is 0.3 V at the edge of saturation and becomes vCE,sat = 0.2 V in the ‘deep’ saturation mode.

- In the forward‐active mode where vBC < 0.4, the first terms (proportional to IS) are dominant over the second terms (proportional to ISC) in Eqs. (3.1.7a) and (3.1.7b) so that iC ≈ βFiB.

- In the reverse‐active mode where vBC > 0.5, the second terms (proportional to ISC) are dominant over the first terms (proportional to IS) in Eqs. (3.1.7a) and (3.1.7b) so that iC ≈ −(βR + 1)iB. This corresponds to Eq. (3.1.6d) where the roles of the collector and emitter terminals have been switched.

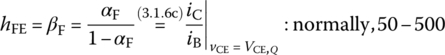

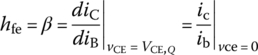

3.1.3 Parameters of BJT

To analyze BJT circuits, we need to define the following parameters for the forward‐/reverse‐active mode:

Table 3.1 Operation modes (regions) of NPN–BJT (Si) with VTD = 0.5 V.

| Operation mode | Forward‐active | Cut‐off | Saturation | Reverse‐active | |

| Bias condition | B‐E | Forward (vBE ≥ VTD) | Reverse (vBE < VTD) | Forward (vBE ≥ VTD) | Reverse (vBE < 0.4) |

| B‐C | Reverse (vBC < 0.4) | Reverse (vBC < 0) | Forward (vBC ≥ 0.4) | Forward (vBC ≥ VTD) | |

| Functions | Current‐controlled current source iC = −αFiE, vBE = 0.7 V | Open switch | Closed switch vBE = 0.7 V vCE = 0.2 V | Roles of E and C terminals switched iE = −αRiC | |

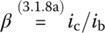

- Forward‐active mode

<CE (Common‐Emitter), forward large‐signal (DC) current gain>

(3.1.9a)

<CB (Common‐Base), forward large‐signal (DC) current gain>

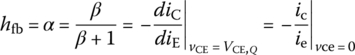

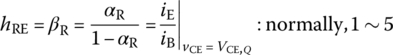

<CE (Common‐Emitter), forward small‐signal (AC or incremental) current gain>

(3.1.10a)

<CB (Common‐Base), forward small‐signal (AC or incremental) current gain>

(3.1.10b)

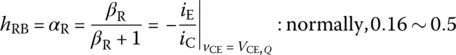

- Reverse‐active mode

<CE (Common‐Emitter), reverse large‐signal (DC) current gain>

(3.1.11a)

<CB (Common‐Base), reverse large‐signal (DC) current gain>

(3.1.11b)

3.1.4 Common‐Base Configuration

Figure 3.4(a) shows a common‐base (CB) NPN‐BJT circuit in which the input is applied to the BEJ (B‐E junction) and the output is available from the BCJ (B‐C junction) so that the base terminal is common between the input and the output. Note that since the BEJ/BCJ are forward/reverse biased, we can expect the BJT to operate in the forward‐active mode (Table 3.1). Also, note that since the BEJ and BCJ are nonlinear resistors, we may have to apply the load line analysis for both the B‐E loop and the B‐C loop.

To perform a comparatively exact analysis considering the nonlinearity of the circuit, we draw the load line on the B‐E characteristic curve (Figure 3.4(b)) where the load line equation can be obtained by applying KVL around the B‐E loop:

The intersection of the load line with the B‐E characteristic curve is the operating (bias) point QE:

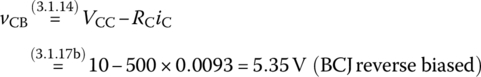

where it does not matter which one of many B‐E characteristic curves with different values of vCB is used to determine the operating point because B‐E characteristic curve varies little with vCB. Then we draw the load line on the B‐C characteristic curve (Figure 3.4(c)) where the load line equation can be obtained by applying KVL around the B‐C loop:

The intersection of the load line with the B‐C emitter characteristic curve for −iE = 9.3 mA gives the operating point QC:

To be strict, unless the B‐E characteristic curve varies little with vCB, we should relocate QC with the B‐E characteristic curve for vCB = 5.35 V and repeat the same process iteratively. Then this theoretical analysis becomes time‐consuming even for such a simple circuit. However, as a practical means, when the BEJ (B‐E junction) is surely forward biased, we often set the BEJ voltage as

Figure 3.4 A Common‐Base (CB) BJT circuit and related v‐i characteristic curves.

and instead of performing the load line analysis for the B‐E loop, use Eqs. (3.1.12), (3.1.6c), (3.1.9b), and (3.1.14) together with βF = 186 (BETADC from the PSpice simulation output file or databook) to obtain the following:

Now, to perform the PSpice simulation, we create an OrCAD/PSpice project named, say, “CB_BJT.opj,” compose the schematic as depicted in Figure 3.4(a), make a Simulation Settings dialog box (with Bias Point analysis type) as depicted in Figure 3.4(d), and run it to get the PSpice simulation output some part of which is shown in Figure 3.4(e). The Bias Point analysis result can also be made seen in the schematic (Figure 3.4(a)) by clicking on the ‘Enable Bias Voltage Display’ and ‘Enable Bias Current Display’ buttons in the tool bar above the Schematic Editor window.

3.1.5 Common‐Emitter Configuration

Figure 3.5(a) shows a common‐emitter (CE) NPN‐BJT circuit in which the input is applied to the BEJ (B‐E junction) and the output is available from the CEJ (C‐E junction) so that the emitter terminal is common between the input and the output. Note that we can expect the BJT to operate in the forward‐active mode since the BEJ/BCJ are forward/reverse biased (Table 3.1).

To perform a comparatively exact analysis considering the nonlinearity of the circuit, we do the following:

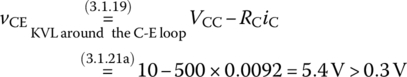

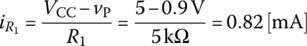

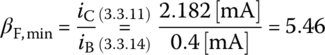

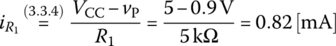

- Setting the BEJ voltage to vBE = 0.7 V, apply KVL around the B‐E loop to find the base current iB as

- Draw the load line on the C‐E characteristic curve(s) (Figure 3.5(b)) where the load line equation can be obtained by applying KVL around the C‐E loop:

Figure 3.5 A Common‐Emitter (CE) BJT circuit and related v‐i characteristic curves.

- The intersection of the load line with the C‐E characteristic curve for iB = 50 μA gives the operating point QCE:

(3.1.20)

Most often, as a more practical means instead of the load line analysis, we use Eqs. (3.1.6c), (3.1.18), and (3.1.19) together with βF = 184 (BETADC from the PSpice simulation output file or databook) to obtain the following:

Whichever of the graphical or analytical methods we may use, we need to check if vCE > 0.3 V so that the BJT will not enter the saturation mode. If vCE turned out to be not greater than 0.3 V, then we would have to set vCE = vCE,sat = 0.2 V and use Eq. (3.1.19) to find the collector current iC.

Now, to perform the PSpice simulation, we create an OrCAD/PSpice project named, say, “CE_BJT.opj,” compose the schematic as depicted in Figure 3.5(a), make a Simulation Settings dialog box (with Bias Point analysis type) as depicted in Figure 3.4(d), and run it to get the PSpice simulation result as shown in Figure 3.5(c), which is a part of the PSpice simulation output file that can be seen by selecting View>Output_File from the top menu bar. The Bias Point analysis result can also be made seen in the schematic (Figure 3.5(a)) by clicking on the ‘Enable Bias Voltage Display’ and ‘Enable Bias Current Display’ buttons in the tool bar above the Schematic Editor window.

3.1.6 Large‐Signal (DC) Model of BJT

Figure 3.6(a)/(b)/(c)/(d) shows the large‐signal (DC) models of an NPN‐BJT for the forward‐active/saturation/reverse‐active/cut‐off modes, respectively. Figure 3.7(a) shows a typical (DC driven) BJT biasing circuit. Figure 3.7(b)/(c)/(d) shows its equivalents with the BEJ biasing side replaced by its Thevenin equivalent and with the BJT replaced by its model in the forward‐active/saturation/reverse‐active mode, respectively.

Figure 3.6 Large‐signal models of NPN‐BJT in different operation modes (regions).

Figure 3.7 A BJT biasing circuit and its equivalents in different operation modes (regions) of BJT.

The above MATLAB function ‘BJT_DC_analysis()’ can be used to analyze NPN‐BJT biasing circuits (driven by DC sources) and find the values of VB,Q, VE,Q, VC,Q, IB,Q, IE,Q, and IC,Q (voltages/currents at/through the base, emitter, and collector terminals) at the operating point. Note the following about its usage:

- If the emitter terminal is connected (via RE) to another voltage source VEE, the first input argument should be a two‐dimensional vector [VCC VEE].

- If the base terminal is connected (via RB) to another voltage source VBB, the second and third input arguments should be VBB and RB, respectively.

Likewise, the above MATLAB function ‘BJT_PNP_DC_analysis()’ has been composed to analyze typical (DC driven) PNP‐BJT biasing circuits.

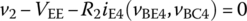

Instead of the (linear) large‐signal model as in Figure 3.6, the exponential model of an NPN‐BJT based on Eq. (3.1.7) (with VA = ∞ to exclude the Early effect) can be used to write KVL equations in vBE and vBC along the two paths VCC‐RC‐CBJ‐BEJ‐RE‐VEE and VCC‐RC‐CBJ‐RB‐VBB (for the NPN‐BJT circuit in Figure 3.8(a)) as

where

Also, KVL equations in vEB and vCB can be written along the two paths VEE‐RE‐EBJ‐BCJ‐RC‐VCC and VBB‐RB‐BCJ‐RC‐VCC (for the PNP‐BJT circuit in Figure 3.8(b)) as

where

Figure 3.8 NPN/PNP BJT biasing circuits and their i‐v relations.

The following MATLAB function ‘BJT_DC_analysis_exp()’ can be used to analyze an NPN‐BJT biasing circuit (based on the exponential model) and find the values of VB,Q, VE,Q, VC,Q, IB,Q, IE,Q, and IC,Q (voltages/currents at/through the base, emitter, and collector terminals) at the operating point. Note the following about ‘BJT_DC_analysis_exp()’:

- If you want to use it for analyzing a PNP‐BJT circuit, attach the minus sign to the sixth input argument

beta. - The sixth input argument

betais expected to be given as [±βF βR IS]. - In this ‘nonlinear’ approach, active‐or‐saturated is not clear‐cut but only a matter of degree.

Figure 3.9 A BJT circuit and its PSpice schematic for Example 3.1.

Figure 3.10 A BJT circuit, its equivalent, and their PSpice schematics for Example 3.2.

Figure 3.11 A BJT circuit and its PSpice schematic for Example 3.3.

Figure 3.12 A BJT circuit and its PSpice schematic for Example 3.4.

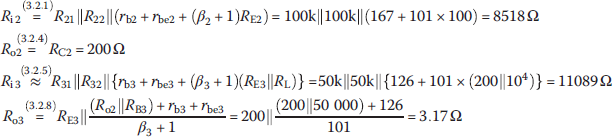

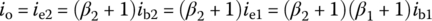

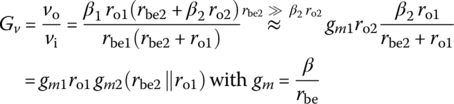

Example 3.8 Three‐BJT Circuit

Consider the three‐BJT circuit in Figure 3.16(a) where the device parameters of the BJTs Q1, Q2, and Q3 are βF = 100, βR = 1, and Is = 10−14 A in common.

- Analyze the circuit to find VE1, VC1, VE2, VC2, VE3, and VC3.

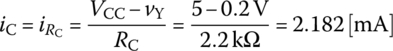

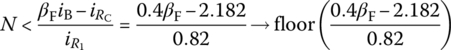

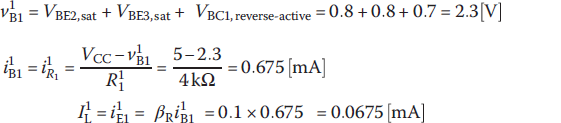

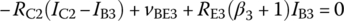

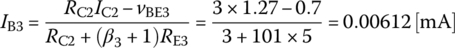

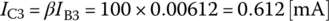

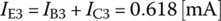

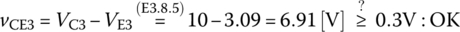

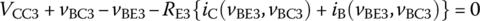

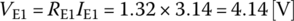

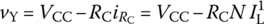

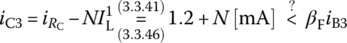

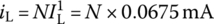

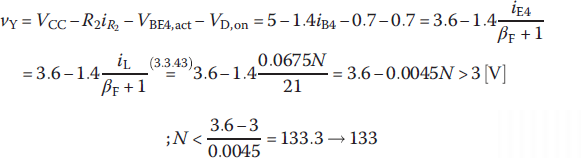

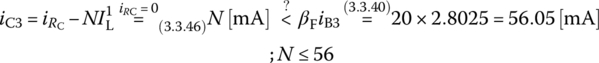

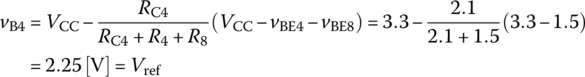

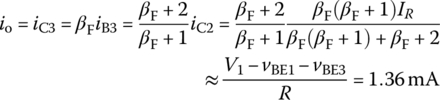

First, noting that the Q1‐Q2 part of the circuit is identical to the circuit of Figure 3.15(a), we copy all the analysis results of Example 3.7 except for VC2, because the current through RC2 decreases from IC2 by IB3. To find IB3, we assume that Q3 also operates in the forward‐active mode (with vBE3 = 0.7 V) and write the KVL equation (in IB3) along the path RC2‐vBE3‐RE3 as

Figure 3.16 A three‐BJT BJT circuit for Example 3.8.

(E3.8.1)

which can be solved for IB3 as

(E3.8.2)

Thus, we can find

(E3.8.3) (E3.8.4)

(E3.8.4) (E3.8.5)

(E3.8.5) (E3.8.6)

(E3.8.6)

Now we check if Q2 and Q3 operate in the forward‐active region:

(E3.8.7a) (E3.8.7b)

(E3.8.7b)

This implies that Q2 and Q3 operate in the forward‐active region.

- With the analysis result of the Q1/Q2 part obtained in Example 3.7, go on to use the MATLAB function ‘

BJT_DC_analysis()’ for the analysis of the Q3 part.Regarding Q3 as driven by the Thevenin equivalent consisting of VBB3 = VC20 = RC2IC2 (with Q3 unconnected) and RB3 = RC2, we run the following MATLAB statements for the analysis of the Q3 (NPN‐BJT) part:

>>VCC3=10; RC2=3e3; IC2=1.27e-03; % From the solution of Example 3.7VBB3=RC2*IC2; RB3=RC2; RC3=0; RE3=5e3; betaF=100; betaR=1;BJT_DC_analysis(VCC3,VBB3,RB3,RC3,RE3,[betaF betaR]);to get the following analysis result for the Q3 part:

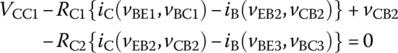

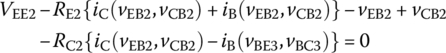

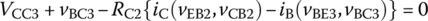

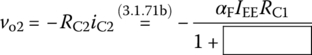

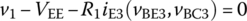

VCC VEE VBB VBQ VEQ VCQ IBQ IEQ ICQ10.00 0.00 3.81 3.79 3.09 10.00 6.12e-06 6.18e-04 6.12e-04in the forward-active mode with VCE,Q= 6.91[V],Alternatively, we can use the exponential model to set up the KVL equations (in vBE1, vBC1, vEB2, vCB2, vBE3, and vBC3) along the six paths VCC1‐RC1‐vCB1‐RB1‐VBB1, VBB1‐RB1‐vBE1‐RE1, VCC1‐RC1‐vBC2‐RC2, VEE2‐RE2‐vEB2‐vBC2‐RC2, VCC3‐vCB3‐RC2, and VCC3‐vCB3‐vBE3‐RE3 as

(E3.8.8a) (E3.8.8b)

(E3.8.8b) (E3.8.8c)

(E3.8.8c) (E3.8.8d)

(E3.8.8d) (E3.8.8e)

(E3.8.8e) (E3.8.8f)

(E3.8.8f)

This set of nonlinear equations in an unknown vector v = [vBE1 vBC1 vEB2 vCB2 vBE3 vBC3] can be solved by using the MATLAB function ‘

fsolve()’ as shown in the following script “elec03e08.m”:%elec03e08.mbetaF=100; betaR=1; alphaR=betaR/(betaR+1); Is=1e-14; Isc=Is/alphaR; VT=25e-3; % BJT parametersVCC1=10; VEE2=10; VCC3=10;R1=127e3; R2=127e3; RC1=1e3; RE1=1.5e3; RE2=1e3; RC2=3e3; RC3=0; RE3=5e3;VBB1=VCC1*R2/(R1+R2); RB1=parallel_comb([R1 R2]);% Exponential model based approachiC=@(v)Is*exp(v(1)/VT)-Isc*exp(v(2)/VT);iB=@(v)Is/betaF*exp(v(1)/VT)+Isc/(betaR+1)*exp(v(2)/VT);% Eq. (E3.8.8) with v=[vBE1 vBC1 vEB2 vCB2 vBE3 vBC3]eq=@(v)[VCC1-VBB1+v(2)-RC1*(iC(v(1:2))-iB(v(3:4)))+RB1*iB(v(1:2));VBB1-RB1*iB(v(1:2))-v(1)-RE1*(iC(v(1:2))+iB(v(1:2)));VCC1+v(4)-RC1*(iC(v(1:2))-iB(v(3:4)))– RC2*(iC(v(3:4))-iB(v(5:6)));VEE2-v(3)+v(4)-RE2*(iC(v(3:4))+iB(v(3:4)))−RC2*(iC(v(3:4))-iB(v(5:6)));VCC3+v(6)-RC2*(iC(v(3:4))-iB(v(5:6)));VCC3+v(6)-v(5)-RE3*(iC(v(5:6))+iB(v(5:6)))];options=optimset('Display','off','Diagnostics','off');v0 = [0.7; 0.4; 0.7; 0.4; 0.7; 0.4]; % Initial guess for vv = fsolve(eq,v0,options);VBE1=v(1), VBC1=v(2), VEB2=v(3), VCB2=v(4), VBE3=v(5), VBC3=v(6)IB1Q = iB(v(1:2)), IC1Q = iC(v(1:2))IB2Q = iB(v(3:4)), IC2Q = iC(v(3:4))IB3Q = iB(v(5:6)), IC3Q = iC(v(5:6))VC1Q = VCC1-RC1*(IC1Q-IB2Q), VB1Q=VC1Q+VBC1, VE1Q=VB1Q-VBE1VE2Q = VEE2-RE2*(IC2Q+IB2Q), VB2Q=VE2Q-VEB2, VC2Q=VB2Q+VCB2VC3Q = VCC3-RC3*IC3Q, VB3Q=VC3Q+VBC3, VE3Q=VB3Q-VBE3A part of the results obtained from running this script is as follows:

IC1Q=0.0020, IC2Q=0.0014, IC3Q=6.7745e-4VC1Q=VB2Q=7.9907, VB1Q=3.7155, VE1Q=3.0647VC2Q=VB3Q=4.0446, VE2Q=8.6315VC3Q=10, VE3Q=3.4211 - Use the PSpice software to simulate the circuit.

We draw the PSpice schematic (Figure 3.16(b)) where the device parameters of the NPN‐BJTs Q1, Q3 (QbreakN), and PNP‐BJT Q2 (QbreakP) have been set in the PSpice Model Editor window as shown in Figure 3.14(b2). The simulation results obtained by performing Bias Point analysis are shown in the schematic.

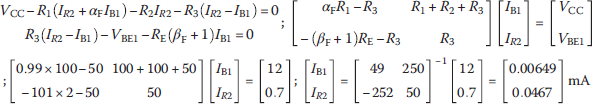

Example 3.9 Two‐BJT Circuit (in Saturation Mode)

Consider the two‐BJT circuit in Figure 3.17(a) where the device parameters of the BJTs Q1 and Q2 are βF = 100, βR = 1, and Is = 10−14 A in common.

- Analyze the circuit to find VE1, VC1, VE2, and VC2.

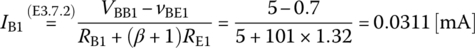

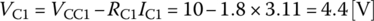

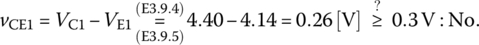

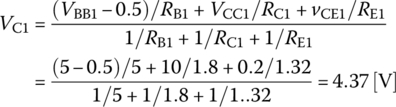

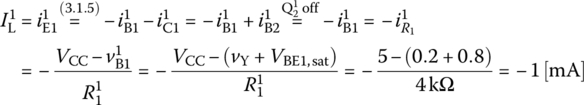

First, as done in Example 3.7, we assume that Q1 operates in the forward‐active region (with vBE1 = 0.7 V) and try to find IB1, IC1, IE1, VE1, VC1, etc. as

(E3.9.1) (E3.9.2,3)

(E3.9.2,3) (E3.9.4)

(E3.9.4) (E3.9.5)

(E3.9.5) (E3.9.6)

(E3.9.6)

Since this implies that Q1 may be in the saturation mode, we assume vCE1 = 0.2 V (referring to Example 3.6), write the KCL equation (in VC1) at Q1, and solve it to find

(E3.9.7)

where IB2 has been assumed to be small enough to make iRC1 ≈ IC1.

Figure 3.17 A two‐BJT BJT circuit for Example 3.9.

Although we can proceed further in this way to find VC2, why not use the MATLAB functions ‘

BJT_DC_analysis()’/‘BJT_PNP_DC_analysis()’ to analyze the Q1/Q2 part, respectively? As done in Example 3.7b, we run the following MATLAB statements:>>betaF=100; betaR=1; VCC1=10; VEE2=10;R1=10e3; R2=10e3; RC1=1.8e3; RE1=1.32e3; RE2=20e3; RC2=19.8e3;[VB1,VE1,VC1,IB1,IE1,IC1,mode1]=...BJT_DC_analysis(VCC1,R1,R2,RC1,RE1,[betaF betaR]);VBB2=VEE2-RC1*IC1; RB2=RC1;[VB2,VE2,VC2,IB2,IE2,IC2,mode2]=...BJT_PNP_DC_analysis(VEE2,VBB2,RB2,RE2,RC2,[betaF betaR]);to get

VCC VEE VBB VBQ VEQ VCQ IBQ IEQ ICQ10.00 0.00 5.00 4.87 4.17 4.37 2.67e-05 3.16e-03 3.13e-03in the saturation mode with VCE,Q= 0.20[V]VEE VCC VBB VBQ VEQ VCQ IBQ IEQ ICQ10.00 0.00 4.37 4.37 5.07 4.87 7.56e-07 2.47e-04 2.46e-04in the saturation mode with VEC,Q= 0.20[V]Alternatively, as done in Example 3.7b, we can use the exponential model to set up a set of KVL equations (in vBE1, vBC1, vEB2, and vCB2) and solve it by running the following MATLAB script:

%elec03e09.mclearbetaF=100; betaR=1; alphaR=betaR/(betaR+1);Is=1e-14; Isc=Is/alphaR; VT=25e-3; % BJT parametersVCC1=10; VEE2=10;R1=10e3; R2=10e3; RC1=1.8e3; RE1=1.32e3; RE2=20e3; RC2=19.8e3;VBB1=VCC1*R2/(R1+R2); RB1=parallel_comb([R1 R2]);iC = @(v)Is*exp(v(1)/VT)-Isc*exp(v(2)/VT);iB = @(v)Is/betaF*exp(v(1)/VT)+Isc/(betaR+1)*exp(v(2)/VT);eq=@(v)[VCC1-VBB1+v(2)-RC1*(iC(v(1:2))-iB(v(3:4)))+RB1*iB(v(1:2));VBB1-RB1*iB(v(1:2))-v(1)-RE1*(iC(v(1:2))+iB(v(1:2)));VCC1+v(4)-RC1*(iC(v(1:2))-iB(v(3:4)))-RC2*iC(v(3:4));VEE2-v(3)+v(4)-RE2*(iC(v(3:4))+iB(v(3:4)))-RC2*iC(v(3:4))];options=optimset('Display','off','Diagnostics','off');v0 = [0.7; 0.4; 0.7; 0.4]; %Initial guess for v=[vBE1 vBC1 vEB2 vCB2]v = fsolve(eq,v0,options);VBE1=v(1), VBC1=v(2), VEB2=v(3), VCB2=v(4)IB1Q = iB(v(1:2)), IC1Q = iC(v(1:2))IB2Q = iB(v(3:4)), IC2Q = iC(v(3:4))VC1Q=VCC1-RC1*(IC1Q-IB2Q), VB1Q=VC1Q+VBC1, VE1Q=VB1Q-VBE1VE2Q = VEE2-RE2*(IC2Q+IB2Q), VB2Q=VE2Q-VEB2, VC2Q=VB2Q+VCB2vCE1Q = VC1Q-VE1Q, vEC2Q = VE2Q-VC2Q

- A part of the results obtained from running this script is as follows:

IC1Q=0.0031, IC2Q=2.4564e-04VC1Q=VB2Q=4.3742, VB1Q=4.8377, VE1Q=4.1759, VE2Q=4.9730, VC2Q=4.8637vCE1Q = 0.1983, vEC2Q = 0.1093

- Use the PSpice software to simulate the circuit.

We draw the PSpice schematic as Figure 3.17(c) and perform the Bias Point analysis to get the simulation results shown in the schematic.

3.1.7 Small‐Signal (AC) Model of BJT

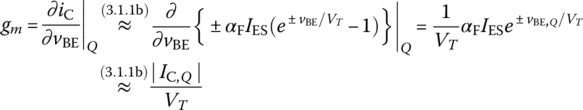

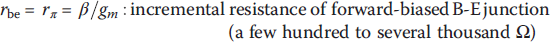

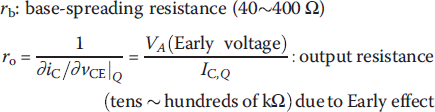

Figure 3.18(a)/(b) shows the high/low frequency small‐signal (AC) models of an NPN‐BJT for the forward‐active mode, respectively, where

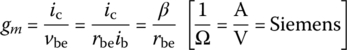

- gm: transconductance (gain)

(3.1.26)

(3.1.27)

(3.1.27)

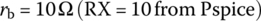

- rb: base‐spreading resistance (40∼400 Ω)

(3.1.28)

- rbc: incremental resistance of B‐C junction (several MΩ)

- Cbe (CD, Cπ, CJ E): diffusion capacitance of B‐ E junction (tens to hundreds of pF)

- Cbc (CT, Cμ, CJ

C): transition/depletion capacitance of reverse‐biased B‐

C junction (0.1∼100 pF)

Figure 3.18 Hybrid‐π small‐signal models of NPN‐BJT with or without frequency dependence.

- Note that compared with the high‐frequency model in Figure 3.18(a), the low‐frequency model in Figure 3.18(b) has no capacitance because the magnitudes of impedance or reactance of Cbe and Cbc are large enough to be regarded as virtually open:

- Note also that referring to the low‐frequency model in Figure 3.18(b), the transconductance, gm, is related with the CE, small‐signal (AC) current gain

as

(3.1.29)

as

(3.1.29)

3.1.8 Analysis of BJT Circuits

For the analysis of BJT circuits, the following three steps are taken where Table 3.2 shows the notations representing the DC/AC components and total solutions:

|

Table 3.2 Symbols representing DC and AC variables

| DC components at operating point Q | AC components | DC + AC components | |||

| Instantaneous values | r.m.s. values | Instantaneous values | r.m.s. values | ||

| Base current | IB,Q | ib | Ib | iB | IB |

| Voltage across C‐E junction | VCE,Q | vce | Vce | vCE | VCE |

To see how the above procedure can be applied, let us consider the BJT circuit in Figure 3.19.1(a) where the roles of the three capacitors are as follows:

- Cs is used for injecting (coupling) the AC input to the base terminal of the BJT and also for blocking the DC source to keep the bias conditions undisturbed.

- CL is used for extracting the AC output signal from the collector terminal of the BJT without disturbing the DC Q‐point.

- CE is used to make the AC signal bypass RE2 so that the emitter resistance should be regarded as RE1+RE2 for setting the DC bias conditions and RE1 for producing AC output signal.

Note that Cs and CL are called coupling or blocking capacitors while CE is called a bypass capacitor. Whatever they are called, all of the capacitors are commonly supposed to provide a very large/small impedance (or reactance XC = 1/ωC) for DC(ω = 0)/AC(ω > 0) signals like being virtually open (XC = ∞)/short(XC = 0)‐circuited where ω represents the frequency of the input signal.

Now, along the procedure listed in the above box, we take the following steps:

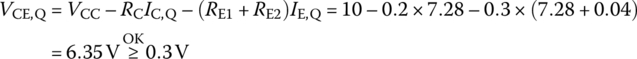

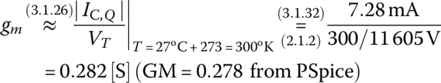

- DC Analysis

- Remove every AC source (by open/short‐circuiting current/voltage sources) and open/short‐circuit every capacitor/inductor to find the DC equivalent circuit as shown in Figure 3.19.1(b).

- Redraw Figure 3.19.1(b) as Figure 3.19.1(c) by replacing the BEJ biasing side with its Thevenin equivalent and also replacing the BJT with its large‐signal model (Figure 3.6(b)).

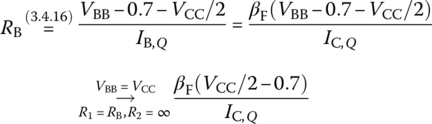

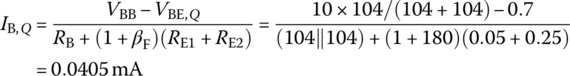

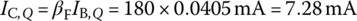

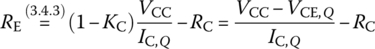

- For the circuit in Figure 3.19.1(c), find the DC voltage/currents corresponding to the operating point Q where the CE, forward large‐signal (DC) current gain βF of the BJT is assumed to be 180.

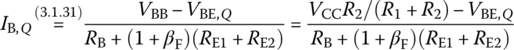

(3.1.30)

Figure 3.19.1 A CE BJT circuit and its DC/AC equivalents.

(3.1.31) (3.1.32)

(3.1.32) (3.1.33)

(3.1.33)

- The DC analysis can be done by running the following statements:

>>VCC=10; betaF=180; betaR=6;R1=104000; R2=104000; RC=200; RE=[50 250];BJT_DC_analysis(VCC,R1,R2,RC,RE,[betaF,betaR]);

- This yields the following results that conform with the above hand‐calculated results:

VCC VEE VBB VBQ VEQ VCQ IBQ IEQ ICQ10.00 0.00 5.00 2.90 2.20 8.54 4.05e-005 7.32e-003 7.28e-003in the forward-active mode with VCE,Q= 6.35

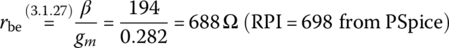

- AC Analysis

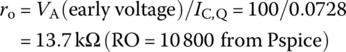

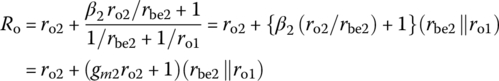

- Determine the small‐signal parameters such as gm, β, and rbe = rπ, ro, ….

(3.1.34) (3.1.36)

(3.1.36) (3.1.37)

(3.1.37)

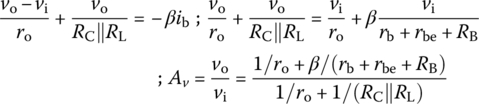

- Remove every DC source (by open/short‐circuiting the current/voltage sources) and short/open‐circuit every (large) capacitor/inductor to find the AC equivalent circuit as Figure 3.19.1(d) where the BJT is replaced by its low‐frequency small‐signal model (Figure 3.18(b)).

Figure 3.19.2 Low‐frequency AC equivalent without Rs, R1, R2, and RL to find the open‐loop gain Avo = vo/vi.

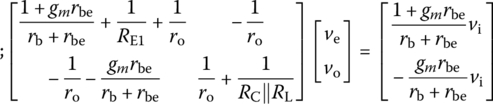

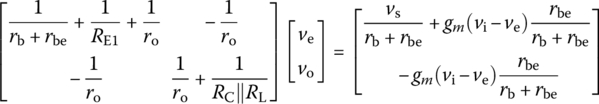

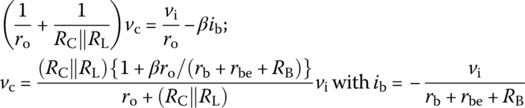

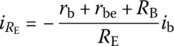

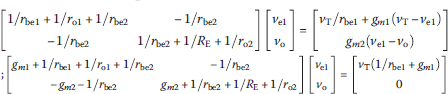

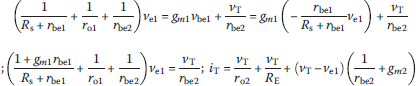

- To find the voltage gain Av=vo/vi, we remove Rs and RB=R1||R2 and then make a V‐to‐I source transformation for node analysis to get the circuit as shown in Figure 3.19.2(b).

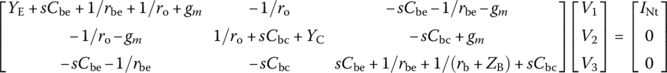

- Then we can set up the node equation as

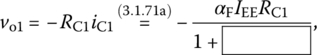

- In case RE1 = 0, we have just one‐node circuit and get the voltage gain as

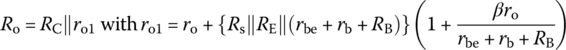

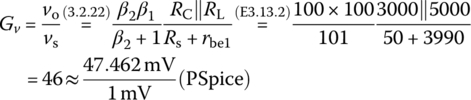

- Once we have got the open‐loop voltage gain Avo (with RL = ∞) and the input/output resistances Ri/Ro (see Eq. (3.2.1)/(3.2.4)), we can easily get the overall voltage gain (considering Rs) as

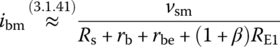

function [VBQ,VEQ,VCQ,IBQ,IEQ,ICQ,Av,Ai,Ri,Ro,gm,rbe,ro]=BJT_CE_analysis(VCC,rb,Rs,R1,R2,RC,RE,RL,beta,Vsm,VA,T)% Vsm = Amplitude of the AC input signal applied to base terminal through Cs% Copyleft: Won Y. Yang, [email protected], CAU for academic use onlyif nargin<12, T=27; end % Ambient temperatureif nargin<11, VA=1e4; end % Early voltagel_beta=length(beta); % bF may have been given as [betaF betaR betaAC Is]if l_beta<3, betaAC=beta(1); bF=beta; % bF=[betaF betaR]else betaAC=beta(3); bF=beta(1:2); if l_beta>3, bF=[bF beta(4)]; endend[VBQ,VEQ,VCQ,IBQ,IEQ,ICQ,mode]=BJT_DC_analysis(VCC,R1,R2,RC,RE,bF);RE1=RE(1);if R1>20, RB=parallel_comb([R1 R2]); else RB=R2; end % R1=VBB?[gm,rbe,re,ro]=gmrbero_BJT(ICQ,betaAC,VA,T);if Rs==0, Rs=0.01; endRCL= parallel_comb([RC RL]);if RE1>=1Y=[(1+gm*rbe)/(rb+rbe)+1/RE1+1/ro -1/ro; % gm*rbe=betaAC-1/ro-gm*rbe/(rb+rbe) 1/ro+1/RCL];vec = Y[1+gm*rbe;-gm*rbe]/(rb+rbe); % Eq. (3.1.39a)Av=vec(2);elseAv=-gm*rbe/(rb+rbe)*parallel_comb([ro RCL]); % Eq. (3.1.39b)endRbeE = rb+rbe+(betaAC+1)*RE1;Ri = parallel_comb([RB RbeE]); % Eq. (3.2.1)Ro = parallel_comb([RC ro]); % Eq. (3.2.4)Ai = -betaAC*RC/(RC+RL); % Eq. (3.2.2)Gv=Av/(Rs/Ri+1); % Eq. (3.1.40)if nargin>9 & abs(Vsm)>0Ibm = Vsm/(Rs+RbeE);if Ibm>=IBQ, fprintf(' Possibly crash into the cutoff region sinceIbm(%6.2fuA)>IBQ(%6.2fuA) ',Ibm*1e6,IBQ*1e6); endif abs(Gv*Vsm-(1+betaAC)*Ibm*RE1)>=VCQ-VEQ-0.3 % Eq. (3.1.47)fprintf(' Possibly violate the saturation region since |Av*Vsm-(1+betaAC)*Ibm*RE1(%5.2f)|>VCQ-VEQ-0.3(%5.2f) ',abs(Av*Vsm-(1+betaAC)*Ibm*RE1), VCQ-VEQ-0.3);endendfprintf(' Ri=%9.3f[kOhm], Ro=%8.0f[Ohm] Gv=Ri/(Rs+Ri)xAv = %6.3fx%8.2f =%8.2f ', Ri/1e3,Ro,1/(Rs/Ri+1),Av,Gv);function [gm,rbe,re,ro]=gmrbero_BJT(ICQ,beta,VA,VT)if VT>0.1, VT=(273+VT)/11605; end % considering VT as Tgm=abs(ICQ)/VT; rbe=beta/gm; re=rbe/(beta+1); ro=VA/abs(ICQ); %(3.1.26-28)

If we assume that R1, R2, and ro are so large (compared with other resistors) as to be negligible as parallel elements, we can approximate the AC equivalent as Figure 3.19.1(d) so that we can write the (small‐signal) base current ib, collector current ic, and output voltage vo as

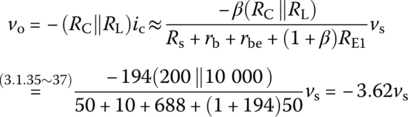

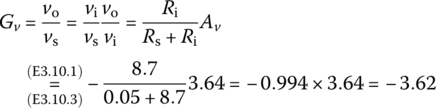

The DC/AC analysis procedure, which has been cast into the MATLAB function ‘BJT_CE_analysis()’ listed above, can be carried out by running the following statements:

>>VCC=10; Vsm=0.02; rb=10; betaF=180; betaR=6; betaAC=194;Rs=50; R1=104000; R2=104000; RC=200; RE=[50 250]; RL=10000;BJT_CE_analysis(VCC,rb,Rs,R1,R2,RC,RE,RL,[betaF betaR betaAC],Vsm);

This yields the following result that conforms with that obtained above:

gm= 281.664[mS], rbe= 689[Ohm], ro= 1373[kOhm]Gv=Ri/(Rs+Ri)xAv = 0.994 x -3.64 = -3.62

Figure 3.20(a), (b), and (c) shows the PSpice schematic of the BJT circuit in Figure 3.19.1(a), its simulation result of the input/output voltage waveforms, and a part of simulation output file containing the netlist and the bias (operating) point information, respectively. Note that the voltage gain can be computed from the ratio between the negative/positive peak values of input/output signals shown in the Probe Cursor box as

Figure 3.20 PSpice simulation of the CE BJT circuit in Figure 3.19.1a (“elec03f20.opj”).

where the negative sign indicates a phase shift of 180° between the input and the output.

Now, consider the following question:

Won’t the voltage gain and/or the linear input‐output relationship be changed when the amplitude (vsm) of the AC input voltage vs increases?

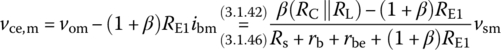

To find out the answer to this question, let us make a soft experiment of increasing vsm to 0.3 V, 1 V, and 1.5 V. The PSpice simulation results are depicted in Figure 3.21(a), (b), and (c), which show that the upper part of the output voltage waveform is distorted for vsm = 1 V and both the upper and lower parts of the output voltage waveform are distorted for vsm = 1.5 V. (This explains the meaning of ‘small‐signal’, illustrating that the small‐signal analysis result based on the linear approximation is valid only within a certain range of the input signal.) Why is that? To understand why the upper and/or lower parts of the output voltage waveform to large inputs are distorted, we should use the load line analysis by drawing the DC load line to determine the operating point Q and drawing the AC load line at the operating point Q (see Figure 3.22(a)) if there exists a (bypass) capacitor (like CE) connected in parallel with the emitter resistor RE2 (see Figure 3.19.1(a) or 3.20(a)).

Note that the equations of the DC/AC load lines are obtained by applying KVL through VCC‐RC‐vCE‐RE as

where the bypass capacitor CE is assumed to have a negligibly small reactance 1/ωCE like a short‐circuit for the input signal frequency ω and the (negative) emitter current −iE is assumed to be (almost) equal to the collector current iC since the base current is negligibly small compared with the collector/emitter currents.

Figure 3.21 Distortion in the output voltage of the circuit of Figure 3.20a due to a large amplitude of input.

Note also that the AC input moves the instantaneous operating point along the AC load line around the quiescent operating point Q, i.e. the intersection of the DC load line and the CE characteristic curve corresponding to the base current iB determined by the DC biasing circuit. With this background knowledge, Figure 3.22(a) together with b‐d shows how iC (the collector current) and vCE (the collector‐to‐emitter voltage) vary with the variation of iB due to the AC signal. About Figure 3.22, there are several observations to make:

- A BJT crashes into the cutoff region if the amplitude of ib (the AC component of base current iB computed roughly by Eq. (3.1.41)) exceeds IB,Q so that the total base current iB = IB,Q + ib may become zero where

Figure 3.22 DC and AC load lines for the CE BJT circuit in Figure 3.19.1a.

(3.1.46)

- A BJT trespasses on the saturation region if the maximum variation of vce (the AC component of collector‐to‐emitter voltage) exceeds VCE,Q−VCE,sat(0.2 V) where

- Increasing RE1 (with the voltage gain Av [Eq. (3.1.49)] decreased) reduces the DC base current

- and decreases the slope 1/(RC + RE1 + RE2) of the DC load line so that the operating point Q can move left (toward the saturation region) downwards (toward the cutoff region). However, the possibility of the BJT to trespass on the saturation region and/or crash into the cutoff region decreases because the maximum variations of vce (Eq. (3.1.47)) and ic = (β + 1)ib decrease more abruptly than the operating point Q moves left downwards.

| vsm (V) | VCC (V) | R1 (kΩ) | R2 (kΩ) | RC (Ω) | RE1 (Ω) | RE2 (Ω) | IB,Q (μA) | IC,Q (mA) | VCE,Q (V) | Remark | |

| (1) | 1.5 | 10 | 104 | 104 | 200 | 50 | 250 | 40 | 7.37 | 6.3 | Cutoff, Sat |

| (2) | 1.5 | 10 | 104 | 104 | 200 | 200 | 250 | 32.1 | 5.83 | 6.19 | Cutoff |

| (3) | 1.5 | 10 | 104 | 104 | 200 | 200 | 100 | 40 | 7.37 | 6.3 | Normal |

| (4) | 1.5 | 10 | 104 | 104 | 400 | 200 | 100 | 40.4 | 7.31 | 4.87 | Normal |

- Decreasing RE2 (with the voltage gain Av (Eq. (3.1.49)) unaffected) increases the DC base current IB,Q (Eq. (3.1.48)) and the slope 1/(RC + RE1 + RE2) of the DC load line so that the operating point Q can move right (away from the saturation region) upwards (away from the cutoff region). Thus, the possibility of the BJT to be saturated and/or cut off decreases.

- Decreasing RC decreases the maximum variation of vce (Eq. (3.1.47)) to reduce the possibility of the BJT to trespass on the saturation region, but it reduces the voltage gain

- Increasing VCC (with the voltage gain Av unaffected) increases the DC base current IB,Q (3.1.48) and pushes the vCE‐intercept rightwards so that the operating point Q can move right upwards. Thus, the possibility of the BJT to be saturated and/or cut off decreases.

The PSpice simulation results of the circuit in Figure 3.19.1(a) or 3.20(a) are depicted in Figure 3.23, which supports the observations stated above. Figure 3.23(a1)/(b1) shows the simulation results and load line analysis for the circuit with RC = 200 Ω, RE1 = 50 Ω, and RE2 = 250 Ω, respectively. Figure 3.23(a2)/(b2) shows the simulation results and load line analysis for the circuit with RC = 200 Ω, RE1 = 200 Ω, and RE2 = 250 Ω, respectively, supporting the observation that increasing RE1 (with the voltage gain Av decreased) will move the operating point Q left downwards, but will decrease the maximum variations of vce and ic more abruptly so that the possibility of the BJT to trespass on the saturation region and/or crash into the cutoff region can decrease. Figure 3.23(a3)/(b3) shows the simulation results and load line analysis for the circuit with RC = 200 Ω, RE1 = 200 Ω, and RE2 = 100 Ω, respectively, supporting the observation that decreasing RE2 (with the voltage gain Av unaffected) will move the operating point Q right upwards so that the possibility of the BJT to trespass on the saturation region and/or crash into the cutoff region can decrease. Figure 3.23(a4)/(b4) shows the simulation results and load line analysis for the circuit with RC = 400 Ω, RE1 = 200 Ω, and RE2 = 100 Ω, respectively, implying that increasing RC may increase the voltage gain Av without trespassing on the saturation region or crashing into the cutoff region thanks to the increase of linearity margin secured by increasing RE1 and decreasing RE2.

Figure 3.23 DC and AC load line for the CE BJT circuit (in Figure 3.19.1a) with different resistor values.

Can the possibility of a BJT to trespass on the saturation region or crash into the cutoff region be predicted by the MATLAB function ‘BJT_CE_analysis()’? Let us try it for the above four cases:

>>VCC=10; Vsm=1.5; rb=10; betaF=180; betaR=6; betaAC=194;Rs=50; R1=104e3; R2=104e3; RC=200; RE=[50 250]; RL=1e4; % (1)BJT_CE_analysis(VCC,rb,Rs,R1,R2,RC,RE,RL,[betaF betaR betaAC],Vsm);VCC VEE VBB VBQ VEQ VCQ IBQ IEQ ICQ10.00 0.00 5.00 2.90 2.20 8.54 4.05e-05 7.32e-03 7.28e-03in the forward-active mode with VCE,Q= 6.35gm= 281.664[mS], rbe= 689[Ohm], ro= 1373[kOhm]Possibly crash into the cutoff regionPossibly violate the saturation regionGv=Ri/(Rs+Ri)xAv = 0.994 x -3.64 = -3.62>>Rs=50; R1=104e3; R2=104e3; RC=200; RE=[200 250]; RL=1e4; % (2)BJT_CE_analysis(VCC,rb,Rs,R1,R2,RC,RE,RL,[betaF betaR betaAC],Vsm);VCC VEE VBB VBQ VEQ VCQ IBQ IEQ ICQ10.00 0.00 5.00 3.32 2.62 8.84 3.22e-05 5.83e-03 5.80e-03in the forward-active mode with VCE,Q= 6.22gm= 224.360[mS], rbe= 865[Ohm], ro= 1724[kOhm]Possibly crash into the cutoff regionGv=Ri/(Rs+Ri)xAvo = 0.998 x -0.95 = -0.95>>Rs=50; R1=104e3; R2=104e3; RC=200; RE=[200 100]; RL=1e4; % (3)BJT_CE_analysis(VCC,rb,Rs,R1,R2,RC,RE,RL,[betaF betaR betaAC],Vsm);VCC VEE VBB VBQ VEQ VCQ IBQ IEQ ICQ10.00 0.00 5.00 2.90 2.20 8.54 4.05e-05 7.32e-03 7.28e-03in the forward-active mode with VCE,Q= 6.35gm= 281.664[mS], rbe= 689[Ohm], ro= 1373[kOhm]Gv=Ri/(Rs+Ri)xAv = 0.998 x -0.96 = -0.96>>Rs=50; R1=104e3; R2=104e3; RC=400; RE=[200 100]; RL=1e4; % (4)BJT_CE_analysis(VCC,rb,Rs,R1,R2,RC,RE,RL,[betaF betaR betaAC],Vsm);VCC VEE VBB VBQ VEQ VCQ IBQ IEQ ICQ10.00 0.00 5.00 2.90 2.20 7.09 4.05e-05 7.32e-03 7.28e-03in the forward-active mode with VCE,Q= 4.89gm= 281.664[mS], rbe= 689[Ohm], ro= 1373[kOhm]Gv=Ri/(Rs+Ri)xAv = 0.998 x -1.88 = -1.88

For the four cases, the MATLAB function ‘BJT_CE_analysis()’ seems to have worked well in terms of its prediction about the possibility of the BJT to be saturated or cut off.

Figure 3.24 Measurement of BJT power in PSpice (“elec03f24.opj”).

Now, to find the DC power of the BJT for the last case by using MATLAB, run the following MATLAB statements:

>>[VBQ,VEQ,VCQ,IBQ,IEQ,ICQ,Av]=BJT_CE_analysis(VCC,rb,Rs,R1,R2,RC,RE,RL, [betaF betaR betaAC],Vsm);>>PQ_DC=(VCQ-VEQ)*ICQ+(VBQ-VEQ)*IBQ % DC power of BJT QPQ_DC= 0.0356 % 35.6mW

The instantaneous (DC + AC) power of the BJT can easily be found as depicted in Figure 3.24(b2) by running the PSpice schematic (Figure 3.24(a2)) with a power (W) marker placed at the center of the device. Why is the instantaneous power pQ(t) always below the DC power PQ,DC =35.6 mW of BJT? It is because vce ic < 0 (Figure 3.24(b1)) so that the AC power of the BJT is negative, implying that the BJT Q is acting as an AC source (active element) supplying an AC power to the other parts.

3.1.9 BJT Current Mirror

Consider the circuit of Figure 3.25(a) where the BJT Q1 is said to be diode‐connected’ or ‘connected in diode configuration’ since its collector and base terminals are short‐circuited so that it behaves like a diode. Why is a BJT used as a diode? It is for efficiency of fabricating integrated circuit (IC) with matched devices. For proper operation of the circuit, the two BJTs Q1 and Q2 must be matched in the sense that they have identical current gains (αF,βF) and characteristic curves.

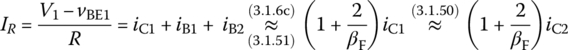

Let us analyze the circuit of Figure 3.25(a), which is called a current mirror because the currents of the two matched BJTs sharing the same vBE are equal. Assume that the voltage sources V1 and V2 forward‐bias the B‐E junctions and reverse‐bias the B‐C junctions (vBC < 0.4) of both BJTs to let them operate in the forward‐active mode so that vBE1 = vBE2 = 0.7 V and

Noting that the voltage at node 1 (the lump of terminals C1‐B1‐B2) is vBE1 = 0.7 V, we apply KCL at the node to write

which yields the output current as

This is supported by the PSpice simulation result (with Bias Point analysis) listed in Figure 3.25(a), which shows that the current iC2 supplied by the current mirror is constant as about 1.4 mA for different values of V2 and, therefore, the current mirror can be used as a current source.

Let us analyze the circuit of Figure 3.25(b), which is also called a circuit mirror because the currents of the two matched BJTs Q1 and Q2 are equal. Assume that the voltage sources V1 and V2 forward‐bias the B‐E junctions and reverse‐bias the B‐C junctions (vBC < 0.4) of the three BJTs to let them operate in the forward‐active mode so that vBE1 = vBE2 = vBE3 = 0.7 V and

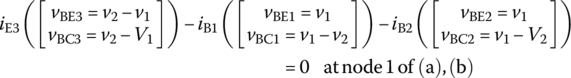

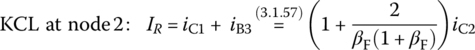

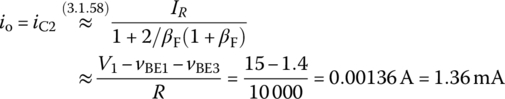

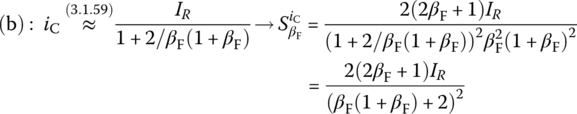

Noting that the voltage at node 1 (the lump of terminals E3‐B1‐B2) is vBE1 = 0.7 V and the voltage at node 2 (the lump of terminals C1‐B3) is vBE1 + vBE3 = 1.4 V, we can write

Figure 3.25 Current mirrors using BJTs (“elec03f25.opj”).

This yields the output current as

This is supported by the PSpice simulation result (with Bias Point analysis) listed in Figure 3.25(b), which shows that the current iC2 supplied by the current mirror is constant as about 1.35 mA for different values of V2 and, therefore, the current mirror can be used as a current source.

Let us compare the sensitivities of iC2 w.r.t. βF for the two current sources:

This implies that the current mirror (b) has smaller sensitivity of the output current iC2 w.r.t. βF (roughly proportional to ![]() ) compared with that of the current mirror (a) (roughly proportional to

) compared with that of the current mirror (a) (roughly proportional to ![]() ).

).

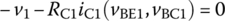

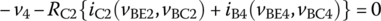

Now, to analyze the 3‐BJT current mirror (Figure 3.26(a)) and that with R replaced by a current source I (Figure 3.26(b)) by using the exponential model, we apply KCL at nodes 1 and 2 to write

where iCk(vBEk, vBCk) and iBk(vBEk, vBCk) are defined by Eqs. (3.1.23a,b), and iEk(·,·) = iBk(·,·) + iCk(·,·) for all k. The following MATLAB function ‘BJT3_current_mirror()’ solves the set of Eqs. (3.1.62a,b) for circuit (a) or Eqs. (3.1.62a,c) for circuit (b) depending on whether the value of the third input argument R is greater than or equal to 1 or not. It returns the output current io = iC2 and v = [v1 v2] for possibly several values of V2 (given as the second to last elements of the fourth input argument V12). For instance, we can solve the circuit of Figure 3.25(b) to get io for V1 = 15 V and V2 = {1, 5, 10, 20, 40} by running the following MATLAB statements:

Figure 3.26 Current mirrors using a BJT as a diode.

>>R=1e4; Is=1e-14; io=BJT3_current_mirror([100 1],Is,R,[15 1 5 10 20 40])

function [io,vs]=BJT3_current_mirror(betaF,Is,R,V12,VT)% Analyze a current mirror consisting of 3 BJTs and an R or I-source% If R<1, it will be regarded as a current source I=R.% Copyleft: Won Y. Yang, [email protected], CAU for academic use onlyif nargin<5, VT=(273+27)/11605; end % Thermal voltageif length(betaF)<2, betaR=1; else betaR=betaF(2); betaF=betaF(1); endif length(Is)<2, VA=inf; else VA=Is(2); Is=Is(1); endV1=V12(1); if length(V12)>1, V2s=V12(2:end); else V2s=V12; endalphaR=betaR/(betaR+1); Isc=Is/alphaR; % Collector-Base saturation currentoptions=optimset('Display','off','Diagnostics','off');iC = @(v)Is*exp(v(1)/VT)-Isc*exp(v(2)/VT); % Eq. (3.1.23a) with v=[vBE vBC]iB = @(v)Is/betaF*exp(v(1)/VT)+Isc/(betaR+1)*exp(v(2)/VT); % Eq. (3.1.23b)iE = @(v)Is*(1+1/betaF)*exp(v(1)/VT)-Isc*betaR/(betaR+1)*exp(v(2)/VT);for n=1:length(V2s)V2=V2s(n);if R>=1 % Eq. (3.1.62a,b) with a resistoreq=@(v)[iE([v(2)-v(1) v(1)-V1])-iB([v(1) v(1)-v(2)])-iB([v(1) v(1)-V2]);V1-v(2)-R*(iB([v(2)-v(1) v(2)-V1])+iC([v(1) v(1)-v(2)]))];else I=R; % Eq. (3.1.62a,c) with a current sourceeq=@(v)[iE([v(2)-v(1) v(2)-V1])-iB([v(1) v(1)-v(2)])-iB([v(1) v(1)-V2]);I-iB([v(2)-v(1) v(2)-V1])-iC([v(1) v(1)-v(2)])]*1e3;endv0=[0.7 0.4]; % Initial guessv=fsolve(eq,v0,options); vs(n,:)=v; io(n)=iC([v(2) v(2)-V2]);end

3.1.10 BJT Inverter/Switch

Figure 3.27(a1)/(a2) shows the PSpice schematics of BJT inverter for Transient/DC_Sweep analysis. Figure 3.27(b1) shows the input and output voltage waveforms of the inverter (obtained from the Transient analysis) where the input 1(high)/0(low) drives the BJT into the saturation/cutoff mode so that the output vo = vCE can go to logic 0(low)/1(high) with high‐to‐low/low‐to‐high propagation delay tpHL/tpLH that are defined as the times between the 50% input and 50% output.

Note that in order for the BJT to go back and forth between the saturation and cutoff modes, the collector current iC,sat in the saturation mode should be less than βF times the base current iB:

Figure 3.27 BJT inverter.

This condition can easily be satisfied by taking a small RB and a large RC. But the following should be noted:

- A small RB makes the input impedance small so that the fan‐in of the gate can be decreased where fan‐in is the number of logic gates that can be connected to its input without deteriorating the input signal or producing an undefined or incorrect output.

- A large RC makes the output impedance and loading effect (due to it) large so that the (output‐high) fan‐out of the gate can be decreased where fan‐out is the number of logic gates that can be connected to its output (as loads) without producing an undefined or incorrect output.

Figure 3.27(b2) shows the input(vi)‐output(vo) relationship, called the VTC (voltage transfer characteristic), of the inverter (obtained from the DC Sweep analysis). In the VTC, the output low/high levels VOH/VOL are defined as the minimum/maximum values of output vo corresponding to logic 1/0, respectively and VIH/VIL are defined as the minimum/maximum values of input vs that can be interpreted as logic 1/0, respectively, where VIL/VOH are the input/output at point A with slope of −1 and VIH/VOL are the input/output at point B with slope of −1. Also, we define the midpoint M as the intersection of the VTC and line vo = vi, which can be thought of as the boundary at which the inverter switches its output from one state to the other.

Figure 3.28(a) shows a practical VTC together with an ideal VTC. As measures of how much the gate can tolerate the variation of signal levels without causing any erroneous logical state, Figure 3.28(b1)/(b2) shows the high and low noise margins for practical/ideal VTCs where the high and low noise margins are defined as

What are the physical meanings of the high/low noise margins? As can be seen in Figure 3.28(b1) or (b2), the high/low noise margin means how much the high(1)/low(0) signal can decrease/increase without being mistaken for a low(0)/high(1) signal by the next‐stage (load) gate (the same kind of inverter), i.e. without misleading (mistakenly driving) the load inverter into the cutoff/saturation mode like a low/high voltage. The absolute noise margin is defined as the smaller of the two noise margins:

Note that the noise immunity measured by the absolute noise margin is maximized by the ideal VTC with abrupt switching at VIL = VIH = (VOL + VOH)/2, which has maximum logic swing from V(0) to V(1), but no transition region.

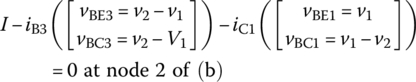

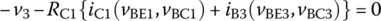

To analyze the BJT inverter circuit in Figure 3.27(a1) by using the exponential model, we can apply KVL around the two meshes to write

where iC(vBE, vBC) and iB(vBE, vBC) are defined by Eqs. (3.1.23a,b).

Figure 3.28 Practical/ideal voltage transfer characteristics (VTCs) and the corresponding noise margins.

function [VIL,VIH,VOL,VOH,VM,NML,NMH,Pavg,vo1,iC1]=... BJT_inverter(betaF,Is,RB,RC,VCC,vi1,VT)% Plot the VTC of a BJT inverter (with no output argument)% which consists of an NPN-BJT and resistors RB/RC between vi/VCC and B/C.% Copyleft: Won Y. Yang, [email protected], CAU for academic use onlyif nargin<7, VT=(273+27)/11605; end % Thermal voltageif length(betaF)<2, betaR=1; else betaR=betaF(2); betaF=betaF(1); endalphaR=betaR/(betaR+1); Isc=Is/alphaR; % CB saturation currentdvi=5e-3; vis=[0:dvi:VCC]; vCE_sat=0.2;options=optimset('Display','off','Diagnostics','off');iC = @(v)Is*exp(v(1)/VT)-Isc*exp(v(2)/VT); % Eq. (3.1.23a) with v=[vBE vBC]iB = @(v)Is/betaF*exp(v(1)/VT)+Isc/(betaR+1)*exp(v(2)/VT); % Eq. (3.1.23b)for n=1:length(vis)vi = vis(n);if vi>=0.4 % v = [vBE vBC]eq = @(v)[vi-v(1)-RB*iB(v); VCC-RC*iC(v)+v(2)-v(1)]; % Eq. (3.1.66)if ~exist('v'), v0=[0.7 0.4]; else v0=v; end % Initial guessv = fsolve(eq,v0,options);vos(n)=v(1)-v(2); iCs(n)=(VCC-vos(n))/RC; % Eqs. (3.1.67),(3.1.66b)else vos(n)=VCC; iCs(n)=0; % Cutoff modeendend[VIL,VIH,VOL,VOH,VM,NML,NMH,VL,Pavg]=... find_pars_of_inverter(vis, vos,iCs,VCC);if nargout==0|nargin<6plot(vis,vos,[VIL VM VIH],[VOH VM VOL],'ro');endif nargin>5 % If you want vo1 for vi1for i=1:length(vi1)[dmin,imin]=min(abs(vis-vi1(i)));vo1(i)=vos(imin); iC1(i)=iCs(imin);endelse vo1=vos; iC1=iCs;endfunction [VIL,VIH,VOL,VOH,VM,NML,NMH,VL,Pavg]=...find_pars_of_inverter(vis,vos,is,Vs,VH)if nargin<5, VH=Vs; end % Highest output voltagedvs=abs(diff(vis)); dv=min(dvs(find(dvs>1e-6)));[pks,locs]=findpeaks(1./abs(diff([vos(1) vos])+dv));[pks,inds]=sort(pks,'descend'); inds1=locs(inds(1:2));[VLH,inds2]=sort(vis(inds1)); % Points with slope=-1VIL=VLH(1); VIH=VLH(2); VOH=vos(inds1(inds2(1))); VOL=vos(inds1(inds2(2)));NML = VIL-VOL; NMH = VOH-VIH; % Eq. (3.1.64)[em,imin]=min(abs(vis-vos)); VM=vis(imin); % Midpoint[em,imin]=min(abs(vis-VH)); VL=vos(imin); % Virtual lowest outputPavg=Vs*mean([max(is) min(is)]); % Average power for on-off periods

Once we solve this set of equations to find vBE and vBC for a given value of the input voltage vi, we can find the output voltage vo as

The process of solving Eq. (3.1.66) to find vo for vi = 0~VCC, finding VIL,VIH,VOL, VOH, and VM, and plotting vo versus vi has been cast into the above MATLAB function ‘BJT_inverter()’. We can run the following script “plot_VTC_BJT_inverter.m” (which uses ‘BJT_inverter()’)

%plot_VTC_BJT_inverter.mVCC=5; RB=1e4; RC=1e3;betaF=180; betaR=6; Is=1e-14;[VIL,VIH,VOL,VOH,VM,NML,NMH,Pavg]=...BJT_inverter([betaF betaR],Is,RB,RC,VCC)

to get the VTC as shown in Figure 3.28(a) and the inverter parameter values as

VIL = 0.565, VIH= 0.990, VOL= 0.151, VOH= 4.971, VM= 0.920NML = 0.414, NMH= 3.981, VL = 0.031Pavg= 12.423[mW]

3.1.11 Emitter‐Coupled Differential Pair

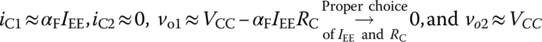

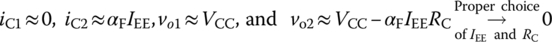

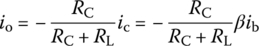

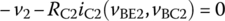

Figure 3.29(a) shows an emitter‐coupled (in the sense that the emitter terminals of the two BJTs are connected) or differential (in the sense that its output varies with the differential input vd = vBE1 − vBE2) pair. To analyze this circuit, we assume that both BJTs operate in the forward‐active mode so that we can use Eq. (3.1.1b) to write their approximate collector/emitter currents as

Then their ratios can be approximately written as

Figure 3.29 Emitter‐coupled (differential) pair and its VTC.

Also, we apply KCL at the node E1‐E2 to write

Combining Eqs. (3.1.69) and (3.1.70) yields the expression of each collector current as

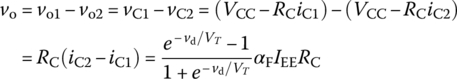

where these collector currents are depicted in Figure 3.29(b). Then we can write the (differential) output voltage as

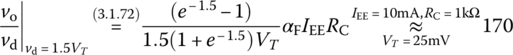

This differential output voltage vo, together with vo1 and vo2, is shown in Figure 3.29(c). From Figure 3.29 and Eqs. (3.1.71a,b) and (3.1.72), note the following:

- If −1.5VT < vd < 1.5VT, the differential output voltage vo and other signals vary almost linearly with the differential input vd, allowing the emitter‐coupled pair to be used as an amplifier with a voltage gain of

(3.1.73)

- If vd > 4VT, we have

(3.1.74a)

- On the other hand, if vd < −4VT, we have

(3.1.74b)

- It is implied that a large swing of the differential input vd = ±4VT makes the two BJTs Q1/Q2 operate as closed/open or open/closed switches, producing two distinct levels of differential output vo depending on whether vd = 4VT or vd = −4VT.

- The amplifying/switching properties are extensively used in analog/digital circuits, respectively. That is why the emitter‐coupled or differential pair is one of the most important configurations employed in ICs.

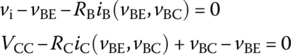

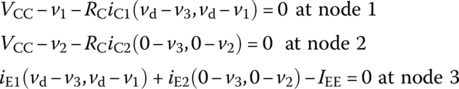

To analyze the BJT differential pair circuit in Figure 3.29(a), we can apply KCL at nodes 1, 2, and 3 to write

where iCk(vBEk, vBCk) and iBk(vBEk, vBCk) are defined by Eqs. (3.1.23a,b). The process of solving this set of equations to find v = [v1 v2 v3] for vd = −Vdm~Vdm and plotting vo = v1 − v2, iC1, iC2 (together with their analytic values computed by Eqs. (3.1.72,74) versus vd has been cast into the following MATLAB function ‘

BJT_differential()’. We can run>>betaF=100; betaR=1; Is=1e-14; IEE=10e-3; RC=1e3; VCC=12;BJT_differential([betaF betaR],Is,IEE,RC,VCC);to get the graphs of iC1, iC2, and vo as shown in Figure 3.29(b) and (c).

function [vo1s,vo2s,iC1s,iC2s]=BJT_differential(betaF,Is,IEE,RC,VCC,Vdm)% Analyze an NPN-BJT differential (emitter-coupled) pair% (to find the outputs vo1/vo2 to a range of differential input vd=-Vdm~Vdm% and plot its VTC in case of no output argument)% which consists of 2 NPN-BJTs, 2 resistors RC1=RC2=RC, and an I-src IEE.% Copyleft: Won Y. Yang, [email protected], CAU for academic use onlyVT=(273+27)/11605; % Thermal voltageif nargin<6, Vdm=4*VT; enddvd=Vdm/100; vds=[-Vdm:dvd:Vdm]; % Differential inputif length(betaF)<2, betaR=1; else betaR=betaF(2); betaF=betaF(1); endalphaF=betaF/(1+betaF); alphaR=betaR/(betaR+1);Isc=Is/alphaR; % Collector-Base saturation currentoptions=optimset('Display','off','Diagnostics','off');iC = @(v)Is*exp(v(1)/VT)-Isc*exp(v(2)/VT); % Eq. (3.1.23a) with v=[vBE vBC]iE = @(v)Is*(1+1/betaF)*exp(v(1)/VT)-Isc*betaR/(betaR+1)*exp(v(2)/VT);for n=1:length(vds)vd = vds(n);eq=@(v)[VCC-v(1)-RC*iC([vd-v(3) vd-v(1)])VCC-v(2)-RC*iC([0-v(3) 0-v(2)])iE([vd-v(3) vd-v(1)])+iE([0-v(3) 0-v(2)])-IEE]; % Eq. (3.1.75)if ~exist('v'), v0=[VCC VCC/2 -0.7]; else v0=v; end % Initial guessv = fsolve(eq,v0,options);vo1s(n)=v(1); vo2s(n)=v(2); vos(n)=v(1)-v(2); % Eq. (3.1.72)iC1s(n)=iC([vd-v(3) vd-v(1)]); iC2s(n)=iC([-v(3) -v(2)]);endiC1s_a=alphaF*IEE./(1+(exp(-vds/VT))); % Eq. (3.1.71a)iC2s_a=alphaF*IEE./(1+(exp(vds/VT))); % Eq. (3.1.71b)if nargout==0subplot(211)plot(vds,iC1s,'g', vds,iC2s,'r', vds,iC1s_a,'k:', vds,iC2s_a,'b:')legend('iC1','iC2','iC1_a','iC2_a'); xlabel('v_d'); ylabel('i_C');vos_a=(exp(-vds/VT)-1)./(1+exp(-vds/VT))*alphaF*IEE*RC; % Eq. (3.1.72)subplot(212) plot(vds,vos,'g', vds,vo1s,'r', vds,vo2s, vds,vos_a,'k:')legend('vo','vo1','vo2','vo_a'); xlabel('v_d'); ylabel('v_o');end

3.2 BJT Amplifier Circuits

This section deals with several configurations of BJT amplifier, i.e. the CE (common‐emitter) amplifier, the CC (common‐collector) amplifier (called an emitter follower), the CB (common‐base) amplifier, and cascaded or compound multistage amplifier.

3.2.1 Common‐Emitter (CE) Amplifier

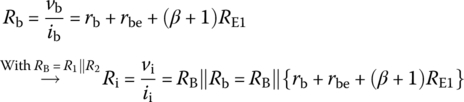

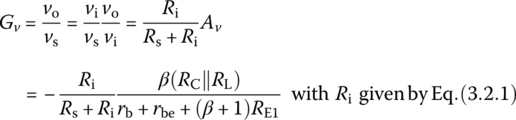

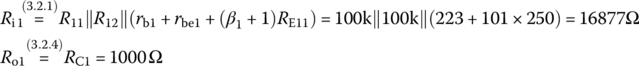

Figure 3.30 shows a CE amplifier and its low‐frequency AC equivalent (which is the same as Figure 3.19.1(d)) where the BJT has been replaced by the equivalent in Figure 3.18(b), and the biasing resistances R1||R2 and BJT output resistance ro are assumed to be so large as to be negligible as parallel resistors. Let us find the input resistance, current gain, voltage gain, and output resistance.

- Input Resistance Ri

To find the input resistance, i.e. the equivalent resistance seen from the source side, we apply KVL for the left mesh (denoted in a gray closed curve) with RB = R1||R2 neglected to write

Figure 3.30 A CE (common‐emitter) BJT circuit and its low‐frequency AC equivalent.

This yields the input resistance as

- Current Gain Ai

The output current io through the load resistor RL can be expressed as

Thus, the current gain, i.e. the ratio of the output current io to the input current ii = ib is

- Voltage Gains Gvand Av

The overall voltage gain, i.e. the ratio of the output voltage vo to the source voltage vs is

- Output Resistance Ro

To find the (Thevenin) equivalent resistance seen from the load side, we need to remove the (independent) voltage source vs by short‐circuiting it. Then no current flows of itself so that we have ib = 0, vbe = 0, and ic = 0 even if a test voltage or current source is applied to the output port. Therefore, the output resistance turns out to be

This AC analysis process to find Ri, Ro, Ai, and Av has been included in the MATLAB function ‘

BJT_CE_analysis()’ presented in Section 3.1.8. If a current source supplying a BJT with its DC emitter current IE,Q is given instead of the biasing circuit as depicted in Figure 3.31(a), the following MATLAB function ‘BJT_CE_analysis_I()’ can be used for the AC analysis.

function [Av,Ai,Ri,Ro,gm,rbe,ro,vsm,vom]=...BJT_CE_analysis_I(Rs,RB,RC,RE,RL,IEQ,beta,VA,T,vbem)% To analyze CE amplifier biased by IEQ% beta = [betaAC rb] if a nonzero base resistance is given.% If the 10th input argument vbem (maximum vbe such that the BJT operated% in the linear region) is given, the following outputs will be returned.% vsm = Max amplitude of vs ensuring the linear operation of BJT.% vom = Max amplitude of vo when the BJT operates in the linear operation.% Copyleft: Won Y. Yang, [email protected], CAU for academic use onlyif nargin<9, T=27; end % Ambient temperatureif nargin<8, VA=1e4; end % Early voltageif length(beta)>1, rb=beta(2); beta=beta(1); else rb=0; endif length(RB)>1, RB=parallel_comb(RB); endif sum([Rs RB RC RE RL rb]<0), error('Resistance must be positive!'); endICQ = IEQ*beta/(beta+1); % Collector current at the bias point[gm,rbe,re,ro]=gmrbero_BJT(ICQ,beta,VA,T);RbeE = rbe + (beta+1)*RE(1);Ri = parallel_comb([RB RbeE]); % Eq. (3.2.1)Ro = parallel_comb([RC ro]); % Eq. (3.2.4)Ai = -beta/(1+RL/RC); % Eq. (3.2.2)Avo = -beta*Ro/RbeE; % Eq. (3.2.3) with neither RL nor roAv = Avo/(Ro/RL+1); % Eq. (3.2.3) with RL, but without considering roGv = Av/(Rs/Ri+1); % Taking Rs into considerationif nargout<1fprintf(' gm=ICQ/VT=%8.3f[mS], re=1/gm=%6.0f[Ohm], rbe=beta/gm=%6.0f [Ohm], ro=VA/ICQ=%7.2f[kOhm] ', gm*1e3,re,rbe,ro/1e3);fprintf(' Ri=RB||RbeE=%8.2f kOhm, Ro=RC||ro=%6.0f Ohm', Ri/1e3,Ro);fprintf(' Av=-beta*Ro/RbeE x RL/(Ro+RL) =%8.2f x%5.2f =%8.2fGv=Ri/(Rs+Ri)xAv =%5.3f xAv =%8.2f ', Avo,RL/(Ro+RL),Av,Ri/(Rs+Ri),Gv);endif nargin<10, vbem = NaN; endvsm=(Rs/Ri+1)*RbeE/rbe*vbem; vom=abs(Gv)*vsm;

Example 3.10 AC Analysis of CE Amplifier

- Consider the CE circuit in Figure 3.19.1(a) or 3.30(a) where VCC = 10 V, rb = 10 Ω, Rs = 50 Ω, R1 = 104 kΩ, R2 = 104 kΩ, RC = 200 Ω, RE1 = 50 Ω, RE2 = 250 Ω, RL = 10k Ω, βF = 180, βR = 6, βAC = 194, and VA = 104 V. Find Ri, Ro, Av = vo/vi, and Gv = vo/vs.

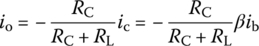

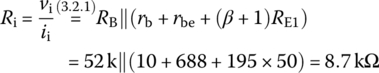

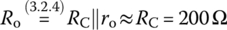

We can use the values of β, rb, rbe, and ro obtained in Section 3.1.8 (Eqs. (3.1.35‐38)) for the AC analysis as follows:

(E3.10.1) (E3.10.2)

(E3.10.2) (E3.10.3)

(E3.10.3) (E3.10.4)

(E3.10.4)

This AC analysis can also be done by using the MATLAB function ‘

BJT_CE_analysis()’ although the results will be slightly different since ro is taken into consideration in the MATLAB function:>>VCC=10; Vsm=0.02; rb=10; betaF=180; betaR=6; betaAC=194;Rs=50; R1=104000; R2=104000; RC=200; RE=[50 250]; RL=10000;BJT_CE_analysis(VCC,rb,Rs,R1,R2,RC,RE,RL,[betaF betaR betaAC],Vsm);Running these MATLAB statements yields

Results of analysis using the PWL modelwith betaF= 180, betaR= 6.0and R1= 104.00[kOhm], R2= 104.00[kOhm], RC= 200[Ohm], RE=300[Ohm]VCC VEE VBB VBQ VEQ VCQ IBQ IEQ ICQ10.00 0.00 5.00 2.90 2.20 8.54 4.05e-05 7.32e-03 7.28e-03in the forward-active mode with VCE,Q= 6.35[V]where beta_forced = ICQ/IBQ = 180.00 with beta = 180.00gm= 281.664[mS], rbe= 689[Ohm], ro= 1373.39[kOhm]Ri= 8.701 kOhm, Ro= 200 OhmGv=Ri/(Rs+Ri)xAvoxRL/(Ro+RL) = 0.994 x -3.71 x 0.980 = -3.62 - Consider the CE circuit in Figure 3.31(b) that is biased by a current source of I = 7.32 mA, which is equal to the value of IE,Q obtained in (a).

Since the circuit of Figure 3.31(b) is the same as that of Figure 3.19.1(a) or 3.30(a) dealt with in (a) (except for the current source I) and the value of the current source for biasing the BJT is equal to the DC emitter current IE,Q = 7.32 mA (obtained in Section 3.1.8), we will get the same AC analysis results as in part (a) by using the MATLAB function ‘

BJT_CE_analysis_I()’ (without having to do the DC analysis):>>VCC=10; Vsm=0.02; rb=10; betaAC=194;Rs=50; RB=52000; RC=200; RE=[50 250]; RL=10000; IEQ=7.32e-3;BJT_CE_analysis_I(Rs,RB,RC,RE,RL,IEQ,[betaAC rb]);Running these MATLAB statements yields

gm=ICQ/VT= 281.710[mS], re=1/gm= 4[Ohm], rbe=beta/gm= 689[Ohm], ro=VA/ICQ= 1373.16[kOhm]Ri=RB||RbeE= 8.700 kOhm, Ro=RC||ro= 200 OhmAv=-beta*Ro/RbeE x RL/(Ro+RL) = -3.71 x 0.98 = -3.64Gv=Ri/(Rs+Ri)xAv =0.994 xAv = -3.62

Figure 3.31 A CE circuit and its PSpice simulation results (“elec03e10a.opj”/“elec03e10b.opj”).

The theoretical values of Ri, Ro, and Av are close to not only those for the circuit of Figure 3.19.1(a) calculated in (a) but also those obtained from the PSpice simulation as shown in Figure 3.31(c):

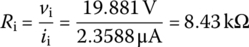

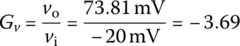

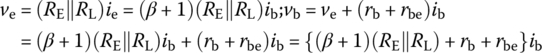

(E3.10.5) (E3.10.6)

(E3.10.6)

3.2.2 Common‐Collector (CC) Amplifier (Emitter Follower)

Figure 3.32 shows a CC amplifier and its low‐frequency AC equivalent where the BJT has been replaced by the equivalent in Figure 3.18(b) and the BJT output resistance ro is assumed to be so large as to be negligible as a parallel resistor. Let us find the input resistance, current gain, voltage gain, and output resistance.

Figure 3.32 A CC (common‐collector) BJT circuit and its low‐frequency AC equivalent.

- Input Resistance Ri

To find the input resistance from the relationship between vi = vb and ii, we express the voltages at nodes e and b in terms of ib as

This yields the equivalent resistance Rb seen from terminals b‐G as

so that we can write the input resistance (including RB = R1||R2) as

- Current Gain Ai

The output current io through the load resistor RL can be expressed as

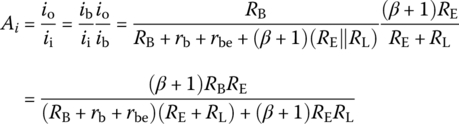

Thus, the current gain, i.e. the ratio of the output current io to the input current ii = ib is

- Voltage Gains Gvand Av

The voltage gain (with Rs = 0) is

The overall voltage gain, i.e. the ratio of the output voltage vo to the source voltage vs is

where Ri is given by Eq. (3.2.5). This implies that if Rs ≪ Ri and rb + rbe ≪ (β + 1)(RE||RL), the output voltage is almost equal to the source voltage and that is why the CC amplifier is called an emitter follower or buffer amplifier.

function [VBQ,VEQ,VCQ,IBQ,IEQ,ICQ,Av,Ai,Ri,Ro,gm,rbe,ro]=...BJT_CC_analysis(VCC,rb,Rs,R1,R2,RC,RE,RL,beta,Vsm,VA,T)% R1,R2 can be replaced by VBB,RB if VBB-RB is connected to the base.% If beta=[betaF betaR betaAC], large-signal model-based analysis% If beta=[betaF betaR betaAC Is], the exponential model-based analysis% Copyleft: Won Y. Yang, [email protected], CAU for academic use onlyif nargin<12, T=27; end % Ambient temperatureif nargin<11, VA=1e4; end % Early voltageif sum([rb Rs R1 R2 RC RE RL]<0), error('Resistance must be positive!'); endl_beta=length(beta);if l_beta<3, betaAC=beta(1); bF=beta; % bF=[betaF betaR]else betaAC=beta(3); bF=beta(1:2); % bF=[betaF betaR betaAC ..]if l_beta>3, bF=[bF beta(4)]; end % bF=[betaF betaR betaAC Is]end[VBQ,VEQ,VCQ,IBQ,IEQ,ICQ,mode]=BJT_DC_analysis(VCC,R1,R2,RC,RE,bF);if strcmp(mode,'forward-active')==0fprintf(' AC analysis is impossible in BJT_CC_analysis()because the BJT is in the saturation mode! ');Av=NaN; Ai=NaN; Ri=NaN; Ro=NaN; gm=NaN; rbe=NaN; ro=NaN;return;endRE1=RE(1);if R1>20, RB=parallel_comb([R1 R2]); else RB=R2; end % R1=VBB?if RE1<1, error('RE1 of CC amplifier (e-follower) may not be zero!'); end[gm,rbe,re,ro]=gmrbero_BJT(ICQ,betaAC,VA,T);RsB=parallel_comb([Rs RB]);RELo=parallel_comb([RE RL ro]);betaRELo=(betaAC+1)*RELo; rbebetaRELo=rb+rbe+betaRELo;Av=betaRELo/rbebetaRELo; % Eq. (3.2.7a)RbeEL = rb+rbe+(betaAC+1)*REL;REpRL = RE1*RL_Av/(RE1+RL_Av);if nargin>9 & abs(Vsm)>0Ibm = Vsm/Rs/rbebetaRELo/(1/Rs+1/RB+1/rbebetaRELo);if Ibm>=IBQ, fprintf(' Possibly crash into the cutoff region '); endif abs(Gv*Vsm)>=VCQ-VEQ-0.2 % Eq. (3.1.47)fprintf(' Possibly violate the saturation region ');endendRi=parallel_comb([RB RbeEL]); % Eq. (3.2.5)Ro=parallel_comb([RE1 (RsB+rb+rbe)/(betaAC+1)]); % Eq. (3.2.8)Ai=(betaAC+1)*RB*RE1/((RB+rb+rbe)*(RE1+RL)+(betaAC+1)*RE1*RL);% Eq. (3.2.6)Gv=Av/(Rs/Ri+1); % Eq. (3.2.7b) considering Rsfprintf(' gm=%8.3f[mS], rbe=%6.0f[Ohm], ro=%7.2f[kOhm] ',gm*1e3,rbe,ro/1e3)fprintf(' Ri=%9.3f[kOhm], Ro=%6.0f[Ohm] Gv=Ri/(Rs+Ri)xAv =%5.3f x%8.3f =%8.3f ', Ri/1e3,Ro,1/(Rs/Ri+1),Av,Gv);

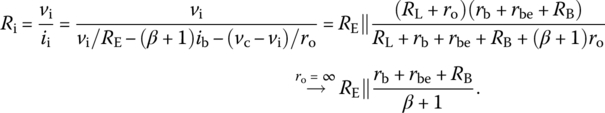

- Output Resistance Ro

To find the (Thevenin) equivalent resistance seen from the load side, we remove the (independent) voltage source vs by short‐circuiting it and apply a test voltage source VT to the output port. Then, the base current ib and the test current IT through VT are computed as

Thus, we find the output resistance as

The emitter follower has a very low output resistance (3.2.8), which enables the circuit to provide its load with much current without paying much attention to the loading effect. It also has a very high input resistance (3.2.5), which enables the circuit to save the current provided by its source (driver). In short words, the emitter follower is modest enough not to burden its source as well as generous to its load. (Isn’t the emitter follower praiseworthy? Who can blame such a nice guy for not amplifying the voltage?) That is the main feature of emitter follower with an almost unity voltage gain.

Example 3.11 AC Analysis of CC Amplifier (Emitter Follower)

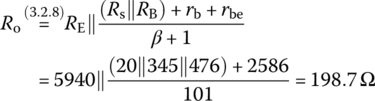

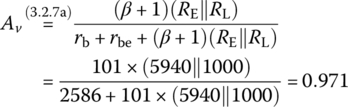

Consider the CC circuit in Figure 3.33(a) where VCC = 15 V, rb = 0 Ω, Rs = 20 kΩ, R1 = 345 kΩ, R2 = 476 kΩ, RC = 4 kΩ, RE = 5940 Ω, RL = 1 kΩ, βF = 100, βR = 1, βAC = 100, and VA = 100 V. Find Ri, Ro, Av = vo/vi, and Gv = vo/vs and compare the value of Gv with that obtained from PSpice simulation.

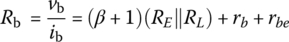

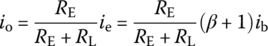

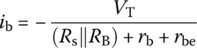

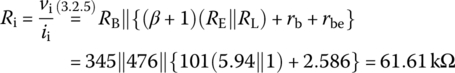

We can use the values of rbe = 2586 Ω and ro = 104 kΩ (obtained by using the MATLAB function ‘BJT_DC_analysis()’ and ‘gmrbero_BJT()’ in ‘BJT_CC_analysis()’) for the AC analysis as follows:

Figure 3.33 A CC amplifier (emitter follower) and its PSpice simulation results (“elec03e11.opj”).

This AC analysis can also be done by using the above MATLAB function ‘BJT_CC_analysis()’ although the results will be slightly different since ro is taken into consideration:

>>VCC=15; Vsm=0.001; rb=0; betaF=100; betaR=1; betaAC=betaF;Rs=2e4; R1=345e3; R2=476e3; RC=4e3; RE=5.94e3; RL=1e3;BJT_CC_analysis(VCC,rb,Rs,R1,R2,RC,RE,RL,[betaF,betaR,betaAC],Vsm);

If the CC circuit is biased by a current source of IEQ = 1 mA, run the MATLAB function ‘BJT_CC_analysis_I()’ as

>>IEQ=0.001; RB=parallel_comb([R1 R2]);BJT_CC_analysis_I(Rs,RB,RC,RE,RL,IEQ,[betaAC rb]); % Alternative

Running the above MATLAB statements yields

Results of analysis using the PWL modelwith betaF= 100, betaR= 1.0and R1= 345.00[kOhm], R2= 476.00[kOhm], RC= 4000[Ohm], RE= 5940[Ohm]VCC VEE VBB VBQ VEQ VCQ IBQ IEQ ICQ15.00 0.00 8.70 6.70 6.00 11.00 1.00e-05 1.01e-03 1.00e-03in the forward-active mode with VCE,Q= 5.00[V]where beta_forced = ICQ/IBQ = 100.00 with beta = 100.00gm= 38.669[mS], rbe= 2586[Ohm], ro= 10003.67[kOhm]Ri= 61.606 kOhm, Ro= 199 OhmGv=Ri/(Rs+Ri)xAv= 0.755 x 0.97 = 0.73

function [Av,Ai,Ri,Ro,gm,rbe,ro,vsm,vom]=...BJT_CC_analysis_I(Rs,RB,RC,RE,RL,IEQ,beta,VA,T,vbem)% To analyze CC amplifier given IEQ% beta = [beta rb] if a nonzero base resistance is given.% If the 10th input argument vbem (maximum vbe such that the BJT operated% in the linear region) is given, the following outputs will be returned.% vsm = Max amplitude of vs ensuring the linear operation of BJT.% vom = Max amplitude of vo when the BJT operates in the linear operation.% Copyleft: Won Y. Yang, [email protected], CAU for academic use onlyif nargin<9, T=27; end % Ambient temperatureif nargin<8, VA=1e4; end % Early voltageif length(RB)>1, RB=parallel_comb(RB); endif length(beta)>1, rb=beta(2); beta=beta(1); else rb=0; end% If there is no RB/RE, they must be given as very large values like 1e10.if sum([Rs RB RC RE RL rb]<0), error('Resistance must be positive!'); endICQ = IEQ*beta/(beta+1); % Collector current at the bias point[gm,rbe,re,ro]=gmrbero_BJT(ICQ,beta,VA,T);RsB=parallel_comb([Rs RB]); REL=parallel_comb([RE RL]);RbeEL = rb+rbe+(beta+1)*REL;Ri=parallel_comb([RB RbeEL]); % Eq. (3.2.5)Ro=parallel_comb([RE (RsB+rbe)/(beta+1)]); % Eq. (3.2.8)Ai = (beta+1)*RB*RE/((RB+rbe)*(RE+RL)+(beta+1)*RE*RL); % Eq. (3.2.6)Av = REL/(re+REL); % Eq. (3.2.7)Gv = Av/(Rs/Ri+1); % Considering Rsif nargout<1fprintf(' gm=ICQ/VT=%8.3f[mS], re=1/gm=%6.0f[Ohm], rbe=beta/gm=%6.0f[Ohm], ro=VA/ICQ=%7.2f[kOhm] ', gm*1e3,re,rbe,ro/1e3);fprintf(' Ri=RB||{rbe+(beta+1)(RE||RL)}=%9.2f kOhm,Ro=RE||[{(Rs||RB)+rbe}/(beta+1)]=%6.0f Ohm', Ri/1e3,Ro);fprintf(' Av=(RE||RL)/(re+(RE||RL))=%8.3f, Gv=Ri/(Rs+Ri)xAv =%5.3f xAv =%8.3f ', Av,Ri/(Rs+Ri),Gv);endif nargin<10, vbem = NaN; endvsm = (Rs/Ri+1)*RbeEL/rbe*vbem; vom = Gv*vsm;

These values of Ri and Gv are close to the PSpice simulation results shown in Figure 3.33(b2):

As listed above, we have the MATLAB function ‘BJT_CC_analysis_I()’, which can be used for the AC analysis of a CC circuit biased by a DC current source IE,Q.

3.2.3 Common‐Base (CB) Amplifier

Figure 3.34.1 shows a CB amplifier and its low‐frequency AC equivalent where the BJT has been replaced by the equivalent in Figure 3.18(b) and the BJT output resistance ro is assumed to be so large as to be negligible as a parallel resistor. Let us find the input resistance, current gain, voltage gain, and output resistance.

- Input Resistance Ri

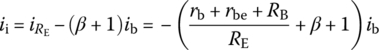

To find the input resistance from the relationship between vi = ve and ii, we apply KCL at node c to write

Figure 3.34.1 A CB (common‐base) BJT circuit and its low‐frequency AC equivalent.

Thus, we can find the input resistance as

This input resistance is very small compared with that (Eq. (3.2.1)) of CE amplifier and that (Eq. (3.2.5)) of CC amplifier.

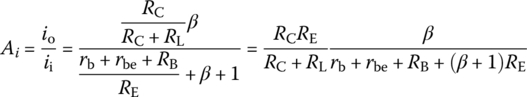

- Current Gain Ai

The current

through the emitter resistor RE can be expressed in terms of the base current ib through rbe‐rb‐RB (connected in parallel with RE) as

through the emitter resistor RE can be expressed in terms of the base current ib through rbe‐rb‐RB (connected in parallel with RE) as

Applying KCL at node e yields the expression of the input current ii in terms of ib as

The output current io through the load resistor RL can be expressed as

Thus, the current gain, i.e. the ratio of the output current io to the input current ii is

- Voltage Gains Gvand Av

To find the voltage gain Av = vo/vi (with Rs = 0), we apply KCL at node c (of the circuit in Figure 3.34.1(b)) to write the node equation and solve it as

The overall voltage gain, i.e. the ratio of the output voltage vo to the source voltage vs is

where Ri is given by Eq. (3.2.9).

function [VBQ,VEQ,VCQ,IBQ,IEQ,ICQ,Av,Ai,Ri,Ro,gm,rbe,ro]=...BJT_CB_analysis(VCC,rb,Rs,R1,R2,RC,RE,RL,beta,Vsm,VA,T)% R1,R2 can be replaced by VBB,RB if VBB-RB is connected to the base.% If beta=[betaF betaR betaAC], large-signal model-based analysis% If beta=[betaF betaR betaAC Is], the exponential model-based analysis% Copyleft: Won Y. Yang, [email protected], CAU for academic use onlyif nargin<12, T=27; end % Ambient temperatureif nargin<11, VA=1e4; end % Early voltageif sum([rb Rs R1 R2 RC RE RL]<0), error('Resistance must be positive!'); endl_beta=length(beta);if l_beta<3, betaAC=bF(1); bF=beta; % beta=[betaF betaR]else betaAC=beta(3); bF=beta(1:2); % beta=[betaF betaR betaAC ..]if l_beta>3, bF=[bF beta(4)]; end % beta=[betaF betaR betaAC Is]end[VBQ,VEQ,VCQ,IBQ,IEQ,ICQ,mode]=BJT_DC_analysis(VCC,R1,R2,RC,RE,bF);if strcmp(mode,'forward-active')==0fprintf(' AC analysis is impossible in BJT_CB_analysis()because the BJT is in the saturation mode! ');Av=NaN; Ai=NaN; Ri=NaN; Ro=NaN; gm=NaN; rbe=NaN; ro=NaN; return;endRE1=RE(1);if R1>20, RB=parallel_comb([R1 R2]); else RB=R2; end % R1=VBB?[gm,rbe,re,ro]=gmrbero_BJT(ICQ,betaAC,VA,T);RCL=parallel_comb([RC RL]); RbeB=rb+rbe+RB;Av=(1/ro+betaAC/RbeB)/(1/ro+1/RCL); % Eq. (3.2.11a)Ri = parallel_comb([RE1 RbeB/(betaAC+1)]); % Eq. (3.2.9)ro1=ro+parallel_comb([Rs RE1 RbeB])*(1+betaAC/RbeB*ro);Ro = parallel_comb([RC ro1]); % Eq. (3.2.12)Ai = betaAC*RC*RE1/(RC+RL)/(RbeB+(betaAC+1)*RE1); % Eq. (3.2.10)Gv = Av/(Rs/Ri+1); % Eq. (3.2.11b)if nargin>9 & abs(Vsm)>0 % Detailed AC analysisIbm = Vsm/Rs/RbeB/(1/Rs+1/RE1+(betaAC+1)/RbeB); % Eq. (3.1.38)if Ibm>=IBQ, fprintf(' Possibly crash into the cutoff region ');endif abs(Gv*Vsm+RbeB*Ibm)>=VCQ-VEQ-0.2 % Eq. (3.1.39)fprintf(' Possibly violate the saturation region ');endendfprintf(' gm=%8.3f[mS], rbe=%6.0f[Ohm], ro=%7.2f[kOhm] ',gm*1e3,rbe, ro/1e3)fprintf(' Ri=%9.3f[kOhm], Ro=%6.0f[Ohm] Gv=Ri/(Rs+Ri)xAv=%7.3f x%8.2f=%8.2f ', Ri/1e3,Ro,1/(Rs/Ri+1),Av,Gv);

Figure 3.34.2 To find output resistance Ro of the CB circuit.

- Output Resistance Ro

To find the equivalent resistance seen from the load side, we remove the (independent) voltage source vs by short‐circuiting it, make a I‐to‐V source transformation of the dependent current source βib into the voltage source βibro in series with ro as shown in Figure 3.34.2. Then we apply a test current source of iT = 1 A and find the voltage across it:

This process for analyzing a CB amplifier to find their input/output resistances and voltage/current gains has been cast into the above MATLAB function ‘

BJT_CB_analysis()’ and the following one ‘BJT_CB_analysis_I()’ for the case where the amplifier is excited by current source.

function [Av,Ai,Ri,Ro,gm,rbe,ro,vsm,vom]=...BJT_CB_analysis_I(Rs,RB,RC,RE,RL,IEQ,beta,VA,T,vbem)% To analyze CB amplifier given IEQ% beta = [beta rb] if a nonzero base resistance is given.% If the 10th input argument vbem (maximum vbe such that the BJT operated% in the linear region) is given, the following outputs will be returned.% vsm = Max amplitude of vs ensuring the linear operation of BJT.% vom = Max amplitude of vo when the BJT operates in linear operation.% Copyleft: Won Y. Yang, [email protected], CAU for academic useif nargin<9, T=27; end % Ambient temperatureif nargin<8, VA=1e4; end % Early voltageif length(RB)>1, RB=parallel_comb(RB); endif length(beta)>1, rb=beta(2); beta=beta(1); else rb=0; end% If there is no RB/RE, they must be given as very large values like 1e10.if sum([Rs RB RC RE RL rb]<0), error('Resistance must be positive!'); endICQ = IEQ*beta/(beta+1); % Collector current at the bias point[gm,rbe,re,ro]=gmrbero_BJT(ICQ,beta,VA,T);RbeB=rb+rbe+RB; RE1=RE(1);Ri = parallel_comb([RE1 RbeB/(beta+1)]); % Eq. (3.2.9)%Ro = parallel_comb([RC ro]); % Eq. (3.2.12)ro1= ro+parallel_comb([Rs RE RbeB])*(1+beta/RbeB*ro);Ro = parallel_comb([RC ro1]); % Eq. (3.2.12)Ai = beta*RC*RE/(RC+RL)/(RB+rbe+(beta+1)*RE1); % Eq. (3.2.10)Avo= beta*Ro/RbeB; % Eq. (3.2.11a) with no RLAv = Avo/(Ro/RL+1); % Eq. (3.2.3) considering RLGv = Av/(Rs/Ri+1); % Eq. (3.2.11b) Considering Rsif nargout<1fprintf(' gm=ICQ/VT=%8.3f[mS],re=1/gm=%6.0f[Ohm],rbe=beta/gm=%6.0f[Ohm], ro=VA/ICQ=%7.2f[kOhm] ', gm*1e3,re,rbe,ro/1e3);fprintf(' Ri=RE||{(RB+rbe)/(beta+1)}=%9.3f kOhm, Ro=RC||ro=%6.0f88Ohm', Ri/1e3,Ro);fprintf(' Av=-alpha*Ro/(re+RE)xRL/(Ro+RL)=%8.2f x%5.2f =%8.2f,Gv=Ri/(Rs+Ri)xAv =%5.3f xAv =%8.2f ', vo,RL/(Ro+RL),Av,Ri/(Rs+Ri),Gv);endif nargin>9, vsm=(Rs+Ri)/re*vbem; vom=Gv*vsm;else vsm=NaN; vom=NaN; end

Example 3.12 AC Analysis of CB Amplifier

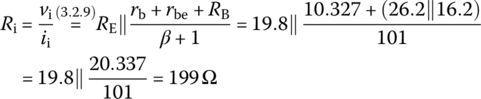

Consider the CB circuit in Figure 3.35(a) where VCC = 15 V, rb = 0 Ω, Rs = 1 kΩ, R1 = 26.2 kΩ, R2 = 16.2 kΩ, RC = 10 kΩ, RE = 19.8 Ω, RL = 10 kΩ, βF = 100, βR = 1, βAC = 100, and VA = 104 V. Find Ri, Ro, Av = vo/vi, and Gv = vo/vs, and compare their values with those obtained from PSpice simulation.

We can use the values of rbe = 10 327 Ω and ro = 399.47 kΩ (obtained by using the MATLAB function ‘BJT_DC_analysis()’ and ‘gmrbero_BJT()’) for the AC analysis as follows:

Figure 3.35 A CB circuit and its PSpice simulation results (“elec03e12.opj”).

This AC analysis can also be done by using the above MATLAB function ‘BJT_CB_analysis()’ although the results will be slightly different since ro is taken into consideration:

>>VCC=15; Vsm=0.001; rb=0; betaF=100; betaR=1; betaAC=betaF;Rs=1e3; R1=26.2e3; R2=16.2e3; RC=10e3; RE=19.8e3; RL=1e4;BJT_CB_analysis(VCC,rb,Rs,R1,R2,RC,RE,RL,[betaF,betaR,betaAC],Vsm);

If the CB circuit is biased by a current source of IEQ = 251 μA, run the MATLAB function ‘BJT_CB_analysis()’ with IEQ and RB=R1||R2 in place of R1 and R2 or ‘BJT_CB_analysis_I()’ as follows:

>>IEQ=253e-6; RB=parallel_comb([R1 R2]); % AlternativeBJT_CB_analysis_I(Rs,RB,RC,RE,RL,IEQ,[betaAC rb]); % Another alternative

Running these MATLAB statements yields

Results of analysis using the PWL modelwith betaF= 100, betaR= 1.0and R1= 26.20[kOhm], R2= 16.20[kOhm], RC= 10000[Ohm], RE= 19800[Ohm]VCC VEE VBB VBQ VEQ VCQ IBQ IEQ ICQ15.00 0.00 5.73 5.71 5.01 12.50 2.50e-06 2.53e-04 2.50e-04in the forward-active mode with VCE,Q= 7.49[V]where beta_forced = ICQ/IBQ = 100.00 with beta = 100.00gm= 9.684[mS], rbe= 10327[Ohm], ro= 39947.48[kOhm]Ri= 0.199kOhm, Ro= 10000OhmGv=Ri/(Rs+Ri)xAv= 0.166 x 24.58 = 4.09

These values of Ri, Ro, and Gv are close to the PSpice simulation results shown in Figure 3.35(b2) and (c2):

where in Figure 3.35(b2), an AC (sine‐wave) voltage source of 1 mV is applied at the output terminal to find the output resistance Ro from the voltage‐current relationship:

The next section will show how the MATLAB functions presented above can be used to analyze a multistage amplifier.

3.2.4 Multistage Cascaded BJT Amplifier

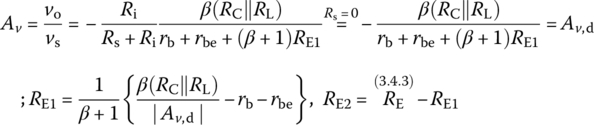

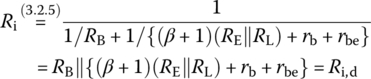

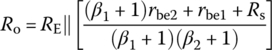

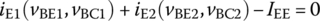

Table 3.3 lists the formulas for finding the input/output resistances, voltage gain, and current gain of the CE/CC/CB amplifiers.

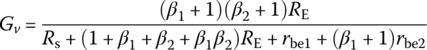

Note that to find the input/output resistance of a CC configuration requires the input/output resistance of the next/previous stage corresponding to its load/source resistance RL/Rs as implied by Eq. (3.2.5)/(3.2.8). That is why, for a systematic analysis of a multistage amplifier containing one or more CC configurations, we should find the input/output resistance of each stage, starting from the last/first stage backwards/forwards to the first/last stage where the load resistance to each stage except the last one is the input resistance of the next stage and the source resistance to each stage except the first one is the output resistance of the previous stage.

Table 3.3 Characteristics of Common‐Emitter/Common‐Collector/Common‐Base (CE/CC/CB) amplifiers.

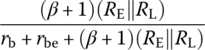

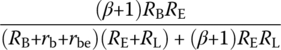

| CE | CC | CB | |

| Ri | RB||{rb + rbe + (β + 1)RE1} (3.2.1) |

RB||{rb + rbe + (β+1)(RE||RL)} (3.2.5) | |

| Ro | RC||ro ≈ RC (3.2.4) | RC‖ro1 (3.2.12) | |

| Av |  (3.2.3) (3.2.3) |

() () |

|

| Ai |  (3.2.6) (3.2.6) |

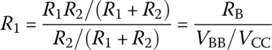

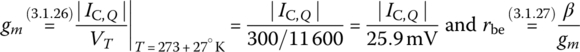

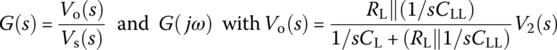

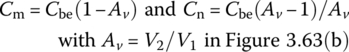

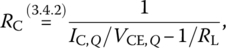

function [Av,Avo,Gv,Ri,Ro]=Av_CE(ro_,RE_,RC_)% Put 1 as the 1st input argument ro_ if ro~=inf.% Put 0 as the 2nd input argument RE_ if RE=0.% Put 0 as the 3rd input argument RC_ if RC=inf.syms b rb rbe ro Rs RB RC RE RLif nargin>1&RE_==0, RE=0; endif nargin>2&RC_==0, RC=inf; endRCL=parallel_comb([RC RL]); vi=1;if nargin>0&ro_>0,if RE==0Ri=parallel_comb([RB rbe]); Av=-b/rbe*parallel_comb([ro RCL]);elseY=[(b+1)/rbe+1/RE+1/ro -1/ro;-1/ro-b/rbe 1/ro+1/RCL];vec=Y[(b+1)/rbe; -b/rbe]; ve=vec(1); vc=vec(2);ib=(vi-ve)/rbe; Ri=parallel_comb([RB vi/ib]); Av=vc;endelsero=inf; rbeRE=rbe+(b+1)*RE;Ri=parallel_comb([RB rbeRE]); % Eq. (3.2.1)Av=-b*RCL/rbeRE; % Eq. (3.2.3)endRo=parallel_comb([RC ro]); % Eq. (3.2.4)Avi=1/(Rs/Ri+1); AvL=1/(Ro/RL+1);Avo=Av/AvL; %Avo=-b*RC/(rbe+(b+1)*RE);if nargout<1, fprintf(' Av = '); pretty(simplify(Av)); end

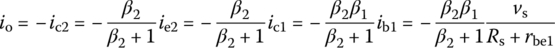

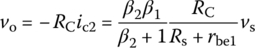

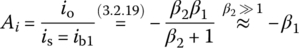

function Ri=Ri_CE(ro_,RE_,RC_)% Put 1 as the 1st input argument ro_ if ro~=inf.% Put 0 as the 2nd input argument RE_ if RE=0.% Put 0 as the 3rd input argument RC_ if RC=inf.if nargin>2, [Av,Avo,Gv,Ri]=Av_CE(ro_,RE_,RC_);elseif nargin>1, [Av,Avo,Gv,Ri]=Av_CE(ro_,RE_);elseif nargin>0, [Av,Avo,Gv,Ri]=Av_CE(ro_);else [Av,Avo,Gv,Ri]=Av_CE;endfunction Ro=Ro_CE(ro_)% Put 1 as the 1st input argument ro_ if ro~=inf.syms ro RCif nargin<1|ro_==0, ro=inf; endRo=parallel_comb([RC ro]); % Eq. (3.2.4)if nargout<1, fprintf(' Ro = '); pretty(simplify(Ro)); end