4

FET Circuits

4.1 Field‐Effect Transistor (FET)

As the Bipolar Junction Transistor (BJT) with three terminals, each called the base B, collector C, and emitter E, the Field‐Effect Transistor (FET) is also a semiconductor device with three terminals, each called the gate G, drain D, and source S. In contrast with the BJT that operates with both types of charge carriers, holes and electrons, the FET is a ‘unipolar’ device that works with only one type of carriers, holes or electrons. While the BJT can basically be modeled as a current‐controlled current source (in the forward‐active region) since its collector current iC depends on its base current iB, the FET can basically be modeled as a voltage(field)‐controlled current source (in the saturation region) since its drain current iD depends on its gate‐to‐source voltage vGS. Table 4.1 shows a rough comparison between BJTs and FETs.

Table 4.1 BJT versus FET.

| FET (Field Effect Transistor) | BJT (Bipolar Junction Transistor) | |

| Voltage‐operated device | Current‐operated device | |

| Input resistance | Large | Small in CE/CB configurations |

| Output resistance | Large | Small |

| Power dissipation | Low | High |

| Noise | Low | Medium |

| Switching time | Very fast | Fast |

| Robustness to static charge | Low (more destructible) | High |

| Thermal stability | Better | |

| Fabricability | FET can be more easily fabricated with higher density in a smaller space. It can also be connected as R or C, which makes possible the design of systems consisting of only FETs with no other elements. | |

Two types of FET are most widely used, junction‐gate device called JFET (Junction FET) and insulated‐gate device called MOSFET (Metal‐Oxide‐Semiconductor FET).

4.1.1 JFET (Junction FET)

There are two basic configurations of junction field effect transistor, the n‐channel JFET and the p‐channel JFET. As shown in Figures 4.1.1 and 4.1.2, an n/p‐channel JFET consists of a lightly doped n/p‐type semiconductor channel and a highly doped P(P+)/N(N+)‐type semiconductor gate. Figure 4.2(a) and (b) show typical drain (output) and transfer characteristic curves of a JFET, respectively. There are three regions (operation modes) besides the breakdown region:

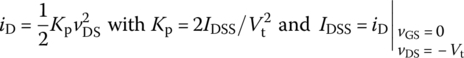

- Ohmic (Triode) region

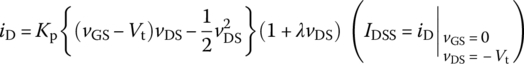

When 0 < vDS ≤ vGS

−Vt with Vt < vGS < 0 (for an n‐channel JFET), the drain current will be

Figure 4.1.1 Structure and symbol of an n‐channel

Figure 4.1.2 Structure and symbol of a p‐channel JFET.

with

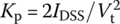

[A/V2]: transconductance coefficient or conduction parameter

[A/V2]: transconductance coefficient or conduction parameterwhere Vt [V], called the threshold, pinch‐off, or pinch‐down voltage, is such a value of vGS that the drain current iD drops to zero if vGS ≤ Vt (for an n‐channel JFET) or vGS ≥ Vt (for a p‐channel JFET). λ [V

‐1] is the channel length modulation (CLM) parameter, typically ranging from 0.005 to 0.02 V‐1, which accounts for the variation of transconductance coefficient with vDS. IDSS [A], called the drain‐to‐source saturation current or zero bias (gate voltage) drain current, is the value of the drain current at vDS =−Vt (with vGS = 0).Why is this region named ‘ohmic region’? Because the JFET in the region acts like a voltage‐controlled resistor whose resistance is determined by vGS. Since iD can be large depending on vGS even with a very low vDS, the JFET operating in this region can be viewed as a closed switch with the on‐drain resistance rDS,ON.

- Saturation (Pinch‐off) or Constant current region

When 0 ≤ vGS − Vt ≤ vDS < Vbreakdown (for an n‐channel MOSFET), the drain current is determined as

Note that the boundary between the ohmic and saturation regions plotted as a line of triangle (∇) symbols is described by

(4.1.3)

- Cutoff region

If vGS ≤ Vt (for an n‐channel JFET) or vGS ≥ Vt (for a p‐channel JFET), the leakage drain current IDS,OFF and the gate cutoff current IGSS flow between the drain/gate and the source of an FET. However, the currents are about 1 pA or less than that even under high voltage, the FET can be viewed as an open switch.

- Breakdown region

If the magnitude of the voltage across any two terminals exceeds a certain value, it may cause avalanche breakdown across the gate junction. As can be seen from the drain (output) characteristics in Figure 4.2(a), the breakdown voltage between drain and source becomes lower as the reverse‐bias gate voltage (|vGS|) increases in magnitude where the breakdown voltage BVDSS with vGS = 0 is specified in the manufacturers' datasheets.

Figure 4.2 Typical characteristics of a JFET.

Figure 4.3 Small‐signal models of FET.

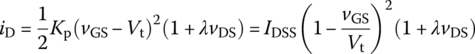

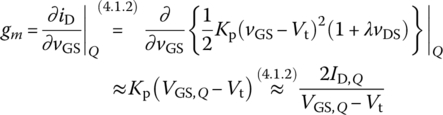

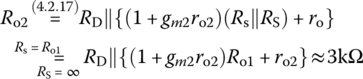

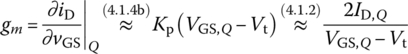

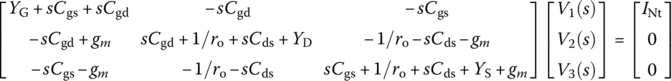

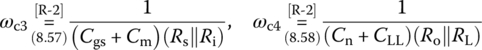

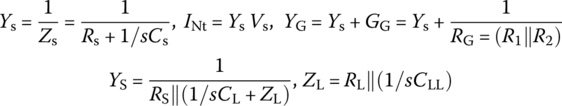

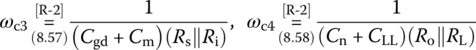

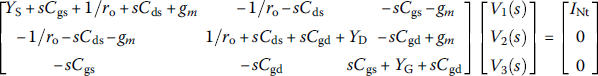

Figure 4.3(a) and (b) shows the high/low frequency small‐signal (AC) models of an FET operating in the saturation region, respectively, where ro[Ω]: incremental resistance between D and S (called the output resistance) is the reciprocal of the slope of the output characteristic (Figure 4.2(a)) at the operating (bias) point Q:

gm[S]: transconductance (gain) is the slope of the transfer characteristic (Figure 4.2(b)) at the operating point Q:

VA[V]: channel modulation voltage or Early voltage normally in the range of 20 ~ 200 V

Note that the parameters KP, lambda, Vto, Cgd, and Cgs of the PSpice model for a JFET represent Kp, λ, Vt, Cgd, and Cgs, respectively, as can be seen from the PSpice Model Editor window (opened by selecting the device and clicking on Edit > PSpice:Model from the top menu bar in the Schematic Window) or the PSpice simulation output file. Also, the operating point information in the PSpice simulation output file obtained from the Bias Point analysis shows the parameters GM and GDS, each representing gm and 1/ro.

Let us consider the JFET circuit of Figure 4.4(a1) where the voltage appearing across RS is fed back to bias the JFET. Note that RS should be chosen large enough to make vGS < 0 so that the gate‐channel(source) junction can be reverse‐biased for normal operation. To analyze this circuit, let us apply Kirchhoff's voltage law (KVL) to the G‐S loop to write the load line equation and solve it to find iD as

Then, assuming that the FET will be in the saturation region, we equate this to the drain current Eq. (4.1.2) with λ ≈ 0:

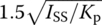

where vG = 0, RD = 1 kΩ, RS = 500 Ω, VDD = 10 V, VSS = −1 V, Kp = 2.608 × 10‐3 A/V2, Vt = −3 V, and IDSS = ![]() . We solve Eq. (4.1.6) to find VGS,Q =

. We solve Eq. (4.1.6) to find VGS,Q = −1.17 V and substitute it for vGS into Eq. (4.1.5) to get ID,Q = 4.35 mA, which is supported by the operating point Q = (VGS,Q, ID,Q) = (‐1.17 V, 4.35 mA) obtained from the load line analysis shown in Figure 4.4(b). We can substitute ID,Q = 4.35 mA into the KVL equation for the D‐S loop to find VDS,Q:

Figure 4.4 DC analysis of a JFET circuit

These computations can be done by running the following MATLAB statements:

>>vG=0; RD=1000; RS=500; VDD=10; VSS=-1; Kp=2.608e-3;Vt=-3; IDSS=Kp/2*Vt^2>>x=roots([Kp/2 1/RS-Kp*Vt Kp/2*Vt^2+(VSS-vG)/RS]); % Eq. (4.1.6)>>VGSQ=x(find((Vt<x&x<vG-VSS)|(Vt>x&x>vG-VSS)))VGSQ = -1.1740>>IDQ=(vG-VSS-VGSQ)/RS % Eq. (4.1.5)IDQ = 0.0043>>VDSQ=VDD-VSS-(RD+RS)*IDQ % Eq. (4.1.7)VDSQ = 4.4780

As an alternative, the MATLAB function ‘FET_DC_analysis()’ (that was made to analyze the standard FET biasing circuits using a voltage divider as depicted in Figure 4.4(a2)) can be used as follows:

>>R1=1e12; R2=1e5; [VGQ,VSQ,VDQ,VGSQ,VDSQ,IDQ,mode]=...FET_DC_analysis([VDD VSS],R1,R2,RD,RS,Kp,Vt);Analysis ResultsVDD VGQ VSQ VDQ IDQ10.00 0.00 1.17 5.65 4.35e-003in the saturation mode

Here, note the following:

- One of the two roots of the quadratic Eq. (4.1.6) between Vt and vG

‐VSS should be selected (see Figure 4.2(b)):(4.1.8a) (4.1.8b)

(4.1.8b)

If neither of them turns out to be inside the interval [Vt, vG−VSS], the JFET must be in the cutoff region.

- In order for the above analysis result to be valid, the operating point should be in the saturation region since we have used Eq. (4.1.2) on the assumption that the JFET is saturated. This condition can be assured by checking if the following inequality is satisfied:

(4.1.9a)

(4.1.9b)

(4.1.9b)

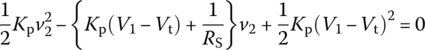

Now, let us consider a question: “What if neither of the two roots of Eq. (4.1.6) satisfies this inequality?” In this case, the JFET must operate in the ohmic region where the circuit can be analyzed by finding the solution of Eq. (4.1.1) with the relations Eqs. (4.1.5) and (4.1.7) substituted for vGS and vDS, respectively:

Since this equation is also a quadratic equation, the larger one of its two roots should be taken where it is supposed to satisfy

The whole computational process of analyzing the standard n‐channel FET biasing circuit shown in Figure 4.4(a2) has been cast into the above MATLAB function ‘FET_DC_analysis()’. Likewise, the following MATLAB function ‘FET_PMOS_DC_analysis()’ has been composed to analyze typical (DC driven) p‐channel FET biasing circuits.

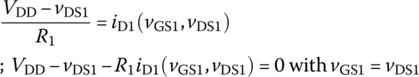

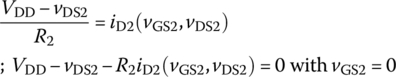

Before ending this section, let us consider how the FET analysis considering the effect of the CLM parameter λ should be performed when λ is not negligibly small where the value of the voltage vG at node G is assumed to be given in the circuit of Figure 4.4(a2). In such a case, a set of two KVL equations in vGS and vDS, one for the path GSJ‐RS‐VSS and the other for the path VDD‐RD‐DSJ‐RS‐VSS, should be solved:

where iD(vDS, vGS) is determined by Eqs. (4.1.1) or (4.1.2) depending on the operation mode of the FET and implemented by the following MATLAB function ‘iD_NMOS_at_vDS_vGS()’. This set of nonlinear equations can be solved by using the MATLAB function ‘fsolve()’ as implemented in the above modified version of ‘FET_DC_analysis0()’.

4.1.2 MOSFET (Metal‐Oxide‐Semiconductor FET)

A MOSFET, with the gate electrode insulated by an oxidized metal layer, can be fabricated to operate as either a depletion‐mode or enhancement‐mode FET. The MOSFET has a very high input resistance owing to the insulated gate. Due to the very thin gate, MOS devices can easily be damaged by ESD ( electro static discharge), requiring special precautions.

Figures 4.5.1‐4.5.5 show the basic structures and symbols of n/p‐channel enhancement and depletion types of MOSFET. Figure 4.6(a) shows typical drain (output) characteristic curves of a MOSFET, where the variables of the horizontal and vertical axes are vDS/vSD and iD/‐iD, respectively, for n/p‐channel MOSFETs. Figure 4.6(b) shows typical transfer characteristic curves of n/p‐channel enhancement and depletion types of MOSFET, where the sign of the threshold (gate) voltage Vt for n/p‐channel is +/‐ or ‐/+ depending on whether the type of MOSFET is enhancement or depletion. Note that the voltage polarities and current directions for an n‐channel MOSFET (NMOS) and a p‐channel MOSFET (PMOS) are opposite to each other.

Figure 4.5.1 Structure and NMOS (n‐channel MOSFET).

Figure 4.5.2 Structure and symbol of an n‐channel enhancement MOSFET (NMOS).

Figure 4.5.3 Structure and symbol of a p‐channel enhancement MOSFET (PMOS).

Figure 4.5.4 Structure and symbol of an n‐channel depletion MOSFET (d‐NMOS).

Figure 4.5.5 Structure and symbol of a p‐channel depletion MOSFET (d‐PMOS).

Figure 4.6 Typical characteristics of a MOSFET.

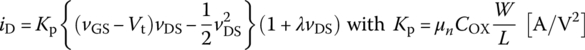

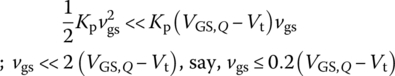

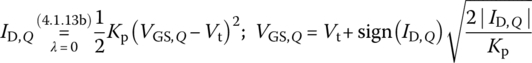

As depicted in Figure 4.6(a), there are three regions (operation modes) besides the breakdown region. Since the operational characteristics of depletion‐type MOSFETs (d‐MOSFETs) are the same with JFETs, we are going to look over the characteristics of enhancement‐mode MOSFETs (e‐MOSFETs) only:

- Ohmic (Triode) region

When 0 < vDS ≤ vGS

−Vt with |Vt| < |vGS| (for an NMOS), the drain current is determined aswhere Kp[A/V2]: conduction parameter or transconductance coefficient, μn[m2/V/s]: mobility of electrons or positive holes in the channel, COX [F/m2]: gate‐to‐channel capacitance per unit area due to the gate oxide, L/W: aspect ratio with length L and width W of the channel, λ [V

‐1]: channel length modulation (CLM) parameter - Saturation (Pinch‐off) or Constant current region

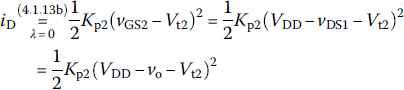

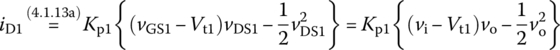

When 0 ≤ vGS

‐Vt ≤ vDS < Vbreakdown (for an NMOS), the drain current is determined asThe boundary between the ohmic and saturation regions (with vDS = vGS

‐Vt) is described by - Cutoff region

If vGS ≤ Vt (for an NMOS) or vGS ≥ Vt (for a PMOS), the MOSFET will be cut off like an open switch.

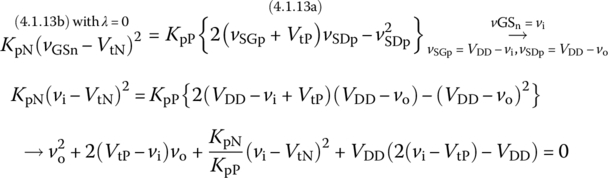

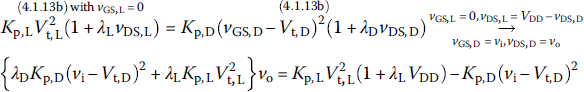

Note that Eqs. (4.1.1) and (4.1.2) and Eqs. (4.1.13a) and (4.1.13b), each describing the i‐v relationships of JFET and MOSFET, are identical except for the definition of the conduction parameter Kp and that is why the above MATLAB function ‘FET_DC_analysis()’ can be used for the DC analysis of FET circuits whether the FET is a JFET or a MOSFET.

Table 4.2 summarizes the circuit symbols and i‐v relationships of JFET and MOSFET.

Table 4.2 Circuit symbols and i‐v relationships of JFET and MOSFET.

| FET type | n‐Channel | p‐Channel | ||||

| JFET | Enhancement MOSFET | Depletion MOSFET | JFET | Enhancement MOSFET | Depletion MOSFET | |

| Circuit symbols |  |

|

|

|

|

|

| Threshold voltage Vt | − | + | − | + | − | − |

| Conduction constant Kp | Process conduction parameter |

Process conduction parameter |

||||

| Turn‐on condition | vGS > Vt and vDS > 0 | vSG > |Vt| and vSD > 0 | ||||

| Triode region (Ohmic mode) | vGD = vG − vD > Vt > 0 | vDG = vD − vG > |Vt| | ||||

| Saturation region (Pinch‐off mode) | vGD = vG − vD ≤ Vt | vDG = vD − vG ≤ |Vt| | ||||

| iD ≅ Kp(vGS − Vt)2/2 | iD ≅ Kp (vSG − |Vt|)2/2(4.1.13b) | |||||

Figure 4.7 DC analysis of a MOSFET circuit.

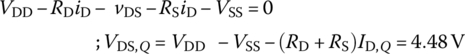

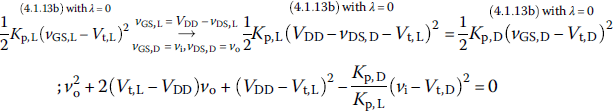

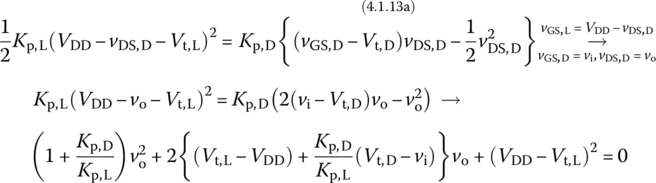

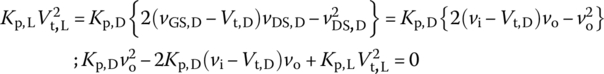

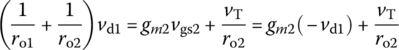

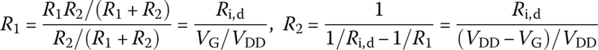

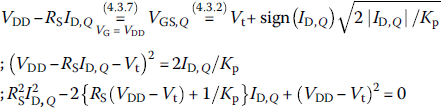

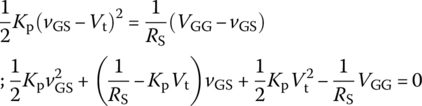

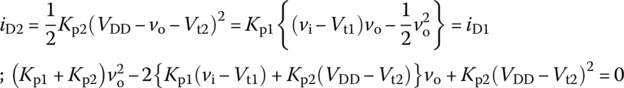

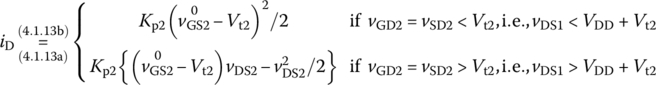

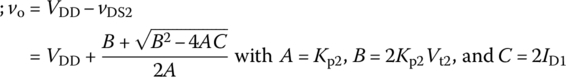

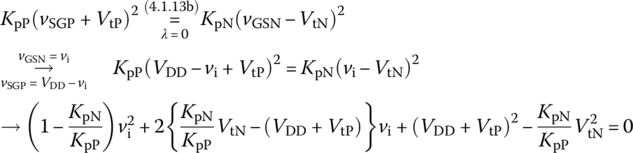

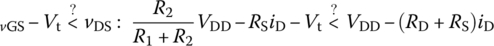

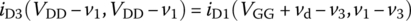

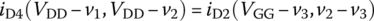

Let us consider the standard FET biasing circuit of Figure 4.7(a1) where the NMOS is biased by the voltage divider consisting of VDD‐R1‐R2. To analyze the circuit, we replace the voltage divider by its Thevenin equivalent as shown in Figure 4.7(a2) and write the following equation by equating the two expressions for the drain current, i.e. one from the KVL equation for the VGG‐GSJ‐RS loop and the other from Eq. (4.1.13b) with λ = 0 as

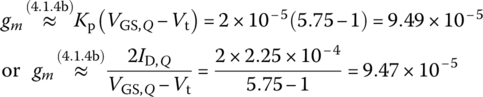

where VDD = 12 V, R1 = 4 kΩ, R2 = 8 kΩ, RD = 2 kΩ, Rs = 10 kΩ, VGG = VDDR2/(R1 + R2) = 8 V, Kp = 2 × 10‐5 A/V2, and Vt = 1 V. We solve this equation to get VGS,Q = 5.75 V and ID,Q = 0.225 mA, which conforms with the operating point Q = (VGS,Q, ID,Q) = (5.75 V, 0.225 mA) obtained from the load line analysis shown in Figure 4.7(b). Then we substitute ID,Q = 0.225 mA for iD into the KVL equation for the D‐S loop to find VDS,Q:

These hand calculations can be done by running the following MATLAB statements:

>>R1=4000; R2=8000; RD=2e3; RS=1e4; VDD=12; Kp=2e-5; Vt=1;FET_DC_analysis(VDD,R1,R2,RD,RS,Kp,Vt);

which yields

VDD VGQ VSQ VDQ IDQ12.00 8.00 2.25 11.55 2.25e-004in the saturation mode with VGD,Q= -3.55[V]<=Vt=1.00

Figure 4.8 Operating point on the iD‐vDS characteristic curve of the NMOS in Figure 4.7(a1).

If you want to locate the operating point Q = (VGS,Q, ID,Q) on the iD‐vDS characteristic curve of the NMOS M1 from the viewpoint of load line analysis, run the following MATLAB script “elec04f08.m” to get Figure 4.8.

These results can be supported by the Bias Point analysis using the PSpice. After running the OrCAD/PSpice project ‘elec04f09.opj’ with the schematic (Figure 4.9(a)), you can click PSpice > View_Output_File on the top menu bar of the Schematic window to see the simulation results shown in Figure 4.9(b). The parameters of PSpice parts MbreakN (enhancement n‐channel)/MbreakND (depletion n‐channel) (referred to as ‘NMOS’/‘NMOS_d’) can be edited as shown in the PSpice Model Editor (Figure 4.9(c1)) opened by selecting the part (to let it pink‐colored) and then clicking Edit > PSpice:Model on the top menu bar of the Schematic window.

Figure 4.9 PSpice simulation for the FET circuit of Figure 4.7(a1) with creating/editing a PSpice model.

Alternatively, you can create a new PSpice model for FET in the following steps:

- Click File > New > PSpice:Library to open the PSpice Model Editor (Figure 4.9(c2)).

- Click Model/New to open the New Model dialog box, set it as Figure 4.9(c2) and click OK to open the model list and parameter list.

- Set the model parameters as Figure 4.9(c3) where most of them are left as their default values.

- Click File/Save to save the created model into a library file in your own directory.

There is one thing to note about the transconductance gain gm, which is one of the AC model parameters for an FET. The PSpice Simulation output file (Figure 4.9(b)) shows that the value of gm(GM) is 9.49 × 10‐5, as can be computed by using Eq. (4.1.4b):

4.1.3 MOSFET Used as a Resistor

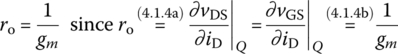

Figure 4.13(a) shows a diode‐connected e‐NMOS with its drain and gate short‐circuited. Its iD‐(vDS=vGS) characteristic can be obtained graphically as the dotted line shown in Figure 4.13(c1) from the locus of points with vDS = vGS and also mathematically by substituting vGS = vDS into Eq. (4.1.13b) (for the saturation mode):

Note that with vDS = vGS, Eq. (4.1.4a) and the reciprocal of Eq. (4.1.4b) conform with each other so that a diode‐connected e‐NMOS can be regarded as just a nonlinear resistor with the small‐signal (incremental or dynamic) resistance

Figure 4.13(a) also shows a diode‐connected d‐NMOS with its source and gate short‐circuited, whose iD‐vDS characteristic can be obtained as the dotted line shown in Figure 4.13(c2) from the locus of points with vGS = 0 where its current is limited unlike an e‐NMOS. These examples imply that a MOSFET can be used as a nonlinear resistor. The theoretical iD‐vDS characteristics of the e‐NMOS/d‐NMOS circuits turn out to agree with the PSpice simulation results shown in Figure 4.13(b).

Figure 4.13 Enhancement/depletion type MOSFETs connected as (nonlinear) resistors (“elec04f13.opj”).

4.1.4 FET Current Mirror

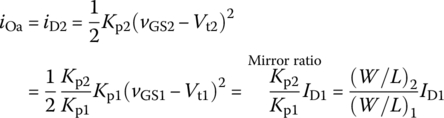

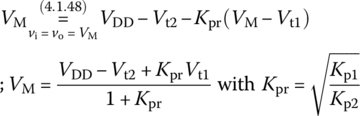

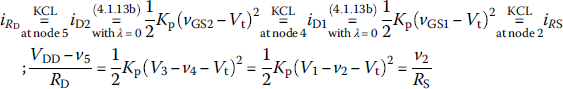

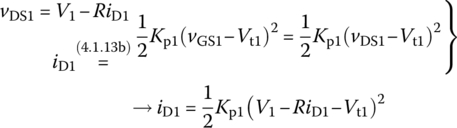

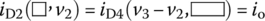

Consider the circuit of Figure 4.14(a) where the FET M1 is said to be ‘diode‐connected’ or ‘connected in diode configuration’ since its source and gate terminals are short‐circuited so that it behaves like a diode. For proper operation of the circuit, the two FETs M1 and M2 must be matched in the sense that they have identical conduction parameters Kp, threshold voltages Vt, and CLM parameters λ. Let us analyze the circuit, which is called a current mirror because the currents of the two matched FETs sharing the same vGS are equal. Noting that since vGD1 = 0 ≤ Vt, M1 (with vGS1 > 0) operates always in the saturation mode, its drain current can be determined by solving

This yields

where A = R2 = 1, B = ‐2{R(V1 − Vt1) + 1/Kp1} = ‐18, and C = (V1 − Vt1)2 = 64. Here, ID1=13.123 mA has been dumped because it does not satisfy even the turn‐on condition vGS1 = V1 − RID1 = 9 − 13.123 > Vt1 = 1[V]. Thus, since vGS1 = vGS2 and Vt1 = Vt2, the output current will be

This analysis result conforms with the PSpice simulation result (with DC Sweep analysis) shown in Figure 4.14(d). Note that considering the effect of the CLM parameter, the current transfer ratio or current gain, also called the mirror ratio, can be written as

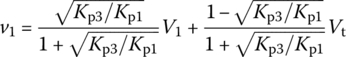

Let us analyze the circuit of Figure 4.14(b) where the three matched FETs have identical threshold voltages Vt and CLM parameters λ, but possibly different conduction parameters {Kp1, Kp2, Kp3}. Since M1 and M3 are diode connected so that vGDk = 0 ≤ Vt for k = 1 and 3, they operate always in the saturation mode (with vGSk > Vt by V1) and thus their drain currents can be expressed as

We can apply KCL at nodes 1 and 2 to write

Once we have solved this set of two nonlinear Eqs. (4.1.24a,b) for v1 and v2 (by using the MATLAB function ‘fsolve()’), we can use Eqs. (4.1.22), (4.1.23), or (4.1.13b) to find the output current iOb = iD2 as long as vGD2 = v1 − V2 < Vt so that M2 is saturated. If vGD2 = v1 − V2 ≥ Vt (so that M2 is in the tride region), Eq. (4.1.13a) should be used to find iOb, as implemented by the MATLAB function ‘iD_NMOS_at_vDS_vGS()’. This solution process for the current mirror of Figure 4.14(b) has been cast into the above MATLAB function ‘FET3_current_mirror()’.

Figure 4.14 Current mirrors using FETs (“elec04f14.opj”).

The two current mirrors of Figure 4.14(a) and (b) have the same output resistance:

Their minimum output voltage, called the compliance voltage, required to keep M2 in saturation is

To use the above function ‘FET3_current_mirror()’ for analyzing the current mirror of Figure 4.14(b), we can run the following statements:

>>Kp=1e-3; Vt=1; lambda=2e-3; R=1e3; V1=9;V2s=[0:0.01:40]; V12=[V1 V2s];[io,ID1,v,Ro,Vomin]= ...FET3_current_mirror(Kp,Vt,lambda,R,V12);plot(V2s,io, Vomin*[1 1],[0 io(end)],'r:')

to get the graph for the output current iOb versus V2 = 0 ~ 40 V like the corresponding PSpice simulation result shown in Figure 4.14(d).

To analyze the current mirror of Figure 4.14(c) with a current source I, we run

>>I=3e-3;[io,ID1,v,Ro,Vomin]= ...FET3_current_mirror(Kp,Vt,lambda,I,V12);plot(V2s,io, Vomin*[1 1],[0 io(end)],'r:')

to get the graph for the output current iOc versus V2 = 0 ~ 40 V like the corresponding PSpice simulation result shown in Figure 4.14(d).

If R = 0, it is not so difficult to derive the analytical expression of v1 even if Kp1≠ Kp3. In this case, we solve Eq. (4.1.25a) for v1 with v2=V1 and Eqs. (4.1.24a,b):

to get

The output current iOb can be determined from Eqs. (4.1.13b) or (4.1.13a) (with vGS = v1 and vDS = V2) depending on whether vGD = v1 −V2 < Vt or vGD = v1 − V2 ≥ Vt so that M2 operates in the saturation or triode region.

- (Q) What advantage does the current mirror of Figure 4.14(b) get from the additional FET M3 over that of Figure 4.14(a)?

- (A) An advantage is a considerable flexibility in the design of current source since Kp3/Kp1 can be fixed at the will of designer by adjusting the width‐to‐length ratios (Wn/Ln) of FETs.

The following MATLAB script “elec04f14.m” can be run to get the plot of the output currents iOa, iOb, and iOc versus V2 = 0 ~ 40 V for the three current mirrors shown in Figure 4.14(a‐c), as depicted in Figure 4.14(d).

4.1.5 MOSFET Inverter

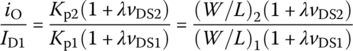

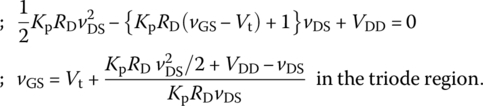

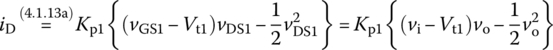

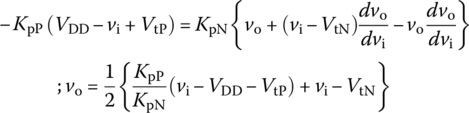

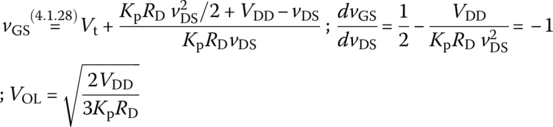

Just like the BJT inverter of Figure 3.27 introduced in Section 3.1.10, let us consider an FET inverter (shown in Figure 4.16(a)) using an FET/resistor as a driver/load, respectively. To get its voltage transfer characteristic (VTC), suppose that the input voltage vi increases from 0 to VDD. While vi = vGS ≤ Vt, the NMOS is cut off with iD = 0 so that vo = VDD. As vi = vGS > Vt, the NMOS enters the saturation region where the output voltage is determined depending on the input voltage as

When vi = vGS increases over vDS + Vt so that vGD = vGS ‐ vDS > Vt, the NMOS enters the triode region where the input–output relationship is

Figure 4.16 An NMOS inverter circuit and its VTC (“elec04f16.opj”).

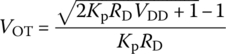

The VTC curve in Figure 4.16(b) is based on these two input–output relationships, each for saturation/triode regions. The transition point T between the saturation and triode segments on the VTC can be determined from vGD = vGS‐ vDS = vi ‐ vo = Vt together with Eq. (4.1.35). That is, we can substitute vGS = Vt + vDS into Eq. (4.1.35) to write

and use the quadratic formula to solve this quadratic equation for the point T = (VIT,VOT) as

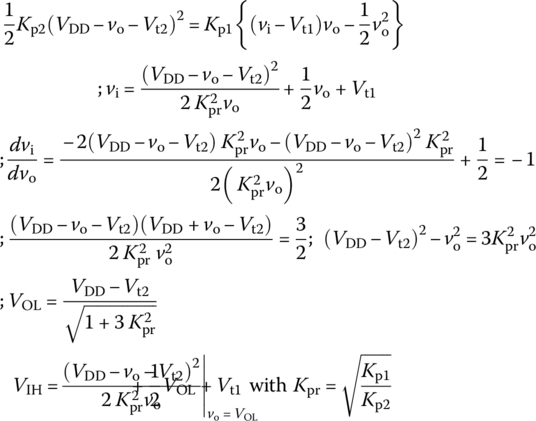

The switching threshold voltage VM, also called the midpoint voltage, can be found by substituting vGS = VM and vDS = VM into the input‐output relationship Eq. (4.1.35) (for the saturation region) and solving it for VM as

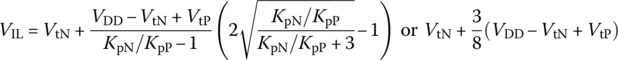

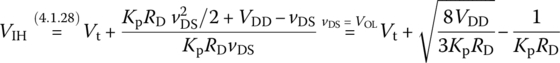

Also, VIL (the maximum input voltage that can be interpreted as “0”) (at point A in Figure 4.16(b)) and the corresponding output voltage VOH (the minimum output voltage that can be interpreted as “1”) can be determined by setting the derivative of Eq. (4.1.35) w.r.t. vGS to ‐1:

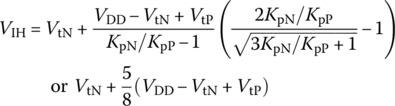

VIH (the minimum input voltage that can be interpreted as “1”) (at point B in Figure 4.16(b)) and the corresponding output voltage VOL (the maximum output voltage that can be interpreted as “0”) can be determined by setting the derivative of Eq. (4.1.37) to ‐1:

function [VIL,VIH,VOL,VOH,VM,VIT,VOT,VLH,NML,NMH,PDavg,vo1,iD1]=...NMOS_inverter(Kp,Vt,RD,VDD,vi1)% Analyze an NMOS inverter consisting of an NMOS and RD between VDD and D% to find the output vo1 to an input vi1 and plot its VTC% Vt = Threshold (Pinch-off) voltage, Kp = mu*Cox*(W/L)% vo1: Output voltage(s) for input voltage(s) vi=vi1% iD1: Drain current(s) for input voltage(s) vi=vi1% Copyleft: Won Y. Yang, [email protected], CAU for academic use onlyif nargin<5, vi1=0; enddvi=1e-3; vis=[0:dvi:VDD]; % Full range of the input viVOT=(sqrt(2*Kp*RD*VDD+1)-1)/Kp/RD; % Boundary between sat/triodeVIT=VOT+Vt; % Eq. (4.1.30)[vos,iDs]=vo_iD_NMOS_inverter(Kp,Vt,RD,VIT,VDD,vis);[VIL,VIH,VOL,VOH,VM,NML,NMH,VL,PDavg]= ...find_pars_of_inverter(vis,vos,iDs,VDD);VH=VDD; % The highest output voltageif nargin>4&sum(vi1>0&vi1<=VDD)>0 % If you want vo for vi1for i=1:length(vi1)[dmin,imin] = min(abs(vis-vi1(i)));vo1(i)=vos(imin); iD1(i)=iDs(imin);endelsevo1=vos; iD1 = iDs;endfprintf(‘ VIL=%6.3f, VIH=%6.3f, VOL=%6.3f, VOH=%6.3f, VM=%6.3f,VIT=%6.3f, VOT=%6.3f, VOE=%6.3f’, VIL,VIH,VOL,VOH,VM,VIT,VOT,VOE);fprintf(‘ Noise Margin: NM_L=%6.3f and NM_H=%6.3f’, NML,NMH);fprintf(‘ Output signal swing: VOL(%6.2f)~VOH(%6.2f) = %6.2f[V]’,VOL,VOH,VOH-VOL);fprintf(‘ Average power dissipated=%10.3e[mW] ’, PDavg*1e3);% Plot the VTC curveplot(vis,vos, [VIL VM VIH],[VOH VM VOL],’ro’)hold on, plot([Vt VIT VH],[VH VOT VL],’r^’)

function [vo,iD]=vo_iD_NMOS_inverter(Kp,Vt,RD,VIT,VDD,vi)for n=1:length(vi)if vi(n)<=Vt, vo(n)=VDD; iD(n)=0; % Cutoff regionelseif vi(n)<=VIT % Saturation regioniD(n)=Kp/2*(vi(n)-Vt).^2; vo(n)=VDD-RD*iD(n); % Eq. (4.1.35)else % Triode regiona=Kp*RD/2; b=-(Kp*RD*(vi(n)-Vt)+1); c=VDD;vo(n) = (-b-sqrt(b^2-4*a*c))/2/a; % Eq. (4.1.36)iD(n) = (VDD-vo(n))/RD;endend

Note that the high/low and absolute noise margins are defined by Eqs. (3.1.64) and (3.1.65) as

It may be useful for establishing your overview of the inverter analysis to see that the slope of the VTC (for the saturation region) is ‐KpRD (vGS – Vt) and also that the points A = (VIL,VOH), M = (VM, VM), T = (VIT, VOT), B = (VIH, VOL), and E = (VOH, VOE) on the VTC can be located on the (pink) load line intersecting the corresponding vDS‐iD characteristic curves of the NMOS in Figure 4.16(c).

The above MATLAB function ‘NMOS_inverter()’ uses another function ‘vDS_vGS_ NMOS_inverter()’ (implementing Eqs. (4.1.35) and (4.1.36)) to get the set of output voltage vo of an NMOS inverter for vi = 0 ~ VDD, uses another function ‘find_pars_of_inverter()’ (Section 3.1.10) to find the inverter parameters, and then plots the VTC of the inverter.

Example 4.5 Design of an NMOS Inverter Loaded by a Resistor

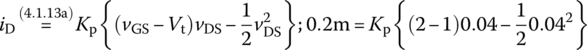

Determine the values of RD and Kp for the e‐NMOS circuit of Figure 4.16(a) so that it dissipates a power of Pmax = 0.4 mW at a low output voltage of vo,min = 0.04 V where VDD = 2 V and the device parameters of the NMOS are Vt = 1 V and λ = 0. Plot the VTC of the designed inverter.

First, from the power specification, the drain current for vo = 0.04 V can be determined as

Then, the value of RD is determined as

Now, noting that the input voltage must be as high as VDD to result in such a low output voltage as 0.04 V (in the triode region), we use Eq. (4.1.13a) to determine the value of Kp so that the drain current can be 0.2 mA for vo = vDS = 0.04 V and vi = vGS = VDD = 2 V:

You can run the following MATLAB script “elec04e05.m” to plot the VTC and get the parameters of the designed inverter.

%elec04e05.m% To solve Example 4.5VDD=2; RD=1e4; Kp=5e-3; Vt=1; % Circuit and NMOS device parameters[VIL,VIH,VOL,VOH,VM,VIT,VOT,VLH,NML,NMH,PDavg]=...NMOS_inverter(Kp,Vt,RD,VDD)

This yields the VTC as depicted in Figure 4.16(b) and the following results:

VIL= 1.020, VIH= 1.307, VOL= 0.163, VOH= 1.990, VM= 1.181NML= 0.857, NMH= 0.683, VOE= 0.040, Pavg= 0.196[mW]

Why is the value of Pavg about half of the power specification, Pmax = 0.4 mW? Because it is the average value of the power for on/off periods.

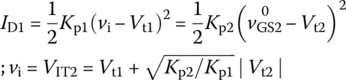

4.1.5.1 NMOS Inverter Using an Enhancement NMOS as a Load

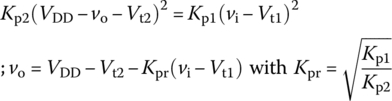

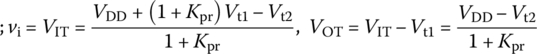

Figure 4.17(a) shows an e‐NMOS inverter, that is an NMOS inverter using a diode‐connected enhancement NMOS M2 (with its gate‐drain short‐circuited) as a load resistor where vGD2 = 0 < Vt2 so that M2 is always in saturation with the drain current (common to the two NMOSs):

Note that we can write a KVL equation in iD (for path VDD‐DS2‐DS1) or a KCL equation in vDS2 (at node S2‐D1) as

Figure 4.17 An NMOS inverter using an e‐NMOS as a load and its VTC (“elec04f17.opj”).

where the LHS of each equation corresponds to the (nonlinear) load curve (of M2 with Vt2 = 1 [V]), which is plotted as the red line together with the iD‐vDS1 characteristic curves of M1 with Vt1 = 1 [V] in Figure 4.17(b).

To get its transfer characteristic, suppose that the input voltage vi increases from 0 to VDD. While vi = vGS1 ≤ Vt1, M1 is cut off with iD = 0 so that vo = VDD ‐ vGS2 = VDD‐Vt2 since vGS2 stays at Vt2 as long as iD = 0, as described by point A in the VTC shown in Figure 4.17(c). As vi = vGS > Vt1, M1 enters the saturation region where the drain current can be expressed as

and the output voltage vo can be determined in terms of vi by equating this with Eq. (4.1.45) for iD2:

This linear saturation mode (with slope −Kpr) continues till vo becomes low enough to make vGD1 = vi − vo ≥ Vt1 so that M1 knocks on the door to the triode region, as described by point T:

If vi increases over VIT, M1 enters the triode region where the drain current can be expressed as

and the output voltage vo can be determined in terms of vi by equating Eqs. (4.1.45) and (4.1.51):

Based on these two input‐output relationships (each for the saturation/triode region), we can plot the VTC as depicted in Figure 4.17(c). The VTC can be regarded as having been obtained by taking the values of (vGS1, vDS1) at the operating points, i.e. the intersection points of the load curve of M2 with the drain characteristic curves of M1 for each value of vi = vGS1. Figure 4.17(d) shows the VTC obtained from the PSpice simulation, which is quite similar to that (Figure 4.17(c)) obtained from the theoretical analysis.

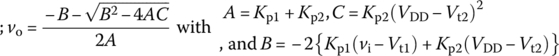

The switching threshold voltage VM, also called the midpoint voltage, can be found by substituting vi = VM and vi = VM into the input–output relationship Eq. (4.1.48) (for the saturation region) and solving it for VM as

How about VIL (the maximum input voltage that can be interpreted as “0”) and the corresponding output voltage VOH (the minimum output voltage that can be interpreted as “1”)? Unlike the case of the NMOS inverter with a resistive load, it can't be determined as a point of slope ‐1 because the slope of the VTC abruptly changes from zero to ‐Kpr. Instead, we determine (VIL, VOH) at the turn‐on point A in Figure 4.17(c):

VIH (the minimum input voltage that can be interpreted as “1”) (at point B in Figure 4.17(c)) and the corresponding output voltage VOL (the maximum output voltage that can be interpreted as “0”) can be determined by setting the derivative of dvi/dvo (rather than dvo/dvi for a technical reason) to ‐1:

The processes of using these formulas to find the parameters and plotting the VTC have been cast into the following MATLAB function ‘NMOS2e_inverter()’. To analyze the NMOS inverter of Figure 4.17(a), all you need to do is to run the following MATLAB statements:

>>VDD=6; Vt1=1; Vt2=1; Kp1=1e-3; Kp2=0.1e-3;Kp12=[Kp1 Kp2]; Vt12=[Vt1 Vt2]; NMOS2e_inverter(Kp12,Vt12,VDD);

This will yield the following analysis result and the VTC as depicted in Figure 4.17(c), which conforms with that (in Figure 4.17(d)) obtained from PSpice simulation:

VIL= 1.00, VIH= 2.39, VOL= 0.90, VOH= 5.00, VM= 1.96, VIT= 2.20, VOT= 1.20Noise Margin: NML= 0.10 and NM= 2.61, Average power = 3.330e+00[mW]

function [VIL,VIH,VOL,VOH,VM,VIT,VOT,VLH,NML,NMH,PDavg,vios]=...NMOS2e_inverter(Kp12,Vt12,VDD)% To find the parameters of an NMOS inverter with another e-NMOS as load% Kp12=[Kp1 Kp2], Vt12=[Vt1 Vt2]: Threshold (Pinch-off) voltage% Copyleft: Won Y. Yang, [email protected], CAU for academic use onlyif numel(Vt12)>1, Vt1=Vt12(1); Vt2=Vt12(2);else Vt1=Vt12; Vt2=Vt12; endif numel(Kp12)>1, Kp1=Kp12(1); Kp2=Kp12(2);else Kp1=Kp12; Kp2=Kp12; endKpr2=Kp1/Kp2; Kpr=sqrt(Kpr2);% Transition point (VIT,VOT)VOT=(VDD-Vt2)/(1+Kpr); VIT=VOT+Vt1; % Eq. (4.1.50)VIL=Vt1; VOH=VDD-Vt2; % Eq. (4.1.55a,b)VH=VOH; % Just let VH=VOH (The highest output voltage)% Cutoff Segment of VTCdv=0.001; vi_cutoff=0:dv:Vt1; vo_cutoff = VH*ones(size(vi_cutoff));Nc=numel(vi_cutoff);% Saturation Segment of VTCvi_sat = VIL:dv:VIT; % Saturation regionvo_sat = VDD-Vt2-Kpr*(vi_sat-Vt1); % Eq. (4.1.48)% Alternative to find vo_sat for saturation segment of VTCa1=1; b1=-2*(VDD-Vt2); c1=(VDD-Vt2)^2-Kpr^2*(vi_sat-Vt1).^2;vo_sat0 = -b1/2-sqrt((b1/2)^2-a1*c1); % Eq. (4.1.48)discrepancy_sat=norm(vo_sat0-vo_sat)/norm(vo_sat)% Triode Segment of VTCvi_tri=VIT:dv:VDD+1; % Triode regiona2=1+Kpr2; b2=-2*((VDD-Vt2)+Kpr2*(vi_tri-Vt1)); c2=(VDD-Vt2)^2;vo_tri = (-b2-sqrt(b2.^2-4*a2*c2))/2/a2; % Eq. (4.1.53)% Put all the segments togethervis=[vi_cutoff vi_sat vi_tri]; vos=[vo_cutoff vo_sat vo_tri];vios = [vis; vos];% To find the inverter parametersVM = (VDD-Vt2+Kpr*Vt1)/(1+Kpr); % Eq. (4.1.54)VOL = (VDD-Vt2)/sqrt(1+3*Kpr2); % Eq. (4.1.56a)VIH = (VDD-VOL-Vt2)^2/2/Kpr2/VOL + VOL/2 +Vt1; % Eq. (4.1.56b)VL = vos(ceil((VH-vis(1))/dv)); % vo to vi=VH (Virtual lowest output)NMH = VOH-VIH; NML = VIL-VOL; % Eq. (4.1.43a,b)IDD = Kp2/2*(VDD-VL-Vt2)^2;PDavg = VDD*IDD/2; % Average power for on-off periodsfprintf(' VIL=%6.3f, VIH=%6.3f, VOL=%6.3f, VOH=%6.3f, VM=%6.3f,VIT=%6.3f, VOT=%6.3f', VIL,VIH,VOL,VOH,VM,VIT,VOT);fprintf(' Noise Margin: NM_L=%6.3f and NM_H=%6.3f', NML,NMH);fprintf(' Average power = %10.3e[mW] ', PDavg*1e3);% To plot the VTCplot(vis,vos, [VIL VM VIH],[VOH VM VOL],'ro')hold on, plot([Vt1 VIT VH],[VH VOT VL],'r^')

4.1.5.2 NMOS Inverter Using a Depletion NMOS as a Load

Figure 4.18(a) shows a d‐NMOS inverter, that is an NMOS inverter using a depletion NMOS M2 (with its gate‐source short‐circuited) as a load resistor where vGS2= 0 > Vt2 so that iD2= iD1= iD is determined by vDS2=VDD‐ vDS1 = VDD‐vo as

The (nonlinear) load curve (of M2 with Vt2= −1 [V]) is plotted as the pink line together with the iD‐vDS1 characteristic curves of M1 with Vt1 = 1 [V] in (b). Note that the load curve and the iD‐vDS1 characteristic curve of M1 for vGS1 = Vt1 ‐ ![]() Vt2 = 2 are symmetric about vDS1 = VDD/2 because they can be switched to each other by substituting vDS2 = VDD

Vt2 = 2 are symmetric about vDS1 = VDD/2 because they can be switched to each other by substituting vDS2 = VDD ‐ vDS1.

To get its transfer characteristic, suppose that the input voltage vi increases from 0 to VDD. While vi = vGS1 ≤ Vt1, M1 is cut off with iD = 0 while M2 is turned on, but with vDS2 = 0 (by Eq. (4.1.57b)) so that vo = VDD ‐ vDS2 = VDD. As vi = vGS1 > Vt1, M2/M1 enter the triode/saturation region where the drain current can be expressed as

and the output voltage vo can be determined in terms of vi by equating this with Eq. (4.1.57b):

From Figure 4.18(b), we can see that during this mode, the operating point moves upward from point S (via point A) along the semiparabolic load curve. When will this mode stop and M2 enter the saturation mode? It is when vGD2 = vSD2 = vDS1‐VDD = Vt2 so that vo = vDS1 = VDD + Vt2 = VOT2. At this point T2, we have

When will this mode stop and M1 enter the triode mode? It is when vGD1 = vGS1 ‐ vDS1 = vi ‐ vo = Vt1. The output voltage vo at this point T can be determined by substituting vi = vo + Vt1 into Eq. (4.1.51) as

function [VIL,VIH,VOL,VOH,VM,VIT,VOT,VLH,NML,NMH,PDavg,vios]=...NMOS2d_inverter(Kp12,Vt12,VDD)% To find all the parameters of an NMOS inverter with a d-NMOS as load% Kp12=[Kp1 Kp2], Vt12=[Vt1 Vt2]: Threshold (Pinch-off) voltage% Copyleft: Won Y. Yang, [email protected], CAU for academic use onlyKp1=Kp12(1); Kp2=Kp12(2); Vt1=Vt12(1); Vt2=Vt12(2);Kpr2=Kp1/Kp2; Kpr=sqrt(Kpr2);% Transition point (VIT,VOT)VIT=Vt1+abs(Vt2)/Kpr; IDT=Kp2*Vt2^2/2; % Eq. (4.1.60)dv=0.001; vis=[0:dv:VIT VIT:dv:VDD];for n=1:length(vis)vi=vis(n);if vi<Vt1, iDs(n)=0; vos(n)=VDD;elseif vi<VIT % M1/M2: saturation/triode - % Eq. (4.1.59)iDs(n)=Kp1/2*(vi-Vt1)^2; A=Kp2; B=2*Kp2*Vt2; C=2*iDs(n);vDS2=(-B-sqrt(B^2-4*A*C))/2/A; %vDS2 = min(roots([A B C]));vos(n)=VDD-vDS2;elseif vi>VIT % M1/M2: triode/saturation - Eq. (4.1.63)iDs(n)=Kp2/2*Vt2^2; A=Kp1; B=2*Kp1*(Vt1-vi); C=2*iDs(n);vos(n)=(-B-sqrt(B^2-4*A*C))/2/A; %vos(n) = min(roots([A B C]));else % M1/M2: saturation/saturation - % Eqs. (4.1.60,61)iDs(n)=IDT;VOT=sqrt(2/Kp1*IDT); % Transition point of M1 between SAT/TriodeVOT2=VDD+Vt2; % Transition point of M2 between Triode/SATvos(n) = (VOT+VOT2)/2;endendvios=[vis; vos]; [VIL,VIH,VOL,VOH,VM,NML,NMH,VL,PDavg]= ...find_pars_of_inverter(vis,vos,iDs,VDD);VH=VDD; VLH=[VL VH]; % The lowest/highest output voltages% To plot the VTCplot(vis,vos, [VIL VM VIH],[VOH VM VOL],'ro')hold on, plot([Vt1 VIT VH],[VH VOT VL],'r^')

Noting that the input voltage vi at this point is the same as VIT (Eq. (4.1.60)) despite the different values of vo, we can see that when vi = VIT, vo may change abruptly between VOT and VOT2 = VDD + Vt2. The midpoint is determined as the constant value of vi along this SAT‐SAT segment:

Figure 4.18 An NMOS inverter using a d‐NMOS as a load and its VTC (“elec04f18.opj”).

As vi = vGS1 increases over VIT, M1 enters the triode region while M2 continues to be in saturation so that their drain currents can be expressed as

and the output voltage vo can be determined in terms of vi by equating these two equations:

Based on the two input‐output relationships (Eqs. (4.1.59) and (4.1.63)), we can plot the VTC as depicted in Figure 4.18(c). The process of using these formulas to plot the VTC has been cast into the above MATLAB function ‘NMOS2d_inverter()’, which uses the MATLAB function ‘find_pars_ of_inverter()’ (Section 3.1.10) to find the values of the inverter parameters such as VIL/VOH, VIH/VOL (at the two points with the slope of the VTC equal to ‐1), and VM (at the midpoint).

To analyze the NMOS inverter of Figure 4.18(a), all you need to do is to run the following MATLAB statements:

>>VDD=5; Vt1=1; Vt2=-1; Kp1=1e-3; Kp2=1e-3;Kp12=[Kp1 Kp2]; Vt12=[Vt1 Vt2]; NMOS2d_inverter(Kp12,Vt12,VDD);

This will yield the following analysis result and the VTC as depicted in Figure 4.18(c), which conforms with that (in Figure 4.18(d)) obtained from PSpice simulation:

VIL= 1.708, VIH= 2.155, VOL= 0.577, VOH= 4.706, VM= 2.000NML= 1.131, NMH= 2.551, VL= 0.127, Pavg= 1.250[mW]

Comparing Figures 4.17(c) and 4.18(c), note that the VTC of a d‐NMOS inverter has a steeper transition region and, accordingly, higher noise margins than an e‐NMOS inverter.

4.1.5.3 CMOS Inverter

Figure 4.19(a) shows a CMOS (Complementary MOSFET) inverter using NMOS and PMOS fabricated on the same chip where both gates/drains are tied to the input/output, respectively, and the sources of Mp(PMOS)/Mn(NMOS) are connected to VDD/GND, respectively. Figure 4.19(b) shows the (blue‐lined) iD‐vDSn characteristic curves of Mn depending on vGSn and the (red‐lined) iD – (vSDp = VDD‐vDSn) characteristic curves of Mp depending on vSGp = VDD ‐ vi. A rough VTC of the inverter can be plotted by connecting the operating points (vSGn = vi, vDSn = vo) {S, A, T2, T1, …}, i.e. the intersection points of the characteristic curve of Mn (for vGSn = 0~1, 1.5, 2, 2.5, 3, 3.5, and 4 ~ 5 V) with that of Mp (for vSGp = VDD‐vi = 5~4, 3.5, 3, 2.5, 2, 1.5, and 1 ~ 0 V), as illustrated in Figure 4.19(b) and (c). Figure 4.19(d) shows the VTC obtained from the PSpice simulation.

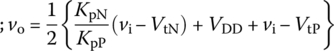

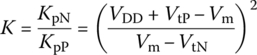

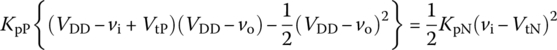

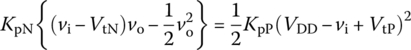

Noting from Figure 4.19(b) and (c) that the operating point moves around the five regions I, II, III, IV, and V as the input voltage vi (applied to the common gate) varies from zero to VDD, let us analyze the inverter to find out the analytical expression of the VTC together with the transition points from a region to another region where the conduction parameters and threshold (turn‐on) voltages of the PMOS/NMOS are KpP/KpN and VtP/VtN, respectively. To this aim, we start from computing the value Vm of the input voltage vi (belonging to region III) at which both Mp and Mn operate in the saturation region by equating the drain currents of Mp and Mn described by Eq. (4.1.13b) (with λ = 0 for simplicity):

Figure 4.19 A Complementary MOSFET (CMOS) inverter and its voltage transfer characteristic (VTC) (“elec04f19.opj”).

This will be used as the boundary values of vi between regions II and III or III and IV (see Figure 4.19(c)).

<Region I>

When 0 ≤ vi = vGSn ≤ VtN, Mn remains OFF while Mp conducts not in the saturation region but in the ohmic (triode) region because the off‐transistor Mn keeps Mp from conducting as much as it could with vSGp = VDD‐vi ≥ |VtP|. Since the resistance of the off‐transistor Mn is much greater than that of the on‐transistor Mp, almost the whole VDD applies to Mn so that the output voltage is vo ≈ VDD.

<Region II>

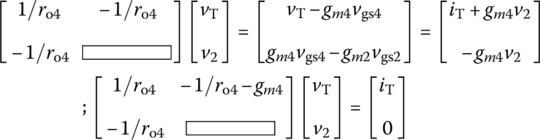

When VtN < vi ≤ Vm, Mn/Mp are assumed to be in the saturation/ohmic regions, respectively (see Figure 4.19(b)) and the operating point is computed by equating the drain currents of Mp and Mn that are described by Eqs. (4.1.13b) (with λ = 0 for simplicity) and (4.1.13a), respectively:

If the (larger) root of this quadratic equation satisfies vo > vi ‐ VtP, the assumption is right. Otherwise, i.e. if

then Mp enters the saturation region and this is region III where both Mp and Mn operate in the saturation mode. The boundary between regions II and III is denoted by the pink line corresponding to vo = vi ‐VtP in Figure 4.19(c).

<Region III>

The inverter stays in Region III (with Mp and Mn saturated) as long as the saturation condition of Mn is satisfied, i.e. if

function [VIL,VIH,VOL,VOH,Vm,VIT1,VOT1,VIT2,VOT2,VLH,NML,NMH,PDavg]=...CMOS_inverter(KNP,VtNP,VDD,Kg)% To find all the parameters of a CMOS inverter.% KNP = [KN'(WN/LN) KP'(WP/LP)]% VtNP = [VtN VtP]: Threshold (Pinch-off) voltages of NMOS/PMOS% Copyleft: Won Y. Yang, [email protected], CAU for academic use onlyif nargin<4, Kg=0; endif numel(KNP)>1, KN=KNP(1); KP=KNP(2); else KN=KNP; KP=KNP; endif numel(VtNP)>1, VtN=VtNP(1); VtP=VtNP(2); else VtN=VtNP; VtP=-VtNP; endKr2=KN/KP; Kr=sqrt(Kr2); % Ratio between conduction parameters of Mn and MpVOL=0; VOH=VDD; VH=VOH; % The lowest/highest output voltageVm=(VDD+VtP+Kr*VtN)/(1+Kr); % Eq. (4.1.65)VIT2=Vm; VOT2=Vm-VtP; VIT1=Vm; VOT1=Vm-VtN; % Boundary points of Region IIIdv=0.001; vis=[0:dv:VDD]; % Input voltage rangefor n=1:length(vis)vi=vis(n);if vi<VtN, iDs(n)=0; vos(n)=VDD; % Mn OFF, Mp in ohmic region (Region I)elseif vi<=Vm % Mn/Mp are saturation/ohmic region (Region II)B=2*(VtP-vi); C=Kr2*(vi-VtN)^2+VDD*(2*(vi-VtP)-VDD); %Eq. (4.1.66)vos(n)=(-B+sqrt(max(B^2-4*C,0)))/2; iDs(n)=KN/2*(vi-VtN)^2;elseif vi<=VDD+VtP % Mp/Mn=saturation/triode (Region IV)B=2*(VtN-vi); C=(VDD-vi+VtP)^2/Kr2; % Eq. (4.1.69)vos(n)=(-B-sqrt(max(B^2-4*C,0)))/2; iDs(n)=KP/2*(VDD-vi+VtP)^2;else iDs(n)=0; vos(n)=0; % Mn in triode region, Mp OFF (Region V)end% Here, Region III (Mp/Mn: sat) doesn't have to be taken care of% since at most only a single value of vi=Vm can belong to that region.end[VIL,VIH,VOL,VOH,VM,NML,NMH,VL,PDavg]= ...find_pars_of_inverter(vis,vos,iDs,VDD);if Kg>0subplot(221)plot(vis,vos), hold onplot([VIL VM VIH],[VOH VM VOL],'ro', [VtN VH],[VH VL],'r^')title('VTC of a CMOS inverter')subplot(222)plot(vis,iDs), title('Drain current of the CMOS inverter'), grid onend

%elec04f19.mVDD=5; VtN=1; VtP=-1; KN=1e-3; KP=1e-3;KNP=[KN KP]; VtNP=[VtN VtP];Kg=2; % To plot the graphs[VIL,VIH,VOL,VOH,Vm,VIT1,VOT1,VIT2,VOT2,VLH,NML,NMH,PDavg]=...CMOS_inverter(KNP,VtNP,VDD,Kg);

<Region IV>

If vi increases further enough to break the above condition, i.e. vo < vi ‐VtN, Mn enters the ohmic region (see Figure 4.19(b)) and the operating point is computed by equating the drain currents of Mp (in the saturation region) and Mn (in the ohmic region) that are described by Eqs. (4.1.13b) (with λ = 0 for simplicity) and (4.1.13a), respectively:

The (smaller) root of this quadratic equation will be vo as long as vi≤ vDD+VtP.

<Region V>

While Mn is still in the ohmic region, Mp will be OFF if

Then almost the whole VDD applies to Mp (with much larger resistance) so that vo ≈ 0.

The process of finding the output voltage of the CMOS inverter to the whole range of the input has been cast into the above MATLAB function ‘CMOS_inverter()’. We have run the above MATLAB script “elec04f19.m” to get not only the following values of the inverter parameters

VIL = 2.1250, VIH = 2.8750, VOL = 0.3750, VOH = 4.6250,VIT2 = 2.5000, VOT2 = 3.5000, Vm = 2.5000, VIT1 = 2.5000, VOT1 = 1.5000,NML = 1.7500, NMH = 1.7500, PDavg = 0.0028

but also the VTC and the drain current of the inverter as depicted in Figures 4.19(c) and 4.20(a), respectively. As can be seen from the VTC in Figure 4.19(c), the lowest/highest output voltage levels are 0/VDD so that the CMOS inverter has the maximum output swing. This, together with the symmetry of the VTC, is the reason why a CMOS inverter can have wide noise margins.

Figure 4.20 Drain currents of the CMOS inverter obtained from MATLAB analysis and PSpice simulation.

Figure 4.20(b) shows the drain current of the inverter obtained from the PSpice simulation, which is quite similar to Figure 4.20(a). What is implied by the current curve(s) in Figure 4.20? The current (drawn from the supply voltage source VDD) is zero when the CMOS inverter is in its output‐high/low state so that the CMOS gate can power down in its static condition, which is one of the major advantages of CMOS configuration.

One more thing to note before closing this section is that a formula to determine the geometry ratio K from the given values of VDD, Vm (the boundary value of the input voltage between regions II and III or regions III and IV), VtP (the threshold voltage of PMOS), and VtN (the threshold voltage of NMOS) can be derived from Eq. (4.1.65) as

4.1.6 Source‐Coupled Differential Pair

Figure 4.21(a) and (b) shows a source‐coupled (in the sense that the source terminals of the two FETs are connected) or differential (in the sense that its output varies with the differential input vd = vGS1‐vGS2) pair. To analyze this circuit, we assume that the two FETs have identical conduction parameters Kp and threshold voltages Vt, and both of them operate in the saturation mode so that we can use Eq. (4.1.13b) (with λ = 0 for ignoring the CLM effect) to write their approximate drain currents as

Figure 4.21 Source‐coupled (differential) pair and its VTC.

Thus, the difference between their square roots can be written as

Also, we apply KCL at node 3 (S1‐S2) to write

Subtracting the square of Eq. (4.1.73) from Eq. (4.1.74) yields

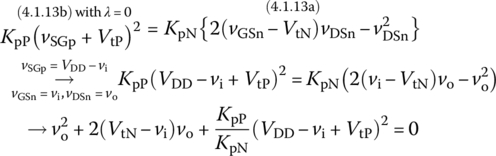

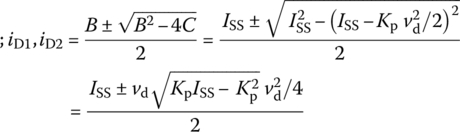

Thus, iD1 and iD2 can be found from the two roots of the quadratic equation:

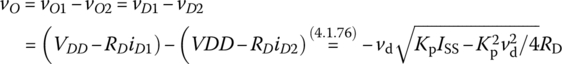

where these drain currents are depicted in Figure 4.21(b). Then we can write the (differential) output voltage as

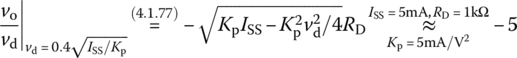

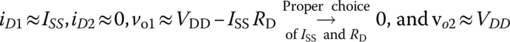

This differential output voltage vo, together with vo1 and vo2, is shown in Figure 4.21(c). From Figure 4.21 and Eqs. (4.1.76) and (4.1.77), note the following:

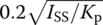

- If |vd| <

, the differential output voltage vo and other signals vary almost linearly with the differential input vd, allowing the source‐coupled pair to be used as an amplifier with a voltage gain of

(4.1.78)

, the differential output voltage vo and other signals vary almost linearly with the differential input vd, allowing the source‐coupled pair to be used as an amplifier with a voltage gain of

(4.1.78)

- If vd >

, we have

(4.1.79a)

, we have

(4.1.79a)

On the other hand, if vd < ‐1.5![]() , we have

, we have

It is implied that a large swing of the differential input vd = ±![]() makes the two FETs M1/M2 operate as a closed or an open switch, producing two distinct levels of differential output vo depending on whether vd =

makes the two FETs M1/M2 operate as a closed or an open switch, producing two distinct levels of differential output vo depending on whether vd = ![]() or vd =

or vd = ‐![]() .

.

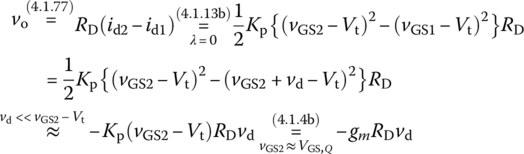

The small‐signal input‐output relationship of the differential pair can be derived by substituting Eqs. (4.1.72a,b) directly into Eq. (4.1.77):

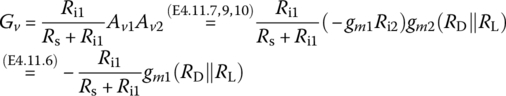

Note that the differential (mode) voltage gain ‐gmRD can be regarded as the voltage gain (Eq. (4.2.6b)) of a common‐source (CS) amplifier with RS1 = 0 and RL = ∞. Note also that if vo1 or vo2, instead of vo, is taken as the output, the differential voltage gain gmRD is halved:

The amplifying/switching properties are extensively used in analog/digital circuits, respectively. That is why the source‐coupled differential pair is one of the most important configurations employed in ICs.

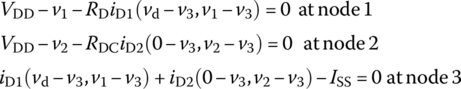

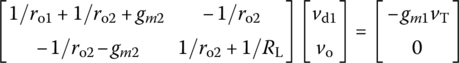

To analyze the FET differential pair circuit in Figure 4.21(a), we can apply KCL at nodes 1, 2, and 3 to write

where iDk (vGSk, vDSk) is defined by Eqs. (4.1.13a,b) as

The process of solving this set of equations to find v = [v1 v2 v3] for vd = ‐Vdm~ + Vdm and plotting vo = v1‐v2, iD1, iD2 (together with their analytic values computed by Eqs. (4.1.79) and (4.1.83)) versus vd has been cast into the following MATLAB function ‘FET_differential()’. We can run

>>Kp=5e-3; Vt=1; lambda=0; ISS=5e-3; RD=1e3; VDD=5; Vdm=1.5;dvd=Vdm/1000;vds=[-Vdm:dvd:Vdm];FET_differential(Kp,Vt,lambda,ISS,RD,VDD,vds);

to get the graphs of iD1, iD2, and vo as depicted in Figure 4.21(b) and (c).

function [vo1s,vo2s,iD1s,iD2s]= ... FET_differential(Kp,Vt,lambda,ISS,RD,VDD,vds)% Analyze an FET differential (source-coupled) pair (to find% the outputs vo1/vo2 to a range of differential input vd=-Vdm~Vdm% and plot its VTC in case of no output argument)% which consists of 2 FETs, 2 resistors RD1=RD2=RD, and an I-src ISS.% vds : Range of differential input vd% Copyleft: Won Y. Yang, [email protected], CAU for academic use onlyif nargin<6, Vdm=1.5*sqrt(ISS/Kp); dvd=Vdm/1000; vds=[-Vdm:dvd:Vdm]; end options=optimset('Display','off','Diagnostics','off');iD=@(vGS,vDS)Kp*(1+lambda*vDS).*((vGS-Vt).^2/2.*(vGS>=Vt).*(vGS-vDS<Vt)+((vGS-Vt).*vDS-vDS.^2/2).*(vGS>=Vt).*(vGS-vDS>=Vt)); % Eq. (4.1.83)id2 = vds.*sqrt(max(Kp*(ISS-Kp*vds.^2/4),0)); % Eq. (4.1.76): iD1-iD2idms=find(id2==min(id2)); idm1=idms(1); id2(1:idm1)=min(id2);idms=find(id2==max(id2)); idm2=idms(end); id2(idm2:end)=max(id2);iD1s_a=(ISS+id2)/2; iD2s_a=(ISS-id2)/2; % Eq. (4.1.76a,b)v1_a=VDD-RD*iD1s_a; v2_a=VDD-RD*iD2s_a; vo_a=v1_a-v2_a;for n=1:length(vds)vd = vds(n);eq=@(v)[VDD-v(1)-RD*iD(vd-v(3),v(1)-v(3))VDD-v(2)-RD*iD(-v(3),v(2)-v(3)) % Eq. (4.1.82)(iD(vd-v(3),v(1)-v(3))+iD(-v(3),v(2)-v(3))-ISS)*1e3];if ~exist('v'), v0=[v1_a(1) v2_a(1) v3_a(1)]; % Initial guesselse v0=v;end%Here, the first values of analytical solutions are used as the initial% guess for the numerical solution of Eq. (4.1.80) with vd(1).[v,fe]=fsolve(eq,v0,options);vo1s(n)=v(1); vo2s(n)=v(2); v3s(n)=v(3); vos(n)=v(1)-v(2); % Eq. (4.1.77)iD1s(n)=iD(vd-v(3),v(1)-v(3)); iD2s(n)=iD(-v(3),v(2)-v(3));end

4.1.7 CMOS Logic Circuits

Figure 4.22(a)‐(c) shows a two‐input CMOS NOR gate, a two‐input CMOS NAND gate, and a CMOS (bidirectional) transmission gate together with their truth tables where the substrates of the PMOS(Mp) and NMOS(Mn) are connected to the most positive/negative potentials (that are VDD/GND), respectively. The transmission gate makes possible the tristate output or wired‐or connection in CMOS circuits and can be used as building blocks for logic circuitry such as a D flip‐flop. Figure 4.23 shows a 256 × 8 bit (256 bytes) NMOS ROM chip where each one of the 256 bytes stored in the memory can be selected by the word line, which is set to High depending on the 8‐bit address code input to the 8‐input 128‐output decoder.

Here are some comparisons of CMOS and NMOS gates:

- CMOS gates have extremely high input impedance, but they are susceptible to damage.

- CMOS gates consume very little power.

- CMOS gates can achieve noise immunity amounting to 45% of the full logic swing.

- Since a CMOS gate requires more transistors than an NMOS gate having the same logic function, not only its size but also its capacitance is larger.

Figure 4.22 Various CMOS logic circuits.

4.2 FET Amplifer

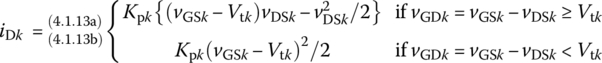

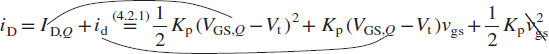

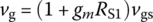

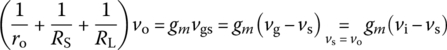

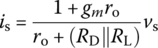

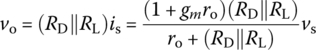

If an FET is used for the purpose of small‐signal amplification, it is supposed to be operating in the saturation region (for the range of input signal vGS = VGS,Q + vgs around VGS,Q at the bias point Q) where its drain current is expressed by

and additionally, its small‐signal component id can be approximated linearly in terms of vgs:

Figure 4.23 256 × 8 bit (256 bytes) NMOS ROM chip.

In order for this linear approximation to be valid, the last term of degree 2 must be negligibly small:

so that

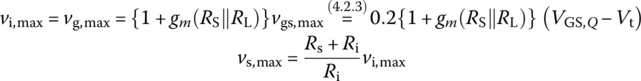

This section deals with three configurations of FET amplifier, i.e. the CS (common‐source) amplifier, the CD (common‐drain) amplifier (called a source follower), and the CG (common‐gate) amplifier.

4.2.1 Common‐Source (CS) Amplifier

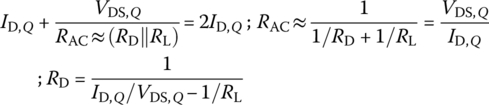

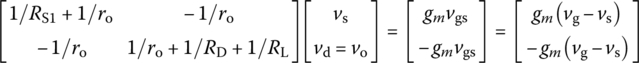

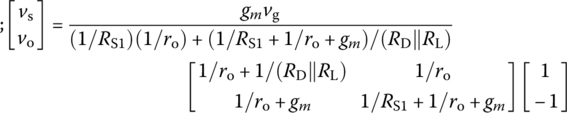

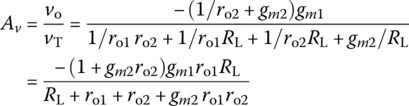

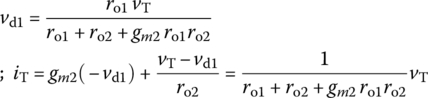

Figure 4.24 shows a CS FET amplifier and its low‐frequency AC equivalent where the FET has been replaced by the equivalent in Figure 4.3(b). Let us find the input resistance, voltage gain, and output resistance. The formulas have been implemented in the MATLAB function ‘FET_CS_analysis()’.

- Input Resistance Ri

Since the gate current of the FET is almost zero, the equivalent resistance seen from the input side (see Figure 4.24(b1)) is

Figure 4.24 A CS (common‐source) FET circuit and its low‐frequency AC equivalent.

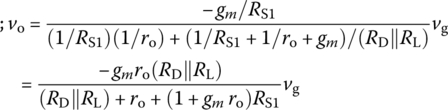

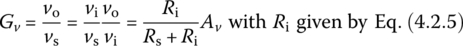

- Voltage Gains Gvand Av

To find the voltage gain, we write the node equation for the circuit of Figure 4.24(b1) as

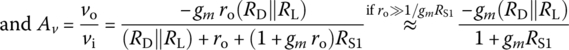

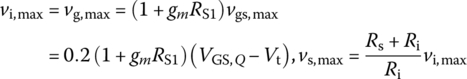

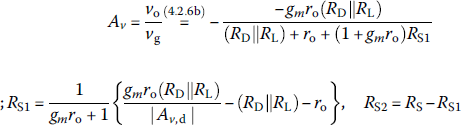

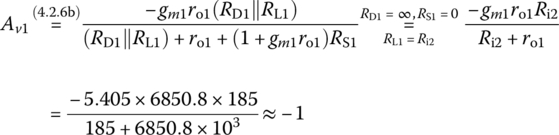

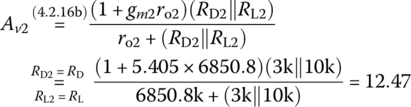

Noting that vi = vg = Ri vs/(Rs + Ri), we can write the voltage gains, i.e. the ratios of the output voltage vo to the source voltage vs and the input voltage vi as

(4.2.6a)

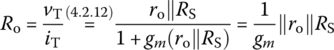

- Output Resistance Ro

To find the (Thevenin) equivalent resistance seen from the load side, we need to remove the (independent) voltage source vs by short‐circuiting it as depicted in Figure 4.24(c). Then, with the test voltage vT applied across RD, we write the drain current id as

Since the test current iT flowing out of vT is the sum of id and

:

:

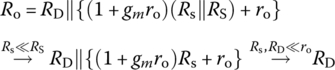

Therefore, the output resistance turns out to be

function [VGQ,VSQ,VDQ,IDQ,Av,Ri,Ro,gm,ro,Vom,vsmax]= ...FET_CS_analysis(VDD,Rs,R1,R2,RD,RS,RL,Kp,Vt,lambda,Vsm)% Copyleft: Won Y. Yang, [email protected], CAU for academic use onlyif nargin<11, Vsm=0.01; endif nargin<10, lambda=0; end % CLM parameterif length(RS)==1, RS1=0; RS2=RS; else RS1=RS(1); RS2=RS(2); end[VGQ,VSQ,VDQ,VGSQ,VDSQ,IDQ,mode,gm,ro]= ...FET_DC_analysis(VDD,R1,R2,RD,RS,Kp,Vt,lambda);if R1<=30, Ri=R2; else Ri=parallel_comb([R1 R2]); end % Eq. (4.2.5)RDL=parallel_comb([RD RL]); mug=gm*ro;if ro<inf, ro_mug1_RS1=ro+(mug+1)*RS1; Av=-mug*RDL/(RDL+ro_mug1_RS1);else ro_mug1_RS1=inf; Av=-gm*RDL;endRo = parallel_comb([ro_mug1_RS1 RD]); % Eq. (4.2.7)Avi=1/(Rs/Ri+1); Gv=Avi*Av; % Eq. (4.2.6)fprintf(' Ri=%8.2f[kOhm], Ro=%6.0f[Ohm] Gv=Ri/(Rs+Ri)xAv =%5.2f x%8.2f=%8.2f with Kp=%5.2f[mA/V^2], gm=%8.3f[mS], ro=%8.3f[kOhm] ', ...Ri/1e3,Ro,Avi,Av,Gv,Kp*1e3,gm*1e3,ro/1e3)Vom=Gv*Vsm; vsmax=0.2*(1+gm*RS1)*(VGSQ-Vt)/Avi; % Eq. (4.2.9)if strcmp(mode(1:3),'sat')~=1fprintf(' This AC analysis is invalid since the FET is notin the saturation region '); return;endif abs(Vom/RDL)>=0.99*IDQfprintf(' Possibly crash into cutoff region since |Av*Vsm/RDL(%9.4fmA)|>=|IDQ|(%9.4fmA) ', abs(Av*Vsm/RDL)*1e3,abs(IDQ)*1e3);endif abs(VDSQ)-abs(Vom)<abs(VGSQ-Vt) % Eq. (4.1.9) Sat condition not metfprintf(' Possibly violate the ohmic region since |VDSQ|-|Av*Vsm|(%6.3f)<|VGSQ-Vt|(%6.3f) ',abs(VDSQ)-abs(Av*Vsm),abs(VGSQ-Vt));end - Maximum Small‐Signal Input vs,maxfor Linear Amplification

Noting that if ro is very large in Figure 4.24(b1),

(4.2.8)

the maximum small‐signal input satisfying the condition (4.2.3) for linear amplification can be determined as

Example 4.6 Analysis of Two CS FET Amplifiers

Consider the CS FET amplifiers in Figure 4.25(a1) and (a2) where VDD = 12 V, Rs = 1 kΩ, R1 = 2.2 MΩ, R2 = 1.5 MΩ, RD = 22 kΩ, RS1 = 6 kΩ, RS2 = 6 kΩ, RL = 100 kΩ, Kp = 0.5 mA/V2, Vt = 1 V, and λ = 0.01 V‐1.

%elec04e06.mVDD=12; Rs=1e3; R1=22e5; R2=15e5; RD=22e3; RL=1e5;Kp=0.5e-3; Vt=1; lambda=0.01; RS=[6e3 6e3]; RS2=[0 sum(RS)];[VGQ,VSQ,VDQ,IDQ,Av1,Ri1,Ro1,gm1,ro1,Vom1,vsmax1]= ...FET_CS_analysis(VDD,Rs,R1,R2,RD,RS,RL,Kp,Vt,lambda) % for (a1)[VGQ2,VSQ2,VDQ2,IDQ2,Av2,Ri2,Ro2,gm2,ro2,Vom2,vsmax2]= ...FET_CS_analysis(VDD,Rs,R1,R2,RD,RS2,RL,Kp,Vt,lambda) % for (a2)gmRS1=[1+gm1*RS(1) 1+gm2*RS2(1)], vsmax=[vsmax1 vsmax2]

Figure 4.25 Two CS FET amplifiers and their PSpice simulation results (“elec04e06.opj”).

To find the values of the amplifier parameters, Ri, Ro, Av = vo/vi, and Gv = vo/vs, and determine the maximum small‐signal input vs,max allowing linear amplification for the two circuits, we run the above MATLAB script “elec04e06.m” to get

VDD VGQ VSQ VDQ IDQ12.00 4.86 2.90 6.68 2.42e-04in the saturation mode with VGD,Q= -1.82[V] (Vt=1.00)Ri= 891.89 kOhm, Ro= 21723 Ohm % for (a1)Gv=Ri/(Rs+Ri)xAv= 1.00 x -2.22 = -2.22 with gm=0.501[mS], ro=429kOhmRi= 891.89 kOhm, Ro= 20928 Ohm % for (a2)Gv=Ri/(Rs+Ri)xAv= 1.00 x -8.67 = -8.66 with gm=0.501[mS], ro=429kOhmgmRS1 = [4.0048 1.0000], vsmax = [0.7738 0.1932]

These DC + AC analysis results are supported by the PSpice simulation results shown in Figure 4.25(a1), (a2), and (c). As can be guessed from Eqs. (4.2.6b) (Av inversely proportional to 1 + gmRS1) and (4.2.9) (vs,max ≈ vi,max proportional to 1 + gmRS1), the voltage gain of (a2) is about 4 times that of (a1) while vs,max of (a2) is about 1/4 times that of (a1). Thus, the two amplifiers (a1) and (a2) will not differ much in the sweep range of their output voltage vo that can be amplified linearly without distortion.

4.2.2 CD Amplifier (Source Follower)

Figure 4.26 shows a CD FET amplifier and its low‐frequency AC equivalent where the FET has been replaced by the equivalent in Figure 4.3(b). Let us find the input resistance, voltage gain, and output resistance. The formulas have been implemented in the MATLAB function ‘FET_CD_analysis()’.

- Input Resistance Ri

Since the gate current of the FET is almost zero, the input resistance is

- Voltage Gains Gvand Av

To find the voltage gain Av = vo /vi, we write the node equation for the circuit of Figure 4.26(b1) as

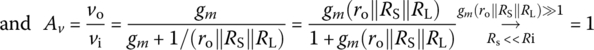

Thus, we have the voltage gains as

function [VGQ,VSQ,VDQ,IDQ,Av,Ri,Ro,gm,ro,Vom,vsmax]=FET_CD_analysis(VDD,Rs,R1,R2,RD,RS,RL,Kp,Vt,lambda,Vsm)% If D with RD~=0 is AC grounded, RD should be given as [0 RD].% Copyleft: Won Y. Yang, [email protected], CAU for academic use onlyRD1=RD(1); RS1=RS(1);[VGQ,VSQ,VDQ,VGSQ,VDSQ,IDQ,mode,gm,ro]= ...FET_DC_analysis(VDD,R1,R2,RD,RS,Kp,Vt,lambda);if R1<=30, Ri=R2;else Ri=parallel_comb([R1 R2]); % Eq. (4.2.10)endgm1=gm/(1+RD1/ro); ro1=ro+RD1; % Against the case where RD is nonzero.RSL=parallel_comb([RS1 RL]); RdsSL=parallel_comb([ro1 RSL]);Ro=parallel_comb([1/gm1 RS1 ro1]); % Eq. (4.2.12)Av=gm1*RdsSL/(1+gm1*RdsSL); Avi=1/(Rs/Ri+1);Gv=Avi*Av; % Eq. (4.2.11)Vom=Gv*Vsm;vsmax=0.2*(1+gm1*RdsSL)*(VGSQ-Vt)/Avi; % Eq. (4.2.13)fprintf(' Ri=%8.2f kOhm, Ro=%6.0f Ohm Gv=Ri/(Rs+Ri)xAv =%7.4f x%8.4f=%8.4f', Ri/1e3,Ro,Avi,Av,Gv)if strcmp(mode(1:3),'sat')~=1fprintf(' This AC analysis is invalid since the FET isn't saturated ');return;endif abs(Av*Vsm/RSL)>=IDQ, fprintf(' Possibly crash into cutoff '); endif abs(VDSQ)-Av*Vsm<abs(VGSQ-Vt) % Eq. (4.1.9) is not metfprintf(' Possibly violate the ohmic region ');endThis implies that if Rs ≪ Ri and gm (ro||Rs||RL) ≫ 1, the output voltage is almost equal to the input and source voltages and that is why the CD amplifier is called a voltage follower.

- Output Resistance Ro

To find the output resistance, we remove the (independent) voltage source, vi, by short‐circuiting it as depicted in Figure 4.26(c). Then, with the test current iT applied to the output port, we can get

- Maximum Small‐Signal Input vs,maxfor Linear Amplification

Noting that if ro is very large in Figure 4.26(b1),

Figure 4.26 A CD (common‐drain) FET circuit and its low‐frequency AC equivalent.

we can write the maximum small‐signal input satisfying the condition (4.2.3) for linear amplification as

Example 4.7 Analysis of a CD FET Amplifier

Consider the CD FET amplifier in Figure 4.27(a) where VDD = 12 V, Rs = 1 kΩ, R1 = 2.2 MΩ, R2 = 1.5 MΩ, RD = 0 kΩ, RS = 12 kΩ, RL = 100 kΩ, Kp = 0.5 mA/V2, Vt = 1 V, and λ = 0.01 V‐1.

%elec04e07.mVDD=12; Rs=1e3; R1=22e5; R2=15e5; RD=0; RS=12e3; RL=1e5; Vsm=0.2;Kp=0.5e-3; Vt=1; lambda=0.01;[VGQ,VSQ,VDQ,IDQ,Av1,Ri,Ro,gm,ro,Vom,vsmax]= ...FET_CD_analysis(VDD,Rs,R1,R2,RD,RS,RL,Kp,Vt,lambda);fprintf('vsmax =%10.3e[V] ',vsmax);

To find the values of the amplifier parameters Ri, Ro, Av = vo/vi, and Gv = vo/vs, and determine the maximum small‐signal input vs,max allowing linear amplification for the circuit, we run the above MATLAB script “elec04e07.m” to get

VDD VGQ VSQ VDQ IDQ12.00 4.86 2.92 12.00 2.43e-04in the saturation mode with VGD,Q= -7.14[V] (Vt=1.00)gm= 0.515[mS], ro= 448.241[kOhm]Ri= 891.89 kOhm, Ro= 1665 OhmGv=Ri/(Rs+Ri)xAv = 0.9989 x 0.8435 = 0.8426vsmax = 1.209e+00[V]

These DC + AC analysis results are supported by the PSpice simulation results shown in Figure 4.27(c1) and (c2). As can be guessed from Eqs. (4.2.11) and (4.2.12), the voltage gain, less than 1, may increase toward 1 and the output resistance Ro, smaller than 1/gm, may become smaller as the transconductance gm (Eq. (4.1.4b)) (proportional to ID,Q) increases.

Figure 4.27 A CD FET amplifier and its PSpice simulation results (“elec04e07.opj”).

4.2.3 Common‐Gate (CG) Amplifier

Figure 4.28 shows a CG amplifier and its low‐frequency AC equivalent where the FET has been replaced by the equivalent in Figure 4.3(b). Let us find the input resistance, voltage gain, and output resistance. The formulas have been implemented in the MATLAB function ‘FET_CG_analysis()’.

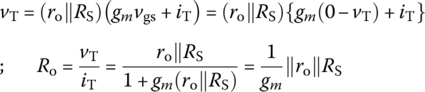

- Input Resistance Ri

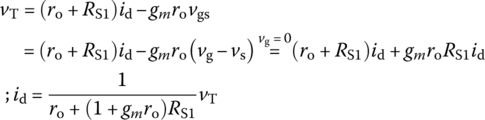

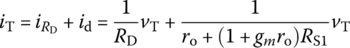

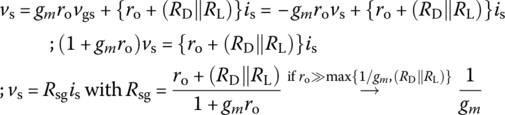

To find the input resistance, we apply a test voltage source vs between node s and GND (as depicted in Figure 4.28(c)) and then write the relationship of vs and is as

This implies that the equivalent resistance of the FET between node s and GND is Rsg. Thus, the input resistance is the parallel combination of RS and Rsg:

Figure 4.28 A CG (common‐gate) FET circuit and its low‐frequency AC equivalent.

- Voltage Gains Gvand Av

Since (during the process of computing Ri) the current through RD||RL caused by vs was found to be

the output voltage (across RD||RL) can be expressed as

Thus, taking account of vi = Ri vsig/(Rs + Ri), we can write the voltage gains, i.e. the ratios of the output voltage vo to the source voltage vsig and the input voltage vi as

- Output Resistance Ro

To find the output resistance, we remove the (independent) voltage source vi by short‐circuiting it. Then, we can write the output resistance as

- Maximum Small‐Signal Input vs,maxfor Linear Amplification

Since |vi| = |vg| = |vgs|, the maximum small‐signal input satisfying the condition (4.2.3) for linear amplification can be determined as

function [VGQ,VSQ,VDQ,IDQ,Av,Ri,Ro,gm,ro,Vom,vsmax]= ...FET_CG_analysis(VDD,Rs,R1,R2,RD,RS,RL,Kp,Vt,lambda,Vsm)% Copyleft: Won Y. Yang, [email protected], CAU for academic use only[VGQ,VSQ,VDQ,VGSQ,VDSQ,IDQ,mode,gm,ro]= ...FET_DC_analysis(VDD,R1,R2,RD,RS,Kp,Vt,lambda);RS1=RS(1); RDL=parallel_comb([RD RL]); Rsg=(ro+RDL)/(1+gm*ro);if R1<=30, Ri=R2; else Ri=parallel_comb([RS1 Rsg]); end % Eq. (4.2.15)Ro=parallel_comb([(1+gm*ro)*parallel_comb([Rs RS1])+ro RD]); % Eq. (4.2.17)Av=RDL/Rsg; Avi=1/(Rs/Ri+1); % Eq. (4.2.16b)Gv=Avi*Av; % Eq. (4.2.16a)Vom=Gv*Vsm; vsmax=0.2*(VGSQ-Vt)/Avi; % Eq. (4.2.18)fprintf(' Ri=%8.2f[kOhm], Ro=%6.0f[Ohm] Gv=Ri/(Rs+Ri)xAv =%5.2f x%8.2f =%8.2f ', Ri/1e3,Ro,Avi,Av,Gv,Kp*1e3,gm*1e3,ro/1e3)if strcmp(mode(1:3),'sat')~=1fprintf('/nThis AC analysis is invalid since the FET isn't saturated ');return;endif abs(VDSQ)-Av*Vsm<abs(VGSQ-Vt) % Eq. (4.1.9) is not metfprintf(' Possibly violate the ohmic region ');end

Example 4.8 Analysis of a CG Amplifier

Consider the CG FET amplifier in Figure 4.29(a) where VDD = 12 V, Rs = 2 kΩ, R1 = 2.2 MΩ, R2 = 1.5 MΩ, RD = 22 kΩ, RS = 12 kΩ, RL = 100 kΩ, Kp = 0.5 mA/V2, Vt = 1 V, and λ = 0.01 V‐1.

%elec04e08.mVDD=12; Rs=2e3; R1=22e5; R2=15e5; RD=22e3; RS=12e3; RL=1e5; Vsm=5e-3;Kp=0.5e-3; Vt=1; lambda=0.01;[VGQ,VSQ,VDQ,IDQ,Av1,Ri,Ro,gm,ro,Vom,vsmax]= ...FET_CG_analysis(VDD,Rs,R1,R2,RD,RS,RL,Kp,Vt,lambda)fprintf('vsmax =%10.4fmV ',vsmax*1e3);

To find the values of the amplifier parameters Ri, Ro, Av = vo/vi, and Gv = vo/vs, and determine the maximum small‐signal input vs,max allowing linear amplification for the circuit, we run the above MATLAB script “elec04e08.m” to get

VDD VGQ VSQ VDQ IDQ12.00 4.86 2.90 6.68 2.42e-04in the saturation mode with VGD,Q= -1.82[V] (Vt=1.00)gm= 0.501[mS], ro= 429.481[kOhm]Ri= 1.766[kOhm], Ro= 21411[Ohm]Gv=Ri/(Rs+Ri)xAvoxRL/(Ro+RL) =0.4690 x ( 10.57x0.8236= 8.707) = 4.083vsmax = 810.2108mV

Figure 4.29 A CG amplifier and its PSpice simulation results (“elec04e08.opj”).

These DC + AC analysis results are supported by the PSpice simulation results shown in Figure 4.29(a), (c1), and (c2). As can be guessed from Eq. (4.2.15), the input resistance Ri is small so that the overall voltage gain Gv = vo/vs can be substantially lower than the terminal voltage gain Av = vo/vi.

4.2.4 Common‐Source (CS) Amplifier with FET Load

4.2.4.1 CS Amplifier with an Enhancement FET Load

Figure 4.30(a) shows a CS amplifier with an enhancement NMOS driver MD and an enhancement NMOS load ML, which is diode connected with its gate and drain short‐circuited so that it can act like a nonlinear resistor. The drain (output) characteristic curves of MD (for several values of vGS) are plotted as solid lines while the iD,L−vDS,L and iD,L−vDS,D=VDD−vDS,L relationships of ML (with vGS,L = vDS,L) are plotted as the lines of square/circle symbols, respectively, in Figure 4.30(b) where the conduction parameter Kp, threshold voltage Vt, and CLM parameter λ of MD and ML are

Figure 4.30 A CS amplifier with an enhancement FET load, its load line analysis, and PSpice simulation results.

From the locus of dynamic operating points obtained from the intersections of the (pink solid) load line and the characteristic curves of MD (for several values of vi = vGS,D), the graphs of iD(t) = iD,L(t) = iD,D(t) and vo(t) = vDS,D(t) for the sinusoidal input vi(t) = Vsm sin (2000πt) (with Vsm = 0.5 or 1) applied to the G‐S terminals of MD have been plotted as the green and red lines in Figure 4.30(b).

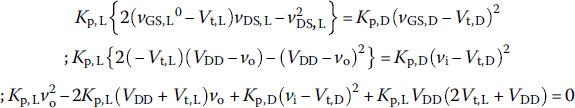

Note that the intersection of the load line of ML and the characteristic curve of MD for a certain value of the input vGS,D = vi (>Vt,D) can analytically be obtained as follows:

function [VGQ,VSQ,VDQ,IDQ,vo,iD,gm,ro]=FET_CS_NMOSe(VDD,Rs,R1,R2,RL,Kp,Vt,lambda,vi)% Copyleft: Won Y. Yang, [email protected], CAU for academic use onlyKpD=Kp(1); KpL=Kp(end); VtD=Vt(1); VtL=Vt(end);if lambda(1)>1, lambda=1./lambda; endlambdaD=lambda(1); lambdaL=lambda(end);if nargin<9, vi=0; else vi=[vi 0]; end % 0 for finding the Q pointRi=R1*R2/(R1+R2); VGQ=VDD*R2/(R1+R2); VSQ=0; VGSQ=VGQ-VSQ; B=2*(VtL-VDD);for n=1:length(vi)vGSn = VGQ + vi(n)/(Rs/Ri+1);C=(VDD-VtL)^2-KpD/KpL*(vGSn-VtD)^2; % Eq. (4.2.20)D=B^2-4*C; % Discriminant of Eq. (4.2.20)if D<=0 % vGSn<VtDfprintf('Driver FET is OFF for vGS(%5.2f)<=VtD(%5.2f) ', vGSn,VtD);iD(n)=0; vo(n)=VDD; continue;endvon=(-B-sqrt(D))/2; iDn=KpD/2*(vGSn-VtD)^2;if von<vGSn-VtD % vGD,D=vGS,D-vDS,D=vGSn-von>Vt ?A=1+KpD/KpL; B1=B+2*KpD/KpL*(VtD-vGSn); C=(VDD-VtL)^2; % Eq. (4.2.21)von=(-B1-sqrt(B1^2-4*A*C))/2/A; iDn=KpL/2*(VDD-von-VtL)^2;fprintf('Driver FET is ohmic with vGD(%5.2f)>Vt(%5.2f) ...for vi(%4d)=%5.2f ', vGSn-von,VtD,n,vi(n));endvo(n)=von; iD(n)=iDn;endVDSQ=von; VDQ=VDSQ+VSQ; IDQ=iDn; vo=vo(1:end-1); iD=iD(1:end-1);gm=KpD*(VGQ-VtD)*(1+lambdaD*VDSQ); ro=1/lambdaD/abs(IDQ); % Eq. (4.1.4)if VDSQ<sqrt(2*IDQ/KpD)|VDSQ>VDD-VtLfprintf(' Linear AC analysis is invalid for FET isn''t saturated! ');end

- (Step 1) Assuming that both NMOSs are in the saturation region, we find the smaller one of the two roots of the following quadratic equation since the larger one (>VDD) must be invalid:

- (Step 2) If this (tentative) solution is not in the saturation region of MD, i.e. vDS,D < vGS,D

‐Vt,D so that vGD,D = vGS,D‐vDS,D >Vt,D, we assume that MD is in the ohmic region and find the smaller one of the two roots of the following quadratic equation:

This process of analyzing the CS amplifier with an enhanced FET load has been cast into the above MATLAB function ‘FET_CS_NMOSe()’. We can run the following MATLAB script “do_FET_CS_NMOSe.m” to plot the output vo(t) to the input vi(t) = 0.5 sin (2000πt) for t = 0 ~ 1 ms like the PSpice simulation result shown in Figure 4.30(c).

%do_FET_CS_NMOSe.mVDD=18; Rs=100; R1=1e5; R2=1e5; RL=1e6; Vsm=0.5;tf=1e-3; t=tf/180*[0:180]; w=2000*pi; vi=Vsm*sin(w*t);Kp=[2e-5 2e-5]; Vt=[1 1]; lambda=1e-2; % Eq. (4.2.14)[VGQ,VSQ,VDQ,IDQ,vo,iD]= ...FET_CS_NMOSe(VDD,Rs,R1,R2,RL,Kp,Vt,lambda,vi);subplot(221), plot(t,vi, t,vo-(VDQ-VSQ),'r'), grid on

CS Amplifier with a Depletion FET Load

Figure 4.31(a) shows a CS amplifier with an enhancement NMOS driver MD and a depletion NMOS load ML, which is diode connected with its gate and source short‐circuited so that it can act like a current‐limited nonlinear resistor. The drain (output) characteristic curves of MD (for several values of vGS) are plotted as blue lines while the iD,L – vDS,L and iD,L – vDS,D = VDD – vDS,L relationships of ML (with vGS,L = 0) are plotted as the lines of square/circle symbols, respectively, in Figure 4.31(b) where the conduction parameter Kp, threshold voltage Vt, and CLM parameter λ of MD and ML are

Figure 4.31 A CS amplifier with a depletion FET load, its load line analysis, and PSpice simulation results.

From the locus of dynamic operating points obtained from the intersections of the (pink solid) load line and the characteristic curves of MD (for several values of vi = vGS), the graphs of iD(t) = iD,L(t) = iD,D(t) and vo(t) = vDS,D(t) for the sinusoidal input vi(t) = Vsm sin (2000πt) (with Vsm = 0.5 or 1) applied to the G‐S terminals of MD can be plotted as the green and red lines, respectively, in Figure 4.31(b).

Note that the intersection of the load line of ML and the characteristic curve of MD for a certain value of the input vGS,D = vi (>Vt,D) can analytically be found as follows:

- (Step 1) Assuming that both NMOSs are in the saturation region, find the root of the following first‐degree polynomial equation:

function [VGQ,VSQ,VDQ,IDQ,vo,iD,gm,ro]= ...FET_CS_NMOSd(VDD,Rs,R1,R2,RL,Kp,Vt,lambda,vi)% Copyleft: Won Y. Yang, [email protected], CAU for academic use onlyKpD=Kp(1); KpL=Kp(end); VtD=Vt(1); VtL=Vt(end);if lambda(1)>1, lambda=1./lambda; endlambdaD=lambda(1); lambdaL=lambda(end);Ri=parallel_comb([R1 R2]); % Input resistanceVGQ=VDD*R2/(R1+R2); VSQ=0; VGSQ=VGQ-VSQ;if nargin<9, vi=0; else vi=[vi 0]; end % 0 for finding the Q pointfor n=1:length(vi)vGSn = VGQ + vi(n)/(Rs/Ri+1);num=VtL^2*(1+lambdaL*VDD)-KpD/KpL*(vGSn-VtD)^2;den=lambdaD*KpD/KpL*(vGSn-VtD)^2+lambdaL*VtL^2; % Eq. (4.2.23)von=num/den; iDn=KpL/2*VtL^2*(1+lambdaL*(VDD-von));if von<vGSn-VtD % vGD,D=vGS,D-vDS,D=vGSn-von>Vt ?fprintf('MD is ohmic: vGD(%5.2f)<Vt(%5.2f) ',vGSn-von,VtD);iDn=KpL/2*VtL^2; B=2*(VtD-vGSn); C=iDn/KpD; % Eq. (4.2.24)von=(-B-sqrt(B^2-4*C))/2;elseif von>VDD+VtL % vGD,L=vSD,L=vDS,D-VDD=von-VDD>VtL ?fprintf('ML is ohmic: vGD(%5.2f)>Vt(%5.2f) ', von-VDD,VtL);iDn=KpD/2*(vGSn-VtD)^2; B=-2*(VDD+VtL); C=iDn/KpL+VDD*(2*VtL+VDD); % Eq. (4.2.25)von=(-B+sqrt(B^2-4*C))/2;endvo(n)=von; iD(n)=iDn;endVDSQ=vo(n); VDQ=VDSQ+VSQ; IDQ=iD(n);vo=vo(1:end-1); iD=iD(1:end-1);gm=KpD*(VGQ-VtD)*(1+lambdaD*VDSQ); ro=1/lambdaD/abs(IDQ); % Eq. (4.1.4)if VDSQ<VGSQ-VtDfprintf(' Linear AC analysis is invalid since driver FET is ohmic ');elseif VDSQ>VDD+VtLfprintf(' Linear AC analysis is invalid since load FET is ohmic ');end - (Step 2) If this tentative solution is in the ohmic region of MD, i.e. vo = vDS,D < vGS,D − Vt,D = vi − Vt,D, the following equation should be solved on the assumption that MD is in the ohmic region: where the smaller one of the two roots should be taken as vo,Q = VDS,D because the larger one must be invalid.

- (Step 3) If the tentative solution is in the ohmic region of ML, i.e. vo = vDS,D > VDD + Vt,L so that vGD,L =

‐vDS,L =‐(VDD − vDS,D) > Vt,L, the following equation should be solved on the assumption that ML is in the ohmic region: where the larger one of the two roots should be taken as the value of vo because the smaller one must be invalid.

This process of analyzing the CS amplifier with a depletion FET load has been cast into the above MATLAB function ‘FET_CS_NMOSd()’.

An alternative to analyze the circuit of Figure 4.31(a) is to solve the KCL at node 1:

where vGS,D = VGSQ,D + vi with VGSQ,D = VDDR2/(R1 + R2) and iDk(vGSk, vDSk) is defined as Eq. (4.1.83). This algorithm can be implemented by replacing the for loop of the above MATLAB function ‘FET_CS_NMOSd()’ by the following block of statements:

iD_vGS_vDS=@(vGS,vDS,Kp,Vt)Kp/2*(vGS-Vt).^2.*(vGS>=Vt).*(vGS-vDS<Vt)+ Kp*((vGS-Vt).*vDS-vDS.^2/2).*(vGS>=Vt).*(vGS-vDS>=Vt); % Eq. (4.1.83)for n=1:length(vi)vGSn = VGSQ + vi(n)*Ri/(Rs+Ri); % Eq. (4.2.26)eq=@(v)(iD_vGS_vDS(0,VDD-v,KpL,VtL)-iD_vGS_vDS(vGSn,v,KpD,VtD))*1e6;if n<2, v0=VDD/2; else v0=vo_(n-1); endvo_(n)=fsolve(eq,v0); % Solution of Eq. (4.2.26)iD_(n)=iD_vGS_vDS(vGSn,vo_(n),KpD,VtD);enddiscrepancy_vo = norm(vo-vo_)/norm(vo)

Isn't it interesting that this simple algorithm of solving just one (seemingly nonlinear) equation can replace the above individual quadratic equation approach?

We can run the following MATLAB script “do_FET_CS_NMOSd.m” to plot the output vo(t) to the input vi(t) = 0.5 sin (2000πt) for t = 0 ~ 1 ms like the PSpice simulation result shown in Figure 4.31(c).

%do_FET_CS_NMOSd.mVDD=18; Rs=100; R1=1e5; R2=1e5; RL=1e6; Vsm=1;tf=1e-3; t=tf/180*[0:180]; w=2000*pi; vi=Vsm*sin(w*t);Kp=[2e-5 2e-5]; Vt=[1 -10]; lambda=[1e-2 1e-2]; % Eq. (4.2.22)[VGQ,VSQ,VDQ,IDQ,vo,iD]= ...FET_CS_NMOSd(VDD,Rs,R1,R2,RL,Kp,Vt,lambda,vi);subplot(222), plot(t,vi, t,vo-(VDQ-VSQ),'r'), grid on

4.2.5 Multistage FET Amplifiers

Table 4.3 lists the formulas for finding the input/output resistances, voltage gain, and maximum small‐signal input (for linear amplification) of the CS/CD/CG amplifiers. It also shows the conditions to be met by the coupling/bypass capacitors, whose AC impedances have been assumed to be negligibly small (for a frequency range of interest) compared with the equivalent impedance seen from their two terminals for AC analysis (see Section 14.7 of [J-1]).Note that finding the input/output resistance of a CG configuration requires the input/output resistance of the next/previous stage corresponding to its load/source resistance RL/Rs as implied by Eqs. (4.2.15) and (4.2.17). That is why, for a systematic analysis of a multistage amplifier containing one or more CG configurations, we should find the input/output resistance of each stage, starting from the last/first stage backwards/forwards to the first/last stage where to the last/first stage, the input/output resistance of the next/previous stage is nothing but the load/source resistance.

Each of the formulas listed in Table 4.3 has been coded in MATLAB as follows so that they can be called individually as symbolic expressions whenever and wherever needed. For instance, the formula for the voltage gain Av can be recalled by typing ‘Av_CS’ at the MATLAB prompt.

Table 4.3 Characteristics of CS/CD/CG amplifiers.

function [Av,Avo,Gv,Ri,Ro]=Av_CS(ro_,RS_)% Put 0 as the 1st input argument ro_ if ro=inf.% Put 0 as the 2nd input argument RS_ if RS=0.syms gm ro Rs RG RD RS RLRi=RG; % Eq. (4.2.5)RDL=parallel_comb([RD RL]);if nargin>0&ro_==0Ro=RD; % Eq. (4.2.7)if nargin>1&RS_==0, Av=-gm*RDL; % Eq. (4.2.6)else Av=-gm*RDL/(1+gm*RS); % Eq. (4.2.6)endelse % if ro is finiteif nargin>1&RS_==0, gmroRS=ro;else gmroRS=ro+(1+gm*ro)*RS;endRo=parallel_comb([RD gmroRS]); % Eq. (4.2.7)Av=-gm*ro*RDL/(RDL+gmroRS); % Eq. (4.2.6)endAvi=1/(Rs/Ri+1); AvL=1/(Ro/RL+1); Avo=Av/AvL;Gv=Avi*Av;if nargout<1fprintf(' Av = '); pretty(simplify(Av))fprintf(' Avo = '); pretty(simplify(Avo))fprintf(' Gv = '); pretty(simplify(Gv))end

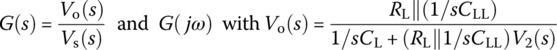

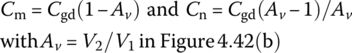

function Ri=Ri_CS()syms RGRi=RG; % Eq. (4.2.5)function Ro=Ro_CS(ro_,RS_)% Put 0 as the 1st input argument ro_ if ro=inf.% Put 0 as the 2nd input argument RS_ if RS=0.syms gm ro Rs RG RD RS RLif nargin>0&ro_==0Ro=RD; % Eq. (4.2.7)else % if ro is finiteif nargin>1&RS_==0, gmroRS=ro;else gmroRS=ro+(1+gm*ro)*RS;endRo=parallel_comb([RD gmroRS]); % Eq. (4.2.7)endif nargout<1fprintf(' Ro = '); pretty(simplify(Ro))end