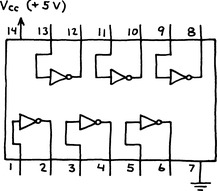

TTL/LS INTEGRATED CIRCUITS

INTRODUCTION

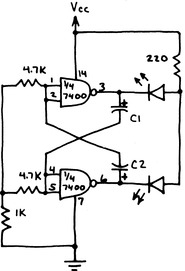

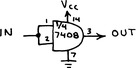

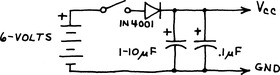

TTL IS THE BEST ESTABLISHED AND MOST DIVERSIFIED IC FAMILY. LS IS FUNCTIONALLY IDENTICAL TO TTL BUT IS SLIGHTLY FASTER AND USES 80% LESS POWER. TTL/LS CHIPS REQUIRE A REGULATED 4.75-5.25 VOLT POWER SUPPLY. HERE’S A SIMPLE BATTERY SUPPLY:

THE DIODE DROPS THE BATTERY VOLTAGE TO A SAFE LEVEL. BOTH CAPACITORS SHOULD BE INSTALLED ON THE TTL/LS CIRCUIT BOARD. CIRCUITS WITH LOTS OF TTL/LS CHIPS CAN USE LOTS OF CURRENT. USE A COMMERCIAL 5 VOLT LINE POWERED SUPPLY TO SAVE BATTERIES. OR MAKE YOUR OWN. (SEE THE 7805 ON PAGE 86.)

OPERATING REQUIREMENTS

1. VCC MUST NOT EXCEED 5.25 VOLTS.

2. INPUT SIGNALS MUST NEVER EXCEED VCC AND SHOULD NOT FALL BELOW GND.

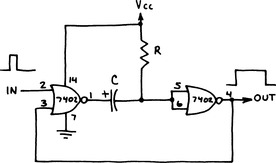

3. UNCONNECTED TTL/LS INPUTS USUALLY ASSUME THE H STATE … BUT DON’T COUNT ON IT! IF AN INPUT IS SUPPOSED TO BE FIXED AT H, CONNECT IT TO VCC.

4. IF AN INPUT IS SUPPOSED TO BE FIXED AT L, CONNECT IT TO GND.

5. CONNECT UNUSED AND/NAND/OR INPUTS TO A USED INPUT OF THE SAME CHIP.

6. FORCE OUTPUTS OF UNUSED GATES H TO SAVE CURRENT (NAND–ONE INPUT H; NOR – ALL INPUTS L).

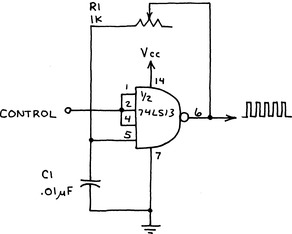

7. USE AT LEAST ONE DECOUPLING CAPACITOR (0.01–0.1 µF) FOR EVERY 5-10 GATE PACKAGES, ONE FOR EVERY 2-5 COUNTERS AND REGISTERS AND ONE FOR EACH ONE-SHOT. DECOUPLING CAPACITORS NEUTRALIZE THE HEFTY POWER SUPPLY SPIKES THAT OCCUR WHEN A TTL/LS OUTPUT CHANGES STATES. THEY MUST HAVE SHORT LEADS AND BE CONNECTED FROM VCC TO GND AS NEAR THE TTL/LS ICs AS POSSIBLE.

8. AVOID LONG WIRES WITHIN CIRCUITS

9. IF THE POWER SUPPLY IS NOT ON THE CIRCUIT BOARD, CONNECT A 1–10 µF CAPACITOR ACROSS THE POWER LEADS WHERE THEY ARRIVE AT THE BOARD.

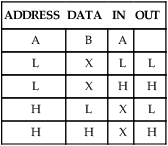

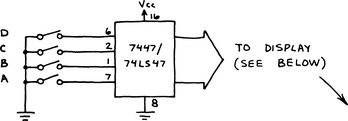

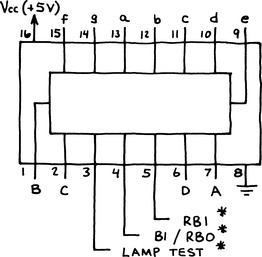

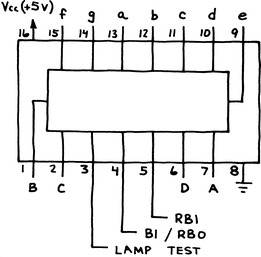

BCD-TO-7 SEGMENT DECODER/DRIVER 7447/74LS47

CONVERTS BCD DATA INTO FORMAT SUITABLE FOR PRODUCING DECIMAL DIGITS ON COMMON ANODE LED 7-SEGMENT DISPLAY. WHEN LAMP TEST INPUT IS LOW, ALL OUTPUTS ARE LOW (ON). WHEN B1/RBO (BLANKING INPUT) IS LOW, ALL OUTPUTS ARE HIGH (OFF). WHEN DCBA INPUT IS LLLL (DECIMAL 0) AND RBI (RIPPLE BLANKING INPUT) IS LOW, ALL OUTPUTS ARE HIGH (OFF). THIS PERMITS UNWANTED LEADING 0’S IN A ROW OF DIGITS TO BE BLANKED.

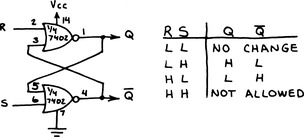

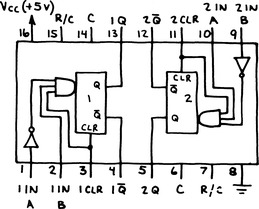

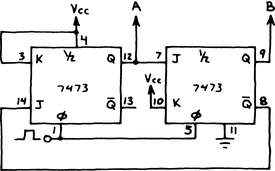

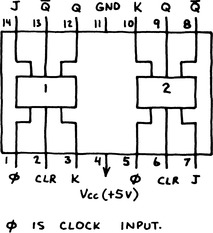

DUAL J-K FLIP-FLOP 7473

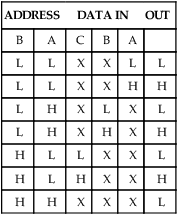

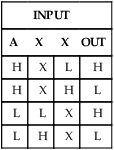

TWO JK FLIP-FLOPS IN A SINGLE PACKAGE. NOTE THE CLEAR INPUTS. THESE FLIP-FLOPS WILL TOGGLE (SWITCH OUTPUT STATES) IN RESPONSE TO INCOMING CLOCK PULSES WHEN BOTH J ANK J INPUTS ARE HIGH. HERE’S THE TRUTH TABLE:

| CLEAR | CLOCK | J | K | Q | |

| L | X | X | X | L | H |

| H | H | L | H | L | |

| H | L | H | L | H | |

| H | H | H | TOGGLE | ||

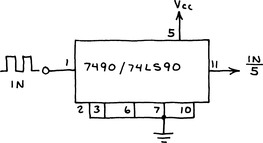

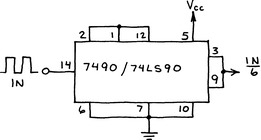

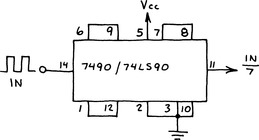

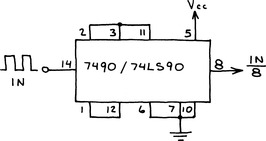

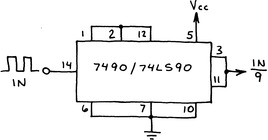

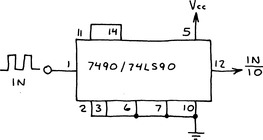

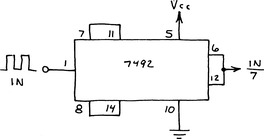

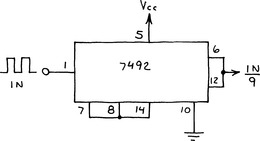

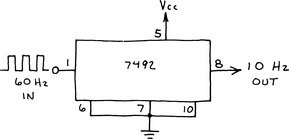

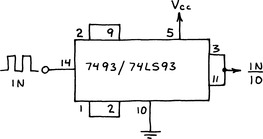

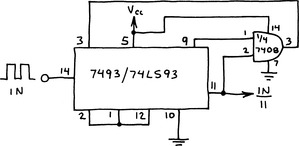

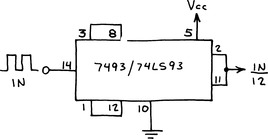

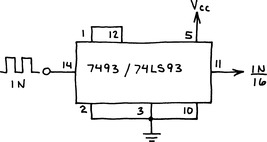

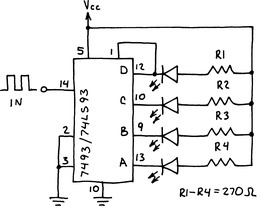

BINARY COUNTERS

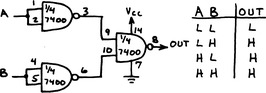

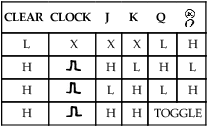

THE THREE CIRCUITS ON THIS PAGE ARE BINARY COUNTERS THAT COUNT UP TO THE MAXIMUM COUNT AND AUTOMATICALLY RECYCLE. CONNECT A DECODER TO OUTPUT OF DIVIDE-BY-THREE AND DIVIDE-BY-FOUR COUNTERS TO OBTAIN ONE - OF - THREE AND ONE-OF-FOUR OPERATION. THIS TRUTH TABLE SUMMARIZES OPERATION OF THESE COUNTERS:

| DIVIDE-BY: | TWO | THREE | FOUR | ||

| OUTPUTS: | A | B | A | B | A |

| L | L | L | L | L | |

| H | L | H | L | H | |

| H | L | H | L | ||

| H | H | ||||

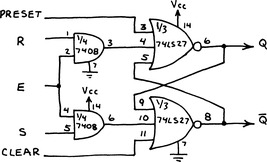

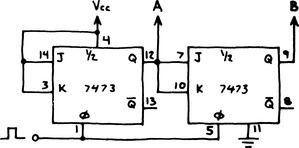

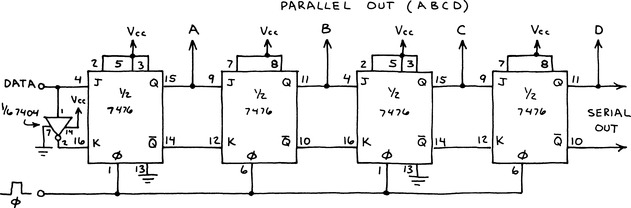

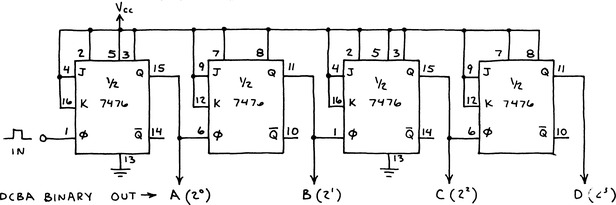

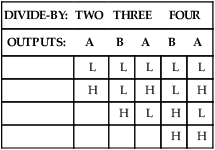

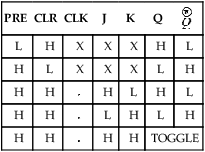

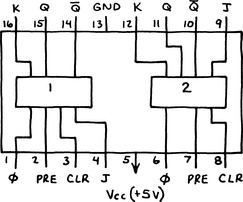

DUAL J-K FLIP-FLOP 7476

TWO JK FLIP-FLOPS IN A SINGLE PACKAGE. SIMILAR TO 7473/74LS73 BUT HAS BOTH PRESET AND CLEAR INPUTS. FLIP-FLOPS WILL TOGGLE (SWITCH OUTPUT STATES) IN RESPONSE TO INCOMING CLOCK PULSES WHEN BOTH J AND K INPUTS ARE HIGH. HERE’S THE TRUTH TABLE:

| PRE | CLR | CLK | J | K | Q | |

| L | H | X | X | X | H | L |

| H | L | X | X | X | L | H |

| H | H | H | L | H | L | |

| H | H | L | H | L | H | |

| H | H | H | H | TOGGLE | ||

TOGGLE = FLIP-FLOP SWITCHES OUTPUT STATES IN RESPONSE TO CLOCK PULSES.

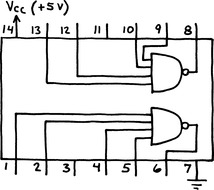

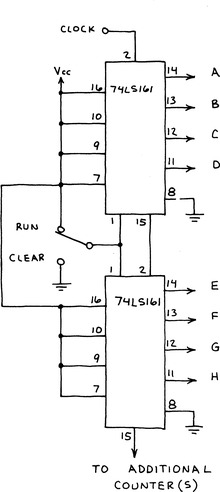

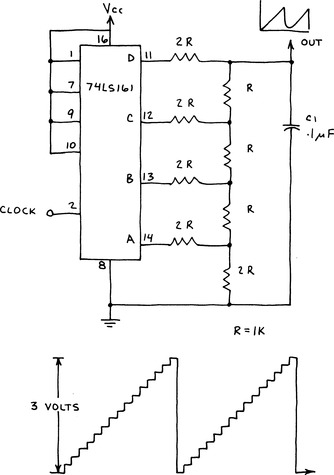

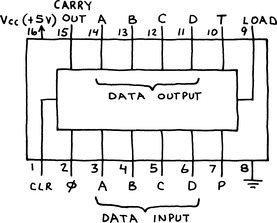

4-BIT UP COUNTER 74LS161

GENERAL PURPOSE BINARY COUNTER WITH PROGRAMMABLE INPUTS. COUNTER ACCEPTS DATA AT INPUTS WHEN LOAD INPUT GOES LOW. A LOW AT THE CLEAR INPUT RESETS THE COUNTER TO LLLL UPON THE NEXT CLOCK PULSE. P AND T ARE COUNT ENABLE INPUTS. BOTH P AND T MUST BE HIGH TO COUNT. THESE ENABLE INPUTS ARE NOT AVAILABLE WITH THE OTHERWISE MORE ADVANCED 74LS193.

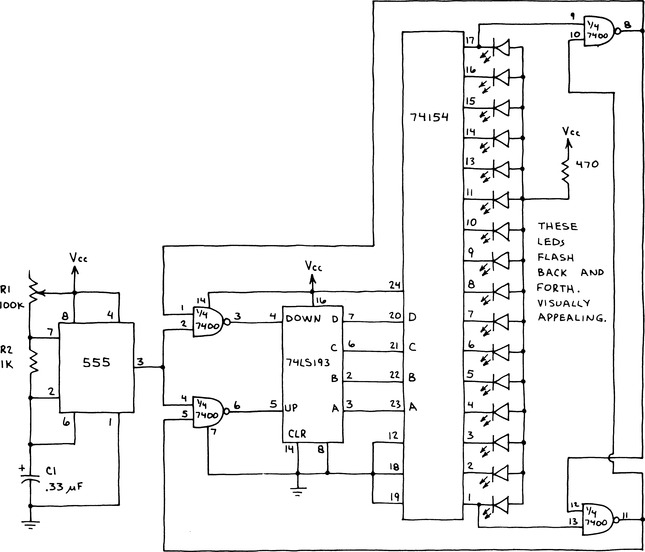

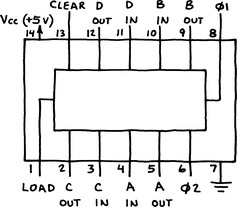

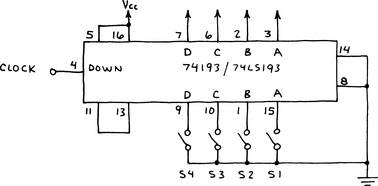

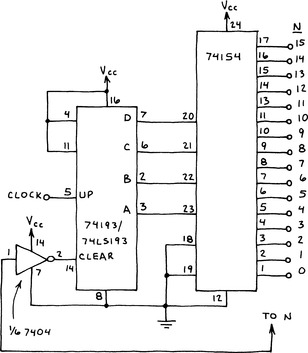

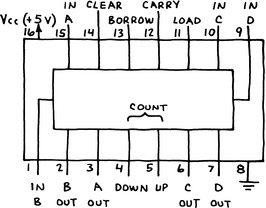

4-BIT UP-DOWN COUNTER 74193/74LS193

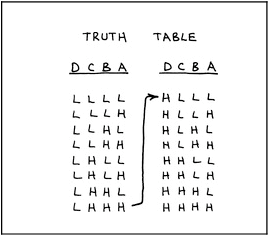

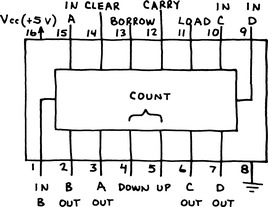

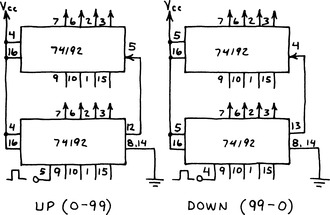

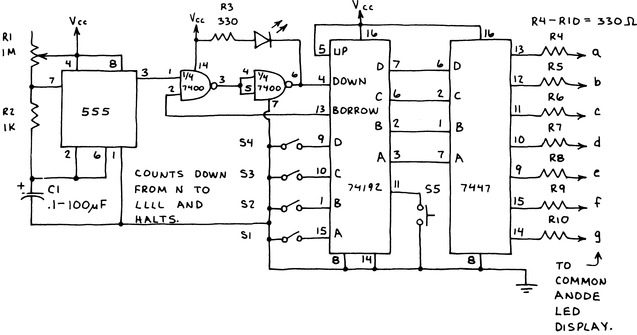

VERY VERSATILE 4-BIT COUNTER WITH UP-DOWN CAPABILITY. ANY 4-BIT NUMBER AT THE DCBA INPUTS IS LOADED INTO THE COUNTER WHEN THE LOAD INPUT (PIN 11) IS MADE LOW. THE COUNTER IS CLEARED TO LLLL WHEN THE CLEAR INPUT (PIN 14) IS MADE HIGH. THE BORROW AND CARRY OUTPUTS INDICATE UNDERFLOW OR OVERFLOW BY GOING LOW.

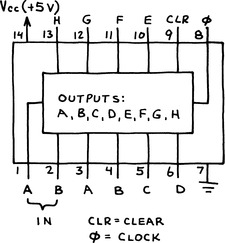

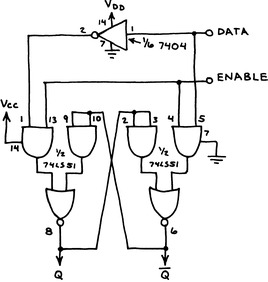

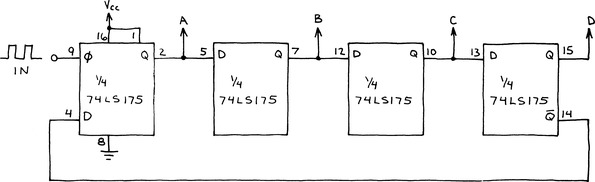

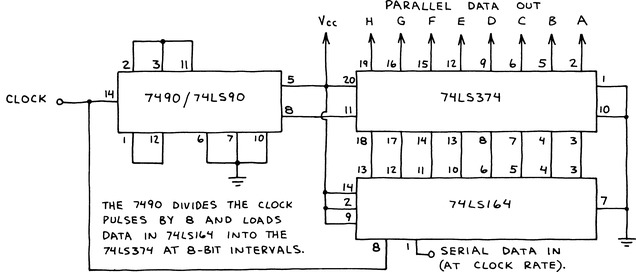

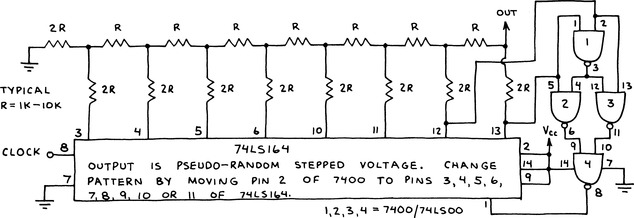

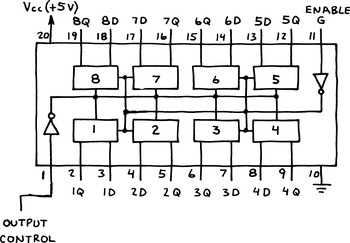

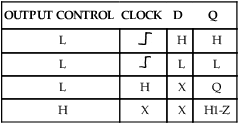

8-BIT SHIFT REGISTER 74LS164

DATA AT ONE OF THE TWO SERIAL INPUTS IS ADVANCED ONE BIT FOR EACH CLOCK PULSE. DATA CAN BE EXTRACTED FROM THE 8 PARALLEL OUTPUTS OR IN SERIAL FORM AT ANY SINGLE OUTPUT. ENTER DATA AT EITHER INPUT. THE UNUSED INPUT MUST BE HELD HIGH OR CLOCKING WILL BE INHIBITED. MAKING PIN 9 LOW CLEARS THE REGISTER TO LLLL.