The PIC family of MCUs was first introduced in 1976 by General Instrument, using their new CP1600 16-bit CPU. This CPU was nearly compatible with the PDP-11 series of processors with its instruction set.

In 1987, General Instrument spun off its microelectronics division to create Microchip Technology, which became an independent company in 1989. Microchip technology produces new PIC designs to this day. Alongside the evolution of PIC cores and peripherals, on-chip memory technology development yielded the introduction of light tight encapsulated EPROM for on-time programmable and later EEPROM for in-circuit reprogramming capabilities. Like most MCUs, PIC MCUs have a Harvard architecture. Today, PIC designs range from 8-bit to 32-bit, with a wide range of features. These are the PIC families as the time of writing this book:

|

Family |

Pins |

Memories |

Details |

|

PIC10 |

6-8 |

384-896 bytes ROM, 64-512 bytes RAM |

8-bit, 8-16 MHz, modified Harvard |

|

PIC12 |

8 |

2-16 KB ROM, 256 bytes RAM |

8-bit, 16 MHz, modified Harvard |

|

PIC16 |

8-64 |

3.5-56 KB ROM, 1-4 KB RAM |

8-bit modified Harvard |

|

PIC17 |

40-68 |

4-16 KB ROM, 232-454 bytes RAM |

8-bit, 33 MHz, superseded by the PIC18, though third-party clones exist. |

|

PIC18 |

28-100 |

16-128 KB ROM, 3,728-4,096 bytes RAM |

8-bit modified Harvard |

|

PIC24 (dsPIC) |

14-144 |

64-1,024KB ROM, 8-16 KB RAM |

16-bit, DsPIC (dsPIC33) MCUs have digital signal processing (DSP) peripherals built in. |

|

PIC32MX |

64-100 |

32-512 KB ROM, 8-32 KB RAM |

32-bit, 200 MHz MIPS M4K with MIPS16e mode, released in 2007. |

|

PIC32MZ EC PIC32MZ EF PIC32MZ DA |

64-288 |

512-2,048 KB ROM, 256-640 KB static RAM (32 MB DDR2 DRAM) |

32-bit, MIPS ISA (2013), PIC32MZ DA version (2017) having a graphics core. Core speeds of 200 MHz (EC, DA) and 252 MHz (EF). |

|

PIC32MM |

20-64 |

16-256 KB RAM, 4-32 KB RAM |

32-bit microMIPS, 25 MHz, |

|

PIC32MK |

64-100 |

512-1,024 KB ROM, 128-256 KB RAM |

32-bit, 120 MHz, MIPS ISA, variant introduced in 2017. Targeted at industrial control and other forms of deeply integrated applications. |

The PIC32 families are interesting in that they're based on an MIPS processor core, and use this Instruction Set Architecture (ISA) instead of the PIC ISA that's used by all other PIC MCUs. The processor core design they share is the M4K, a 32-bit MIPS32 core from MIPS Technology. Between these families, the differences are easy to spot when looking at the block diagrams from their respective datasheets.

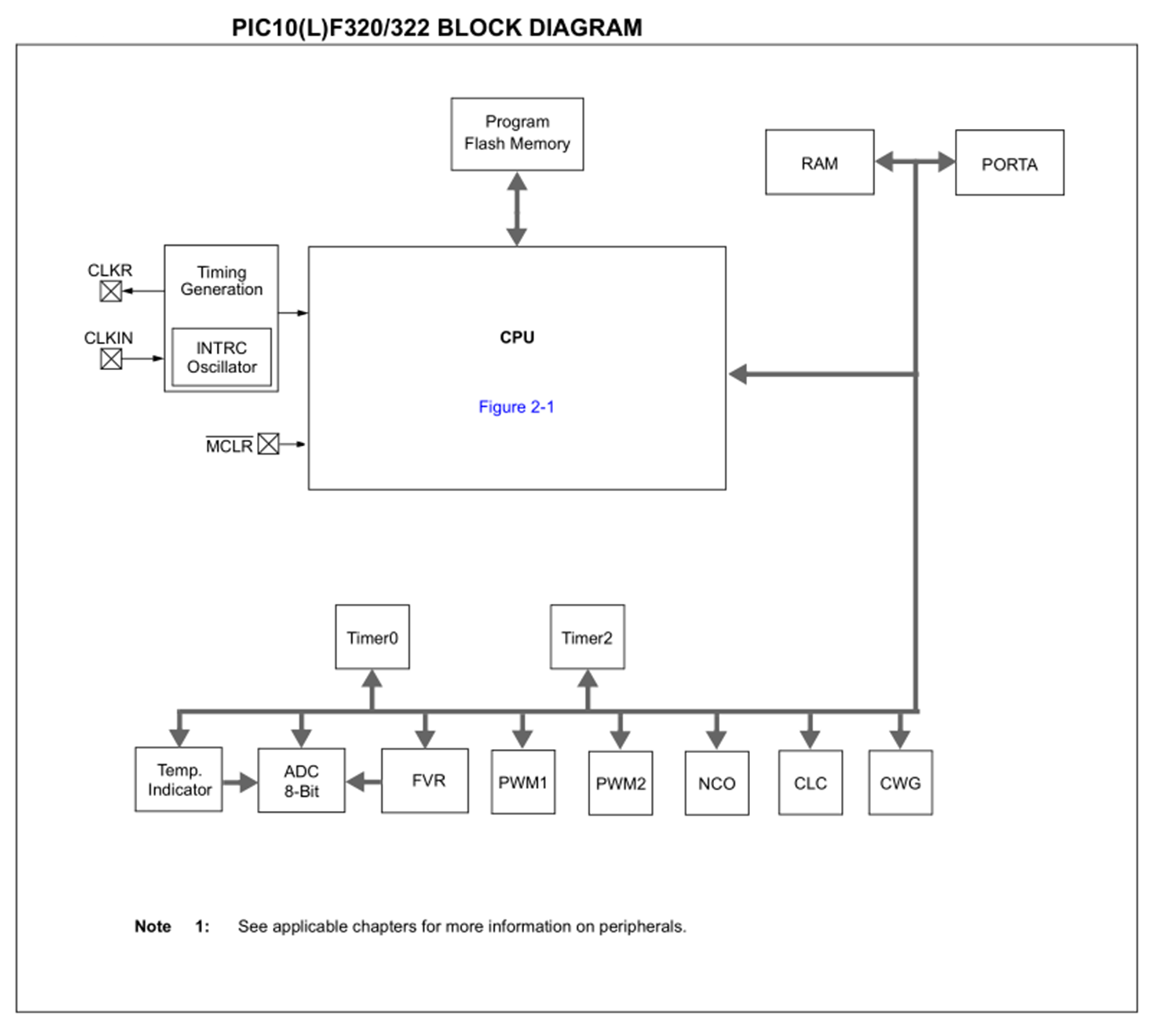

The decades of development in the PIC line of microcontrollers are perhaps best made tangible in the form of functional block diagrams, so we start by looking at the PIC10:

These are very small MCUs, with barely any peripherals around a processor core not more closely defined here—and the referenced table only mentions the memory layout. The I/O port is very minimal and the I2C and UART interfaces we know today are not implemented as peripheral logic. To pick an example for a controller next in line, the PIC16F84 datasheet is very detailed in terms of processor architecture and shows that more power-up and reset circuitry has been added while also expanding GPIO and adding EEPROM for easy integrated non-volatile storage. Self-contained serial peripherals are still absent.

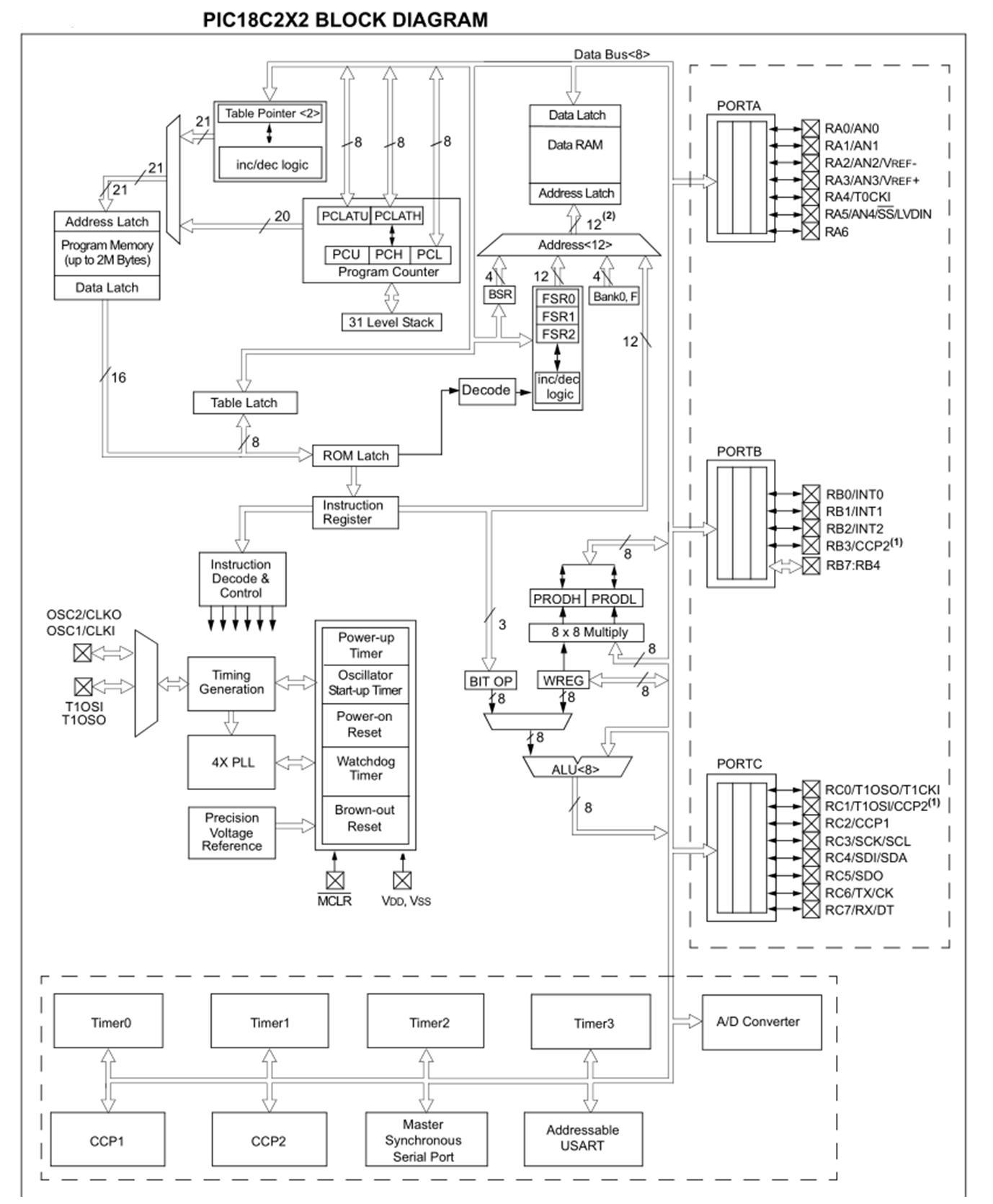

Next, we'll have a look at the PIC18:

The PIC18 family is the latest 8-bit PIC architecture, with MCUs covering a wide range of applications. It has significantly more I/O options than the PIC10, PIC12, and PIC16 families, while also offering more options in terms of ROM and RAM and now providing USART in conjunction with a synchronous serial port for 4-wire SPI. Also note that the ports now have alternate pin functions and the routing from peripherals to the pins and the corresponding configuration registers are not shown for simplicity.

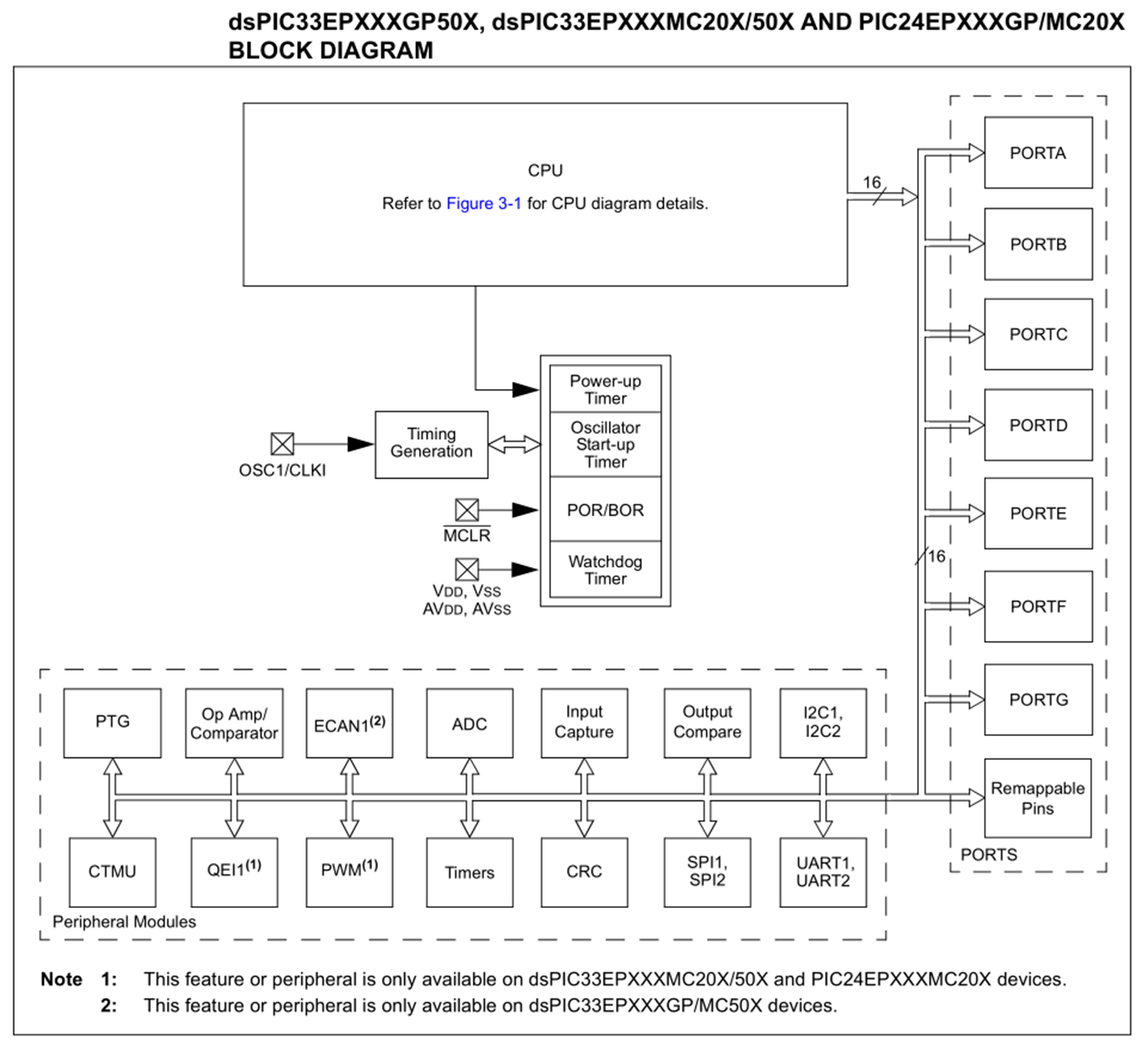

Next, let's observe the focus shifting from the core to Port and Peripheral capabilities in the PIC24 functional block diagram:

The diagram is similar to that of the PIC10, with the CPU abstracted away as a single block relative to the rest of the MCU. Each of the PORT blocks being a set of I/O pins, we're running out of space to display all the possible pin functions.

Each I/O pin can have a fixed function (linked with a peripheral module), or have an assignable function (hardware-level rerouting, or done in software). Generally, the more complex the MCU, the more likely it is that I/O pins are generic and not fixed-function.

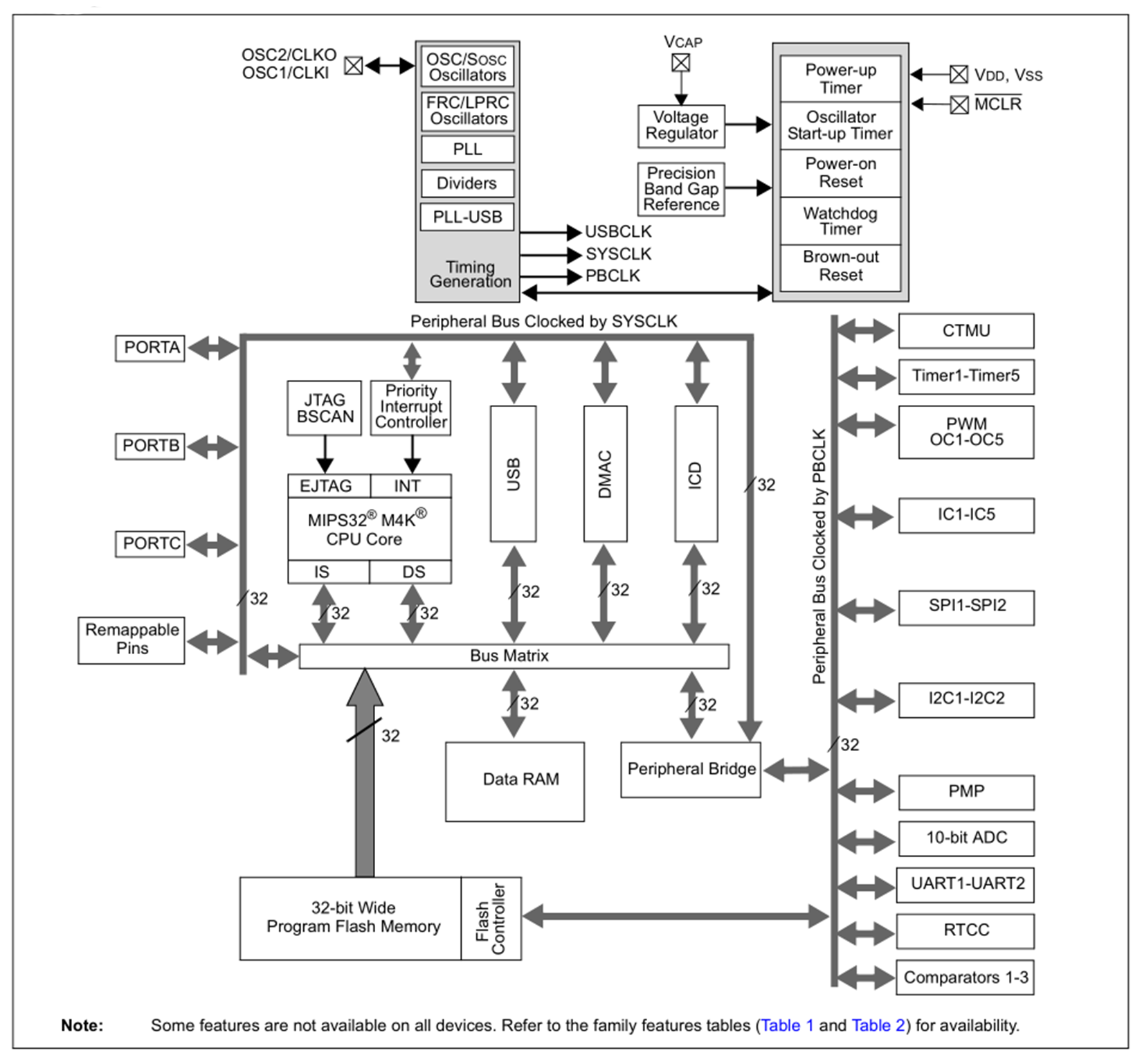

Finally we have look at the PIC32:

This block diagram is for PIC32MX1XX/2XX devices in the PIC32MX family. It is usually clocked at 50 MHz.

An interesting property of the PIC32 architecture is that it effectively turns the Harvard architecture M4K MIPS CPU into a more John von Neumann-like architecture by having both program instructions and data travel over the System Bus Matrix. Note that the space dedicated to a single processor register in the PIC10 diagram now casually depicts a complex digital or mixed signal peripheral, or the powerful JTAG in-circuit programming and debugging interface.