CHAPTER 13

The Power Distribution Network (PDN)

The power distribution network (PDN; sometimes also called the power delivery network) consists of all the interconnects from the voltage-regulator module (VRM) to the pads on the chip and the metallization on the die that locally distributes power and return current. This includes the VRM itself, the bulk decoupling capacitors, the vias, the traces, the planes on the circuit board, the additional capacitors added to the board, the solder balls or leads of the packages, the interconnects in the packages mounted to the board, the wire bonds or C4 solder balls, and the interconnects on the chips themselves.

The primary difference between the PDN and signal paths is that there is just one net for each voltage rail in the PDN. It can be a very large net that can physically span the entire board and can have many components attached.

TIP

As we will see, the PDN is like an ecosystem. If one small part of the PDN changes, the performance of the entire system can be affected. This makes generalizations very difficult.

13.1 The Problem

Figure 13-1 shows an example of a motherboard with all the interconnects mentioned in the preceding section.

The first and primary role of the PDN is to keep a constant supply voltage on the pads of the chips and to keep it within a narrow tolerance band, typically on the order of 5%. This voltage has to be stable, within the voltage limits, from DC up to the bandwidth of the switching current, typically above 1 GHz.

TIP

The purpose of the PDN is threefold: Keep the voltage across the chip pads constant, minimize ground bounce, and minimize EMI problems.

In most designs, the same PDN interconnects that are used to transport the power supply are also used to carry the return currents for signal lines. The second role of the PDN interconnects is to provide a low-impedance return path for the signals.

The easiest way of doing this is by making the interconnects wide, so the return currents can spread out as much as they want and by keeping the signal traces physically separated so that the return currents do not overlap. If these conditions are not met, the return current is constricted, and the return currents from different signals overlap. The result is ground bounce, also called simultaneous switching noise (SSN) or just switching noise.

Finally, because the PDN interconnects are usually the largest conducting structures in a board, carry the highest currents, and sometimes carry high-frequency noise, they have the potential of creating the most radiated emissions and causing failure of an EMC certification test. When done correctly, the PDN interconnects can mitigate many potential EMI problems and help prevent EMC certification test failures.

The consequence of not designing the PDN correctly is that there will be excessive noise on the voltage rails of the chips. This can cause a bit failure directly, or it can mean the clock frequency of the chip can’t be met, and timing errors result.

Figure 13-2 shows an example of the voltage noise on the pads of a processor chip. In this example, the nominally constant 2.5-v rail to the core of the chip, referred to as Vdd, shows voltage noise of as much as 125 mV on some pads. As the Vdd supply drops, the propagation delay of the core gates will increase, and timing problems can cause bit failures.

Figure 13-2 Example of the measured voltage between three different pairs of Vdd and Vss pads of a processor chip, showing as much as a 125-mV drop. The initial step down is when the processor comes out of an idle state. The three traces are three different locations on the die. The precise shape is related to the microcode running on the processor.

13.2 The Root Cause

If the problem is a voltage drop or a droop on the power supply rails on the pads of the chip, why not just use a “heftier” regulator—one that can supply a more rock stable voltage? Why not pay extra for a regulator with a 1% regulation or even 0.1% regulation? This way, the voltage from the regulator will be absolutely stable, no matter what, right?

What the chip cares about is the voltage on its pads. If there were no current flow in the PDN interconnects from the regulator pads to the chip pads, there would be no voltage drop in this path, and the constant regulator voltage would appear as a constant rail voltage on the chip pads.

If there were a constant DC current draw by the chip, this DC current would cause a voltage drop in the PDN interconnects due to the series resistance of the interconnects. This is commonly referred to as the IR drop. As the current from the chip fluctuates, the voltage drop in the PDN would fluctuate, and the voltage on the chip pads would fluctuate.

Now add not just the resistive impedance of the PDN but also the reactive components, including the inductive and capacitive qualities of the PDN interconnects. The impedance of the PDN, as seen by the pads on the chip, in general, is some complex impedance verses frequency, Z(f ). This is diagrammed in Figure 13-3.

Figure 13-3 Diagram of the connections from the VRM through the PDN to the chip pads and the voltage drop across the PDN interconnects due to the impedance of the PDN.

As fluctuating currents with some spectrum, I(f ), pass through the complex impedance of the PDN, there will be a voltage drop in the PDN:

where:

V(f ) = voltage amplitude as a function of frequency

I(f ) = current spectrum drawn by the chip

Z(f ) = impedance profile of the PDN, as seen by the chip pads

This voltage drop in the PDN means that the constant voltage of the regulator is not seen by the chip but is changed. In order to keep the voltage drop on the chip pads less than the voltage noise tolerance, usually referred to as the ripple, given the chip current fluctuations, the impedance of the PDN needs to be below some maximum allowable value. This is referred to as the target impedance:

where:

Vripple = voltage noise tolerance for the chip, in volts

VPDN = voltage noise drop across the PDN interconnects, in volts

I(f ) = current spectrum drawn by the chip, in Amps

ZPDN (f ) = impedance profile of the PDN as seen by the chip pads, in Ohms

Ztarget = maximum allowable impedance of the PDN, in Ohms

As mentioned many times so far in this book, the most important step in solving a signal integrity problem is to identify the root cause of the problem. The root cause of rail collapse or voltage noise on the PDN conductors is that a voltage drop in the PDN interconnects is created by the chip’s transient current flowing through the complex impedance of the PDN.

TIP

If we want to keep the voltage stable across the pads of the chip, given the chip’s current fluctuations, we need to keep the impedance of the PDN below a target value. This is the fundamental guiding principle in the design of the PDN.

13.3 The Most Important Design Guidelines for the PDN

The goal of the PDN is to deliver clean, stable, low-noise voltage to the pads of all the active devices that require power. We often translate this performance metric into designing the PDN interconnects to bring their impedance, as viewed from the chips’ pads, below a target value from DC to high frequency. In general, this will be accomplished by following three important design principles. Though it may not always be possible to push these to the limit, it is always important to be aware of the directions to head, even if the real-world constraints keep you from the ultimate path.

The three most important guidelines in designing the PDN are:

1. Use power and ground planes on adjacent layers, with as thin a dielectric as possible, and bring them as close to the surface of the board stack-up as practical.

2. Use a surface trace that is as short and wide as possible between the decoupling capacitor pads and the vias to the buried power and ground plane cavity and place the capacitors where they will have the lowest loop inductance.

3. Use SPICE to help select the optimum number of capacitors and their values to bring the impedance profile below the target impedance.

Unfortunately, in the real world of practical product design, you may not always have the luxury of power and ground planes on adjacent layers or placed near the top of the board stack-up. There may be multiple voltage rails, and they may have odd and irregular shapes, with many antipad clearance holes.

You may not be able to use as many capacitors as you think you need, nor place them in proximity to the devices they are decoupling. Even if you do the best you can, it will still be important to know if it is “good enough” before you build the product. The last place you want to find a problem is when you are making 100,000 units and finding that 1% of them are failing due to excessive noise in the PDN. The time to find this out is as close to the beginning of the design process as possible, and the only way to determine this is by using analysis tools that allow you to explore design space.

TIP

It is essential to try to follow the three important design guidelines above and, at the same time, to use combinations of rules of thumb, approximations, and numerical simulation tools to predict the impedance profiles and voltage noise under typical and worst-case conditions.

The most important principle to follow for cost-effective design is to add appropriate analysis as early in the design cycle as possible. This will reduce the surprises as the design progresses and result in a product with acceptable performance at the lowest cost and that works the first time.

13.4 Establishing the Target Impedance Is Hard

The first step in designing the PDN is to establish the target impedance. This must be done separately and independently for each voltage rail to all the chips on the board. Some designs may use as many as 10 different voltages. In each one, the target impedance may vary with frequency due to the specific current spectrum of the chip.

Suppose that the current from the chip on one rail is a sine wave, with a peak-to-peak value of 1 A. The amplitude of the sine wave of current will be 0.5 A. This current from the chip is shown in Figure 13-4 in both the time domain and the frequency domain.

Figure 13-4 Example of the current waveform in the time domain (top) and the frequency domain (bottom) for a sine-wave current draw.

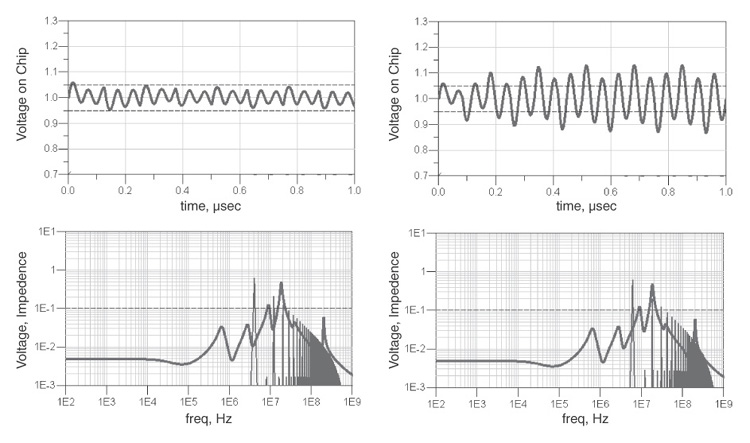

When this frequency component of the current flows through the specific impedance profile of the PDN, a voltage noise will be generated in the PDN. An example of an impedance profile with the frequency component of the current, and the resulting time-domain voltage noise across the chip pads, is shown in Figure 13-5.

Figure 13-5 Voltage noise on the chip pads (top) as the sine-wave current flows through the PDN impedance profile of simulated PDN (bottom). The spike in the PDN profile at about 20 MHz shows where the sine-wave-frequency component of the current is with respect to the PDN impedance peaks.

When the sine-wave current passes through an impedance that is too large, the voltage generated is above the ripple spec, which is typically ±5%, shown as the reference lines.

There is the potential for the current draw through a chip to be at almost any frequency from DC to above the clock frequency. This means that unless the precise current spectrum from the chip is well known, for all the possible microcode that could be running through it, we have to assume that the peak current could be anywhere from DC to the bandwidth of the signals.

In a few rare cases, if it is known that the chip processing will have a high-frequency fall off the current draw above some frequency, it may be possible to put some constraints on the current spectrum. This should always be done whenever possible.

While the current draw from a chip is rarely a pure sine wave, there are always sine-wave-frequency components in the current. The precise spectrum of the current amplitudes will interact with the impedance profile of the PDN completely independently of each other, but the resulting voltage waves will add together. Sometimes they can add and still meet the ripple spec, while at other times, they can add and exceed the ripple spec, depending on the precise overlap of current peaks and impedance peaks.

Figure 13-6 shows an example of a 1-A peak-to-peak square wave current draw for two slightly different modulation frequencies. The square wave current will have sine-wave-frequency components at odd multiples of the square wave frequency. Above roughly the fifth harmonic, depending on the rise time, the amplitude of the sine-wave harmonics will drop off much faster than 1/f. As the modulation frequency changes, the frequency distribution of the harmonics shifts and interacts differently with the PDN impedance profile.

Figure 13-6 The resulting ripple noise when the same 1 A current draw has a slightly different modulation frequency, where one of the harmonic components overlaps an impedance peak of the PDN impedance profile.

A very slight frequency shift in the modulation of the current can mean the difference between acceptable performance and failure. Unfortunately, the engineer designing the PDN has very little control of the current draw spectrum of the chip. It is whatever the chip is going to do, depending on its operation.

This means that unless there is precise information about the specific, worst-case spectrum of the current draw of the chip, a conservative design must assume a worst-case current that could occur at any frequency from DC to the bandwidth of the clock, which is a few times the clock frequency.

In practice, it is not the peak current but the maximum transient current that interacts with the higher frequencies of the PDN. If there is a steady-state DC current draw from the chip, the sense lines of the VRM can usually compensate to keep the rail voltage close to the specified voltage value. It’s when the current changes from the DC value, either increasing or decreasing, at frequencies above the response frequency of the VRM, that the current will interact with the PDN impedance.

The maximum impedance for the PDN, the target impedance, is established based on the highest impedance that will create a voltage drop still below the acceptable ripple spec. This is given by:

or:

where:

Vdd = supply voltage for a specific rail

Itransient = worst-case transient current

ZPDN = impedance of the PDN at some frequency

Ztarget = target impedance, the maximum allowable impedance of the PDN

Vnoise = worst-case noise on the PDN

ripple% = ripple allowed, assumed to be ±5% in this example

The optimum PDN impedance should be below the target impedance but not too far below the target impedance.

If the PDN impedance is kept below the target impedance at every frequency, the worst-case voltage noise generated across it as the worst case, maximum transient current flows through it will be less than the ripple spec. If the PDN impedance is much below the target impedance, it means the PDN was overdesigned and costs more than it needs to.

TIP

Whenever possible, the peak transient current should be used in estimating the target impedance. When the peak transient current is not available, it can be roughly estimated from the maximum current draw or from the power consumption of the chip.

While the worst-case transient current is what is important, rarely is this provided in a spec sheet. Rather, it is the worst-case peak current per rail that is on spec sheets. After all, this is important to estimate how large a voltage regulator module is needed. It must be capable of supplying the maximum current draw at the rated voltage.

The peak current could be mostly DC with a 10% transient current, or it could be a very low quiescent current with most of the peak current being transient that would last only for a few microseconds. Without special knowledge of the behavior of the chips in each application, the conservative design has to plan for the worst case.

What fraction of the maximum current is transient? Obviously, it depends on the function of the chip. It could vary from 1% to 99%, depending on the application. As a rough, general rule of thumb, without any special knowledge, the transient current can be estimated as being half of the maximum current:

where:

Itransient = worst-case transient current from the chip

Imax = maximum total current from the chip

Alternatively, the worst-case power dissipation of the chip will always be provided in a chip’s specs since this is critical information when designing the thermal management approach for the package. It is not usually separated by voltage rail, so some assumptions would have to be made on the power consumption of each rail.

However, given the power consumption per voltage rail, the peak current draw of a chip can be estimated from:

And from this, the target impedance can be evaluated as:

where:

Ipeak = worst-case peak current, in Amps

Pmax = worst-case power dissipation, in watts

Vdd = voltage rail, in volts

ripple% = ripple spec, in %

2 = comes from the transient current being ½ the peak current

For example, if the ripple spec is 5%, the target impedance is:

In the case of a 1-volt rail and 1-watt power dissipation device, the target impedance would be about 0.1 Ohm:

Some chip vendors, especially FPGA vendors, also provide calculation tools that allow simple estimates of the current draw of specific voltage rails, depending on the gate utilization. These can be used to estimate the target impedance specs of the rails. An example of the results of using one such analysis for the Altera Stratix II GX FPGA is shown in Figure 13-7.

Figure 13-7 Example of a calculation of the target impedance of different voltage rails based on gate utilization of an Altera FPGA.

Finally, the current requirements of the I/O voltage rails, typically referred to as either the Vcc or Vddq rails, can be estimated based on the number of gates that are switching.

If each output gate drives a transmission line with some characteristic impedance, then the load it sees, if only for a round-trip time, is the same as the characteristic impedance of the line it drives.

If n gates could switch simultaneously, the transient current draw could be:

And the target impedance of the VCC rail would be:

Itransient = worst-case transient current

n = number of I/Os that could switch simultaneously

Vcc = voltage rail

Z0 = characteristic impedance of the transmission lines

For example, if the lines are all 50 Ohms, and there are 32 bits switching simultaneously, the target impedance for the Vcc rail would be:

Even with the peak current and the target impedance established, the current could be fluctuating at almost any frequency due to the specific microcode or application running. This means that unless there is information to the contrary, it must be assumed this is the target impedance, flat from DC to very high frequency.

TIP

The goal in designing the PDN is to keep the impedance of the PDN interconnects below this target value over a very wide bandwidth. A PDN above the target impedance may result in excessive ripple. A PDN impedance much below the target impedance may be overdesigned and more expensive than it needs to be.

When the impedance profile is kept below the target value, the worst-case voltage rail noise will be less than the ripple spec. An example of a successful impedance profile is shown in Figure 13-8.

Figure 13-8 When the impedance profile (bottom) is below the target impedance, the worst-case voltage noise (top) is below the ripple spec. The square wave is the current draw by the chip, while the flat curve is the voltage on the supply rail.

However, if there is a peak in the impedance profile that exceeds the target spec, and if the worst-case current happens to fall on top of this peak impedance, there is a chance that the ripple spec may be exceeded. This is shown in Figure 13-9. In this example, the step current change excites the peak impedance, and we see the characteristic ringing at the peak frequency.

Figure 13-9 When the impedance exceeds the target spec (bottom) and the current’s peak frequency hits this impedance peak, excess ripple can result (top). The square wave is the current draw through the chip. The ringing wave is the voltage on the supply rail. Inset is an example of the measured voltage noise on a PDN, showing the typical ringing response of a peak in the impedance profile.

Peak impedances in the PDN impedance profile are an important design feature to watch out for. Many aspects of PDN impedance design, especially the selection of capacitor values, are driven by the desire to reduce the peak impedances in the PDN.

13.5 Every Product Has a Unique PDN Requirement

One of the greatest sources of confusion in PDN design is created by taking the PDN design features of one product and blindly applying them to another product.

TIP

Unlike with the design of signal paths, where the design rules in one product can often be applied to other products of similar bandwidth, the behavior of the PDN depends on the interactions of all of its parts, and the goals and constraints vary widely from product to product.

The PDN is one giant net rather than a large number of individual nets, with only a small amount of local coupling between them. In this respect, the PDN net is like an ecosystem of interconnects. While it may be possible to suggest an optimized design based on optimizing individual elements, the most cost-effective designs are based on optimizing the entire ecology of all the elements, across the entire frequency range.

The voltage level of the rails can vary from 5 v to less than 1 v, depending on the chip type and technology node. The ripple spec may be as large as 10% in some devices or as low as 0.5% in others, such as phase locked loop (PLL) supplies or the analog-to-digital converter (ADC) reference voltage rails.

The current draw from chips can vary from more than 200 A in high-end graphics chips and processors to as low as 1 mA for some low-power microcontrollers. This means that the target impedance values can vary from below 1 mOhm for high-end chips to more than 100 Ohms. This is five orders of magnitude in impedance.

There could be as many as 10 different voltage rails in some designs, many sharing the same layer, while other designs may have just one voltage and ground. Some of the planes may be solid; others may be irregularly shaped and full of clearance holes.

TIP

This wide variety of applications and board constraints means no one solution is going to fit all. Instead, each design must be treated as a custom design.

It is dangerous to blindly apply the specific features of one design to another design. However, a general strategy can be followed to arrive at an acceptable impedance profile.

13.6 Engineering the PDN

It is remarkable that so complex a structure as the PDN interconnects can be partitioned in the frequency domain into just five simple regions. Figure 13-10 diagrams these five regions, based on the frequency ranges they can influence.

At the lowest frequency, the VRM dominates the impedance the chip sees when looking into the PDN. Of course, the series resistance of the interconnects can also set a limit on the lowest impedance of the PDN if it is larger than the VRM impedance. The VRM performance dominates from DC to about 10 kHz.

The next higher frequency regime, roughly in the 10-kHz to 100-kHz range, is dominated by the bulk decoupling capacitors. These are typically electrolytic and tantalum capacitors that provide a low impedance beyond where the VRM can go.

The highest-frequency impedance is set by the on-die capacitance. This is the only feature in the PDN that the chip sees in the GHz regime. It generally has the lowest loop inductance associated with it and offers the lowest impedance at the highest frequency of any element in the PDN.

TIP

Every chip interfaces to the board it is mounted to through some mounting inductance. Usually, this is dominated by the package, the board vias, and the spreading inductance of the via contacts into the power, and ground planes of the board.

The PDN interconnects in the package are generally inductive. This means that at high frequency, they will act as a high-impedance path. Even if the board on which the package is mounted were designed with an impedance of a dead short, the chip would be looking at this short through the chip attach and package attach inductance, and it would see an impedance limited by these inductances.

The series inductance of the package’s PDN will always limit the highest frequency at which the chip will see the board-level PDN. This acts as a high-frequency limit to the board-level PDN design, and above this package-limited frequency, the impedance the chip sees will be determined by the on-die capacitance and any capacitance in the package. This limit is generally in the 10- to 100-MHz range. Above this frequency, the impedance the chip sees is all about the package and the chip.

TIP

The frequency region that board-level PDN design can influence is roughly from the 100-kHz range up to about 100-MHz. This is where the planes of the board and the multilayer ceramic chip capacitors (MLCC) can play a role.

These capacitors—typically in sizes of 60 mils × 30 mils and referred to as 0603 or 40 mils × 20 mils and referred to as 0402—are called chip capacitors because they look like small “chips” of something on a board. Figure 13-11 is a close-up of some typical multilayer ceramic chip (MLCC) capacitors on a small memory board.

13.7 The VRM

The low-frequency impedance is set by the VRM. All VRMs, regardless of regulator type, have an output impedance profile. This can easily be measured using a two-port impedance analyzer.

An example of the measured impedance profile of a typical VRM is shown in Figure 13-12. In this example, the impedance looking into the output leads of the VRM was measured when the regulator was turned off and when it was turned on and providing regulation. In addition, the impedance of a simple two-capacitor model is superimposed.

Figure 13-12 Measured impedance profile, from 10 Hz to 40 MHz, using an Ultimetrix Impedance Analyzer for a typical VRM, showing the impedance when on and when turned off and showing the modeled impedance based on a two-capacitor model.

This illustrates that when the regulator is off, the behavior seen at the output leads is almost exactly as predicted by a two-capacitor model, each capacitor being modeled as an RLC circuit.

This behavior corresponds to the two bulk decoupling capacitors associated with the VRM. The 910 µF capacitor is an electrolytic capacitor, while the 34 µF capacitor is a tantalum capacitor. This impedance profile is for the passive network of the leads and the two capacitors.

When the regulator is turned on, its output impedance drops by orders of magnitude at low frequency. This is exactly what is expected from a regulator. The output voltage is kept constant, independently of the current load. A large change in current produces a small change in voltage, the behavior of a low impedance. However, we see that in the actual behavior of the VRM, this low impedance is maintained from DC only up to the kHz range.

Above about 1 kHz, the impedance is seen to increase, until it matches the impedance of the bulk capacitor at about 4 kHz, at which frequency the impedance is brought down by the passive capacitor network on the regulator. Above about 1 kHz, the output impedance of the VRM is completely due to the passive capacitors, and the active regulation plays no role at all. Whether the regulator is on or off, the impedance is the same.

This is a slight exaggeration because the regulator fights with the capacitance of the passive network, and when the regulator is turned on, its impedance is actually higher than if it were literally turned off.

TIP

The output impedance of most VRMs is low up to the kHz regime. Beyond this, what brings the impedance down is the bulk capacitors associated with the regulator.

The total amount of capacitance needed on a board in the form of electrolytic or tantalum capacitors can be estimated based on achieving the target impedance at the frequency where the VRM is no longer able to maintain the low impedance.

The capacitance is chosen so that its impedance at 1 kHz is less than the target impedance. The minimum capacitance needed is given by:

where:

Cbulk = minimum bulk capacitance needed, in µF

Ztarget = target PDN impedance, in Ohms

1 kHz = frequency at which the VRM is no longer able to provide low impedance

For example, if the target impedance is 0.1 Ohm, the minimum bulk capacitance needed is about 1600 µF. Of course, this is only a rough estimate, but it is a good starting place. When it comes to establishing the actual target values of the capacitance, the interactions of the VRM effective inductance and the capacitor’s capacitance must be taken into account with a SPICE simulation.

The low-frequency model of a VRM can be easily approximated by a simple RL model with a voltage source. The equivalent circuit model of the VRM and bulk decoupling capacitor is shown in Figure 13-13. This circuit can be used to optimize the capacitor value to keep the impedance below the target value at low frequency.

Figure 13-13 Typical equivalent circuit model of a VRM and bulk decoupling capacitor with typical values for each element.

13.8 Simulating Impedance with SPICE

Simulating the impedance profiles of different circuit models is essential in PDN design. Luckily, most of the simple circuits that need to be analyzed can be simulated with free versions of SPICE, such as QUCS, that can be downloaded from the Internet.

TIP

The secret to using SPICE to perform impedance simulations is to build an impedance analyzer as a SPICE circuit. This is done with a single element in SPICE: a constant-current AC current source.

This element is defined as a constant-current sine-wave source, outputting a sine wave of current with a constant amplitude. The output voltage of this element will be whatever it needs to be to always output a constant-amplitude sine wave of current. The frequency of the current is set by the frequency of the frequency-domain simulation. An example of a SPICE impedance analyzer is shown in Figure 13-14.

The amplitude of the constant current source is set to 1 A with a phase of 0. The voltage across the constant current source will depend on the impedance of whatever is connected across the leads. This voltage generated will be given by:

where:

V = voltage generated across the current source, in volts

I(f ) = current from the source, a constant 1-A amplitude sine wave

Z(f ) = impedance of the device connected across the current source, in Ohms

We set the current amplitude to be exactly 1 A. This means the voltage generated across the current source is numerically the impedance in Ohms. The impedance of the circuit connected may vary with frequency. As the 1-A constant amplitude sine wave flows through it, a voltage will be generated that is numerically equal to the impedance. The phase of the voltage will even track the phase of the impedance.

A large shunt resistor, in this case 1 TOhm, is connected across the current source. This is to keep SPICE from halting due to an error. SPICE wants to see a DC path to ground for all nodes. Without the resistor, an open across the constant-current source could result in an infinite voltage, causing an error.

With this circuit, the impedance of any circuit model can be simulated. It’s actually the voltage across the current source that is simulated, but this is equal to the impedance of the circuit. The impedance of the two-capacitor model in the VRM was simulated using this SPICE impedance analyzer.

13.9 On-Die Capacitance

The impedance at the highest frequency is established by the on-die decoupling capacitance. This arises from three general sources: the capacitance between the power and ground rail metallization, the gate capacitance from all the p and n junctions, and any added capacitance.

The largest component is from the gate capacitance distributed over the die. Figure 13-15 shows a typical CMOS circuit, found by the millions on most chips, and by the billions for some chips. At any one time, one of the gates is on, and the other is off.

This means that the gate capacitance of one of the gates, either the p channel or the n channel, is connected between the power and ground rails on the die. The capacitance per area associated with the gate is simply approximated by:

where:

C/A = capacitance per area, in F/m2

Dk = dielectric constant of the oxide ~3.9 for SiO2

h = dielectric thickness, in meters

In general, the shorter the channel length, the thinner the gate oxide. As a rough rule of thumb, the gate oxide thickness is about 2 nm per 100 nm of channel length. However, below about 100-nm channel length, the scaling of h flattens out due to higher leakage currents, but then the dielectric constant is increased with the use of “high-Dk” gate insulator materials. This keeps the rule of thumb a good approximation even below 100 nm channel lengths.

For the 130-nm channel length node, the capacitance per area is about:

Of course, not all the die is gate area. If we assume that 10% of the surface of the die is gate capacitance, then we see that as a rough rule of thumb, the on-die decoupling capacitance on a 130-nm technology chip due to its p and n junctions is about:

As the technology node advances and the channel length decreases, the gate capacitance per area will increase, but the total gate area on a die will stay about the same. This means the capacitance per unit of die surface area will increase inversely with the technology node.

The capacitance of 65-nm chips is about 260 nF/cm2. This estimate suggests that for a die that could be 2 cm × 2 cm, close to the largest mask size in volume production, at 65-nm channel length, the on-die decoupling capacitance could easily be in excess of 1000 nF.

A typical chip in many embedded processors, only 1 cm × 1 cm, would have as much as 260 nF of capacitance. If the gate utilization on the die were larger, the on-die capacitance could be higher as well.

TIP

At high frequency, it is the on-die capacitance that provides the low impedance.

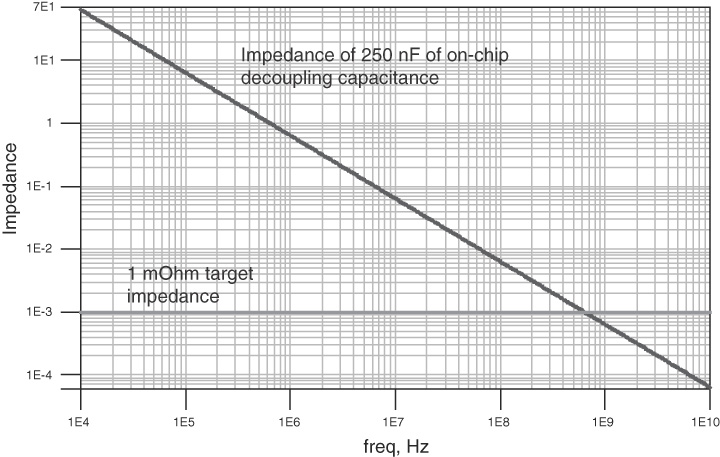

The impedance profile of a capacitance that is 250 nF is shown in Figure 13-16. In this example, the on-die capacitance provides an impedance below 1 mOhm at frequencies above 800 MHz. All high-frequency decoupling is provided by this mechanism.

Figure 13-16 Impedance, in Ohms, provided by 250 nF of on-chip decoupling capacitance, typical of a die that is 65 nm and 1 cm on a side.

If the target impedance were 10 mOhms, the on-die capacitance would provide significant decoupling for frequencies above about 100 MHz.

13.10 The Package Barrier

Between the pads on the chip and the pads on the circuit board is typically the IC package. Styles range from lead frame-based packages to miniature circuit board–based packages to minimalist or chip-scale packages.

The loop inductance of the package leads in the power/ground distribution path is in series with the pads of the chip to the pads on the circuit board. This series inductance creates an impedance barrier. The impedance of an inductance is given by:

where:

Z = impedance, in Ohms

f = frequency, in Hz

L = inductance, in H

For example, at 100 MHz, the impedance of a 0.1-nH inductor is about 0.06 Ohm. Even if the impedance of the PDN on the board were implemented as a dead short, the chip, looking through the package, would see a PDN impedance of 0.06 Ohm at 100 MHz. Of course, this is why on-die and on-package capacitance is so important.

Low-cost packages are often leaded, either as a stamped lead frame or as a two-layer printed circuit board. The loop inductance of adjacent leads is roughly about 20 nH/inch of length. For package leads 0.25 inches long, the loop inductance of a single power and ground lead pair can be as much as 5 nH. In the case of chip-scale packages, the loop inductance of a pair of leads may be on the order of 2 nH.

In multilayer BGA packages with at least four layers, a dedicated power and ground plane is often used. The loop inductance can be reduced to less than 1 nH per power and ground pair, limited by the roughly 50 mil total path length solder ball and its associated package via.

In small packages, there may be only a few power and ground pairs. In large BGA packages, there can be hundreds of pairs. This means the effective package lead inductance can vary from 1 nH to as low as 1 pH.

In addition to the package leads, there is also the loop inductance of the vias into the circuit board and the spreading inductance launching current into the power and ground planes of the board. When the package lead inductance is small, the board via and spreading inductance can limit the loop inductance as seen by the chip.

When the interactions of the on-die capacitance are added to the package inductance, the behavior is even more complicated. Figure 13-17 shows the impedance profile the chip sees looking into a board that has a short for the PDN. The impedance profile is limited by the package inductance.

Figure 13-17 Impedance seen by the chip when the board is a dead short for different package lead inductances.

This suggests that no matter what the board-level PDN does, it can never reduce the impedance the chip sees below the package lead impedance. When the package equivalent lead inductance is 0.1 nH, the board cannot influence the impedance the chip sees to below 10 mOhms at frequencies above 10 MHz.

Of course, in this example, there is a large parallel resonance impedance peak due to the interactions of the package inductance and on-die capacitance. Many times, these can be suppressed by using on-package decoupling capacitors.

For example, Figure 13-18 shows the reduction in peak impedance for the case of 0.1 nH of lead inductance with the addition of 10 different 700-nF capacitors, each with 50 pH of ESL mounted to the package.

Figure 13-18 Suppression of package and on-die capacitance parallel resonances with on-package decoupling capacitors, as seen by the chip, if the board-level impedance were a dead short.

TIP

When establishing the design goals of the board-level PDN, the high-frequency limit to where the board-level impedance can be effective to the chip is determined by the frequency at which the impedance from the combination of the package leads, board vias, and spreading inductance exceeds the target impedance.

The relationship between thepackage lead inductance, maximum effective frequency and target impedance corresponds to:

Ztarget = target impedance, in Ohms

Lpkg = equivalent lead inductance of all the PDN paths in the package

fmax = highest useful frequency for the board-level PDN

As a starting place, Figure 13-19 shows the map of the target impedance and package inductance for a specific maximum frequency of 100 MHz. If a product design falls below the line—for example, if the target impedance is very low and the package lead inductance is very high—the maximum frequency for the board to be effective is below 100 MHz. In this case, the package severely limits the PDN's performance.

Figure 13-19 Map of the combination of target impedance and package lead inductance that has a maximum board-level frequency limit of 100 MHz. If a design is above the line, the board-level impedance will play a role at frequencies higher than 100 MHz; if the combination falls below the line, the board-level impedance will play a role at less than 100 MHz.

If a design falls above the line—for example, if the lead inductance is very low and the target impedance is high—the maximum frequency range for the board to still be effective is above 100 MHz.

As a rough rule of thumb, with about 20 nH/inch of loop inductance in a package lead and 0.05 inch of package lead length in a CSP package, the loop inductance per power and ground lead pair is about 1 nH. With 10 power and ground pin pairs in parallel, this is about 0.1 nH of equivalent lead inductance in a typical package that might have 10 pairs of PDN leads. If the target impedance were below about 0.6 Ohm, the board would not be effective much above 100 MHz.

Though it is difficult to generalize, as we've said throughout this book, sometimes an okay answer now is better than a good answer late. In general, the combination of packages and target impedance limits the board-level impedance to be effective under about 100 MHz. This is why the board-level PDN design goal is typically set to no higher than 100 MHz unless there is other information to the contrary.

While it is possible to set the high-frequency limit higher, achieving higher-frequency design limits is often much more expensive and should be done only when it is known to be important.

When on-package decoupling capacitors are provided, the maximum frequency at which the board-level impedance can be effective is often lower than 100 MHz.

The lead inductance also acts as a filter to keep high-frequency noise from the chip’s PDN off the board. When the core gates switch, the PDN rail voltage is kept low by the on-die capacitance. After all, if there is excessive noise on the chip’s PDN pads, this will cause its own problem. Any voltage noise on the chip rails will be further filtered by the lead inductance before it gets to the board.

Figure 13-20 shows an example of the simulated noise rejection from the chip pads to the board for different package lead inductances and a board-level impedance of 10 mOhms.

Figure 13-20 Relative noise injected onto the board from the chip pads for different package lead inductances. This is for the special case of the board-level impedance at or below 10 mOhms.

When the target impedance is 10 mOhms, and the package lead inductance is 0.1 nH, the noise rejection is about 0.1 or −20 dB at 100 MHz. Less than 10% of the on-chip noise is coupled into the board. The higher the package lead inductance, the less on-chip noise gets on the board. This is why very little noise above about 100 MHz gets onto the board-level PDN from the chip.

In the absence of a complete package model including the PDN paths, it is difficult to do much more than roughly estimate the impact of the package on the PDN path.

13.11 The PDN with No Decoupling Capacitors

At low frequency, the VRM and the bulk decoupling capacitors provide the low impedance in the PDN. At high frequency, the on-die capacitance and on-package capacitance provide the low impedance to the PDN. We can see what the complete impedance profile might look like for this simple case using typical model parameter values.

Figure 13-21 is the simulated impedance profile for the case of power and ground planes in the board, with no added decoupling capacitors. It includes a simple VRM with bulk decoupling capacitor and 50 nF of on-die capacitance.

If the target impedance were 1 Ohm, this board would work just fine, with no added decoupling capacitors. It would not matter how many or what value capacitors were added to the board; the PDN would still have acceptable noise. Even if the target value were as low as 0.2 Ohm, as long as the current spectrum did not have any worst-case amplitude spikes in the 5 MHz to 20 MHz range, this board might work just fine.

This is why many boards work no matter what is done at the board level: because of the on-die capacitance and large bulk decoupling capacitors that are part of the VRM. This is also why it is sometimes reported that decoupling capacitors have been removed from the board, and it works just fine, thereby starting the myth that decoupling capacitors aren’t very important. However, there is no guarantee that this condition will apply to your specific product application. Different chips with different current requirements and different on-die capacitance with different packages and the same board can have very different performance.

TIP

In order to have confidence in a PDN design, the board-level designer must have information about the package model and the on-die capacitance, as well as the current spectrum of the chip.

While the package model and the on-die capacitance, as well as the current spectrum of the chip, are important, it is also difficult to get this information from most semiconductor suppliers. We still have to design the board-level decoupling in the absence of all the important information. In such cases, it’s important to make some reasonable assumptions to base the board-level design around.

The two most common board-level design assumptions are that the package lead inductance will limit the frequency where the board-level impedance is important to below 100 MHz and that the current draw and target impedance can be estimated based on the worst-case power dissipation of the chips.

When the target impedance is 1 Ohm or above, the board design and decoupling capacitors may not play a very important role. However, achieving target impedances below 1 Ohm requires careful selection of capacitors and their integration into boards to optimize their performance.

With the correct number, value, and implementation of decoupling capacitors and power and ground planes to connect them to the VRM and the package leads, we can engineer the PDN impedance down below the mOhm range.

TIP

Knowing the behavior of individual capacitors, combinations of capacitors, and how capacitors interact with planes will lay the foundation for the most cost-effective PDN designs.

13.12 The MLCC Capacitor

An ideal capacitor has an impedance that drops off inversely with increasing frequency, given by:

where:

Z = impedance, in Ohms

f = frequency, in Hz

C = capacitance, in F

For example, the impedance profile of four ideal capacitors is shown in Figure 13-22. It is easy to believe that if this is the behavior of a capacitor, then why can't we just add a single, large capacitor to a board and use it to provide low impedance at ever higher frequencies?

The problem with this approach is that the behavior of a real capacitor is not quite the same as that of an ideal capacitor. An example of the measured impedance of a real 0603 capacitor is shown in Figure 13-23. While the impedance starts out like that of an ideal capacitor, unlike an ideal capacitor, a real capacitor reaches a lowest impedance and then begins to increase in value.

A real capacitor can be approximated by a simple RLC circuit model to very high frequency. The simulated impedance of an ideal RLC circuit is an excellent match to this measured performance. Figure 13-24 shows the comparison of the measured and simulated impedance for the specific values:

R = 0.017 Ohm

C = 180 nF

L = 1.3 nH

In this model, the R, L, and C parameter values are absolutely constant with frequency. They are each ideal elements. However, when connected together in series, the resulting impedance profile of the combination of ideal elements is remarkably close to the actual measured impedance of the capacitor.

TIP

The fact that an ideal RLC circuit matches the behavior of a real capacitor makes this RLC circuit model incredibility useful for modeling real capacitors, even up to very high bandwidth, above 1 GHz.

The composite behavior of an RLC model is different than the behavior of any single element. These are compared in Figure 13-25.

At low frequency, the impedance of the RLC circuit is related to the ideal capacitance. At high frequency, the impedance of the RLC circuit is related to the ideal inductance. The lowest impedance of the RLC circuit is limited by the ideal resistance.

The frequency at which the impedance is the lowest is called the self-resonant frequency (SRF) and is given by:

where:

fSRF = self-resonant frequency, in MHz

L = equivalent series inductance, in nH

C = capacitance, in nF

For example, for the real capacitor shown earlier, the self-resonance frequency is estimated to be:

As can be seen in the earlier example, this is very close to the measured SRF of this capacitor.

Near the SRF, the impedance profile of the RLC circuit is not the same as the ideal L or C. It differs in a complicated way that also depends on the R value. This makes it difficult to perform simple analytical estimates but can be easily simulated with any free version of SPICE (see www.beTheSignal.com).

TIP

Above the SRF, the impedance is dominated by the inductance. Reducing the high-frequency impedance is about reducing the inductance. This is the most important engineering term to adjust in the selection of capacitors and their integration into the board.

TIP

Change the way you think of a capacitor. An MLCC capacitor is not a capacitor; it is an inductor with a DC block. Everything about implementing a capacitor is about the mounting inductance design, not about its capacitance.

The R is related to the series resistance of the metallization in the planes that make up the capacitors. The C is about the number of layers in the capacitor, the area of the internal planes, their separation, and dielectric constant.

13.13 The Equivalent Series Inductance

The L, often referred to as the equivalent series inductance (ESL), is more about how the capacitor is mounted to the board or test fixture than the capacitor itself.

Even though many capacitor vendors offer an “intrinsic” inductance for their capacitor components, the inductance they provide is absolutely worthless and has no value in determining the performance of real capacitors. Instead, we will see how the ESL is affected by the mounting geometry of the capacitor.

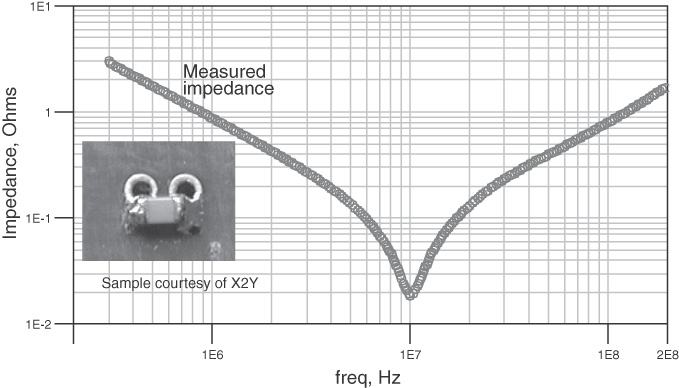

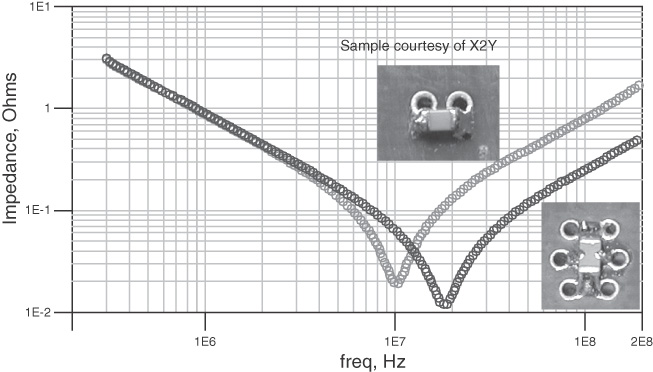

Some capacitors are capable of achieving lower ESL for the same mounting features by nature of their design. It is not that they have lower intrinsic ESL but that they enable lower mounted inductance because of design features. For example, an X2Y capacitor, a type of interdigitated capacitor, will have a lower ESL under typical mounting conditions than an 0603. Figure 13-26 compares the measured impedance profile of an 0603 capacitor and an X2Y capacitor on the same board.

Figure 13-26 Measured impedance profiles of a conventional 0603 capacitor and an X2Y interdigitated capacitor on the same board. They have exactly the same value of capacitance, seen at low frequency, but very different ESL.

The impedance at low frequency for these two different capacitors is nearly the same, but their high-frequency impedance is very different. This is primarily due to the fact that the single X2Y capacitor with four terminals is really like four separate capacitors in parallel. The parallel combination of their loop inductances reduces the equivalent loop inductance of the whole capacitor. This can be a significant advantage in some designs.

The complete path of the power and return currents from the pads of the BGA package to the capacitor is shown in Figure 13-27. The ESL of the capacitor is, to first order, related to design features in this path.

The ESL associated with the capacitor and its path to the package can be divided into four regions:

1. The loop inductance of the surface traces and top of the plane’s cavity

2. The loop inductance of the vias from the capacitor pads to the top of the plane cavity

3. The spreading inductance from the capacitor vias to the vias of the BGA

4. The loop inductance from the cavity under the package to the leads or solder balls of the package

TIP

Different design techniques should be applied to each region in order to engineer the lowest ESL possible.

When only a few capacitors are used on a board, and the current distributions in the planes from the capacitors to the pins of the package do not substantially overlap, the ESL of each capacitor is the loop inductance of the entire path. In this case, each capacitor behaves independently, and it is possible to accurately simulate the impedance profile of the parallel combinations of the capacitors on the board by using a simple SPICE model and simulation. The capacitors are independent.

However, when the current distributions overlap, such as when the capacitors are clustered in one region of the board or when many capacitors surround a package, the spreading inductance in the cavity of the power and ground cavity will be a complicated function of the location of the capacitors, their values, and the location of the package pins.

This is why it is useful to separate the ESL of a capacitor into the mounting inductance and the spreading inductance in the cavity. When the capacitors do not interact with each other, the cavity spreading inductance can be combined with the mounting inductance into the ESL. When the capacitors’ spreading inductances interact, the only accurate way of estimating the impedance profile seen by the package is with a 3D simulator, which takes into account the current distribution of each capacitor. In this case, the location of the capacitors and the location of the power and ground pins in the package will be important.

TIP

It’s always a good practice to separate the mounting inductance and the cavity spreading inductance. They can be combined when needed into one number to estimate the ESL.

13.14 Approximating Loop Inductance

There are only a few geometries for which there are simple approximations for loop inductance:

• Any uniform transmission line

• The special case of two round rods

• A pair of long, wide conductors with a thin dielectric between them

• The special case of edge-to-edge connections to planes

• Spreading inductance from a via to a distant ring

• Spreading inductance between two via contacts in a plane

The loop inductance of any uniform transmission line, assuming that the signal and return paths are shorted at the far end, is given by:

where:

Lloop = loop inductance, in nH

Z0 = characteristic impedance, in Ohms

TD = time delay of the transmission line, in nsec

Len = length of the transmission line, in inches

v = speed of light in the material, in inches/nsec

When the impedance of the line is 50 Ohms, such as a surface microstrip trace that is 10 mils wide and dielectric spacing in FR4 to the return path of 5 mils, the loop inductance is roughly:

For a surface trace that is 0.2 inches long, the loop inductance of the surface trace can be as large as 1.7 nH.

This simple relationship suggests the two important design guidelines for engineering the lowest loop inductance possible for any structure that sort of looks like a uniform transmission line:

• Design the lowest a characteristic impedance possible.

• Keep the lengths as short as possible.

A special structure for which there is an analytical relationship between the geometry and loop inductance is two round rods, as illustrated in Figure 13-28.

The loop inductance from the end of one rod, down the rod, shorting across the end of the other rod and back again to the front is related to only the three geometry terms in Figure 13-28. If the length is increased, the loop inductance will increase. If the rods are brought closer together, their partial mutual inductance will help to cancel some of the total field lines, and the loop inductance will be reduced. If the diameter of the rods is increased, the loop inductance will be decreased.

There are a number of analytical approximations for the loop inductance of these two rods. The simplest approximation is:

where:

Lloop = loop inductance, in pH

h = length of the rods, in mils

s = center-to-center pitch of the rods, in mils

D = diameter of each rod, in mils

For example, for 2 vias, 10 mils in diameter, on 50-mil centers and 100 mils long going through an entire board, the loop inductance is roughly:

The uniform transmission-line model gives the same constant loop inductance per length for the two rods, independent of the rod length. For the case of 10-mil via diameter and 50-mil centers, the loop inductance per pair-length is roughly 23 nH/inch, or 23 pH/mil. When the center-to-center pitch is 40 mils, typical of high-density BGAs, the loop inductance per length is 21 nH/inch, or 21 pH/mil.

TIP

As a rough rule of thumb, if you want to carry around one value for the loop inductance of a pair of vias, a rough estimate is about 21 pH/mil. This is a reasonable estimate for the loop inductance contribution from vias.

When the two conductors that make up the loop are wide and closely spaced, such as with two plane segments shown in Figure 13-29, the loop inductance is approximated by:

where:

Lloop = loop inductance between the planes, in pH

Len = length of the planes, in inches

w = width of the planes, in inches

h = thickness between the two planes in mils

For example, if the planes are 2 inches long and 0.5 inches wide, with 4 mils between them, the loop inductance would be:

When the length of the trace is equal to the width, the structure looks like a square, and the ratio of Len/w is always 1. The loop inductance of this square section of plane is the first part of the equation and is called the loop inductance per square, or the sheet inductance:

Any square piece of a pair of planes has the same loop inductance. The thinner the dielectric between them, the lower the sheet loop inductance.

This approximation assumes that the currents flow in a uniform sheet down the top trace and back to the bottom, uniformly distributed along both sheets. When the contacts are spread along the edge of the strip, this is a good approximation. However, in via contacts to planes, the current does not flow uniformly. Instead, it spreads out from sources and constricts into sinks. An example of the current flow map in a plane between two via contacts is shown Figure 13-30.

Figure 13-30 Current flow pattern in the top plane from a via source point to a via sink point into the bottom plane. Simulated with HyperLynx.

The spreading inductance in planes is the most important property of planes and is discussed in detail in Chapter 6. It contributes to the additional loop inductance between point contacts in planes over their sheet inductance when contacts are at vias rather than at an edge of the plane.

The narrow contact regions of vias increase the current density and increase the local loop inductance. In general, spreading inductance is complicated to calculate and usually requires a 3D field solver, as the current flow is difficult to calculate by approximation.

There is one special case for which there is an accurate approximation for spreading inductance. This is the case of current flowing from a central-ring contact to an outer, symmetrical-ring contact, where it flows into the bottom plane and then reverses back, constricting to an inner ring contact on the bottom plane. This is diagrammed in Figure 13-31.

Figure 13-31 Inner and outer contact regions on the top plane, with similar regions on the bottom plane. Spreading inductance calculation is the loop inductance from the top contact point, radially outward to the edge, down the edge, and back in to the center contact.

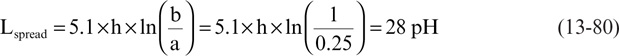

In this geometry, the loop spreading inductance is:

where:

Lspread = loop spreading inductance between the planes, in pH

a = radius of the inner contact region, in inches

b = radius of the outer contact region, in inches

h = thickness between the two planes, in mils

This assumes that the current is flowing from the center via contact to the bottom plane and returns to the inside edge of the clearance hole, and the clearance hole is just slightly larger than the via contact diameter in the bottom plane. For example, if the inner radius is 5 mils, corresponding to a 10-mil-diameter via, and the outer radius is 1 inch, corresponding to the perimeter of a package, and the dielectric thickness between the planes is 10 mils, the loop spreading inductance is:

This relationship of spreading inductance has the same form as the sheet loop inductance of a path, if we use as the number of squares:

then:

For typical cases, b/a could be on the order of 100, and the number of squares is of order 1.

In the special case of the current flow between the via contacts to a buried plane pair from a capacitor and BGA pins on the surface of a board, the loop inductance is more complicated to calculate. There are no exact analytical equations that describe this loop spreading inductance. However, by making a few assumptions, a simple approximation can be developed for the loop inductance in a pair of planes with round contact points.

Figure 13-32 illustrates the example of two via contacts positioned a distance B apart in a pair of planes and the current flow between them, spreading out and constricting in the planes.

Figure 13-32 Spreading current from one via contact to another via contact in a pair of planes. There is spreading loop inductance between the two locations.

The spreading loop inductance between these two via contacts is approximated by:

where:

Lvia−via = loop spreading inductance in the planes between the two via contacts, in pH

h = dielectric thickness between the vias, in mils

B = distance between the via centers, in mils

D = diameter of the vias, in mils

For example, if the via diameters are 10 mils and they are spaced 1 inch apart, in a pair of planes with h = 10 mils, the spreading inductance in the planes between the contacts is about:

The contribution of the spreading inductance in the planes between the vias can be as much as 1 nH. The thinner the dielectric, the lower the spreading inductance.

The lower spreading inductance in ultra-thin laminates is the real reason they offer a performance advantage over conventional FR4 for the dielectric between power and ground planes. The higher capacitance plays little role as there is far more capacitance in the on-die capacitance than in the power and ground planes.

If the connections between the capacitors and the pads of the package can be routed in planes with a cavity thickness that is not 4 mils but 1 mil or 0.5 mil, the spreading inductance in this path can be reduced from 0.4 nH with 4 mils down to 0.05 nH with a 0.5-mil-thick dielectric. An example of the cross section of a board with a 0.5-mil-thick dielectric in the power and ground planes is shown in Figure 13-33.

Figure 13-33 Cross section of a board with a 0.5-mil-thick layer of DuPont Interra HK04 laminate between the power and ground planes, close to the bottom surface of the board.

The predicted values of this approximation can be compared to the results predicted by a 3D field solver. Figure 13-34 shows the estimates of these approximations to the simulated via to via spreading inductance using the HyperLynx PI tool for two planes separated by 3 mils.

Figure 13-34 The comparison of the approximation (solid lines) and the simulated loop inductance (single dots), using HyperLynx for the case of a pair of planes separated by 3 mils.

These various approximations can be used to roughly estimate the impact of physical design features and the resulting ESL of a capacitor mounted to a board. Using these approximations, we can explore design space to determine what general design guidelines to follow.

TIP

Since each design is custom, care must be taken when applying an observation for one case and blindly applying it to another without putting in the numbers.

13.15 Optimizing the Mounting of Capacitors

The three most useful approximations for loop inductance are summarized in one place in Figure 13-35.

These approximations describe the important design trade-offs. If you want to reduce the loop inductance associated with the traces from the pads of the capacitor to the vias, there are three important design knobs to adjust:

1. Keep the depth to the top of the power/ground cavity thin.

2. Use wide surface traces.

3. Keep the length of the surface traces short.

To reduce the inductance of the vias, there are three design knobs to adjust:

1. Keep the depth to the top of the power/ground cavity short.

2. Use large-diameter vias.

3. Keep the via pitch as close as possible.

To reduce the spreading-loop inductance in the planes, there are three knobs to adjust:

1. Keep the dielectric thickness of the power/ground cavity thin.

2. Use large-diameter vias or multiple vias in contact to the cavity.

3. Place the capacitor close to the package it is decoupling. (This is only a weak dependence.)

While these are important design guidelines to be aware of, some are more important than others.

TIP

The terms that affect the total loop inductance the most should always be optimized first.

These are the terms that affect the total loop inductance the most:

1. Keep the depth to the top of the power/ground cavity short.

2. Keep the dielectric thickness of the power/ground cavity thin.

3. Use wide surface traces.

4. Keep the length of the surface traces short.

The other design features are of second- and third-order importance and can sometimes be a distraction from the first-order concerns. In general, the only way to know what is important is to put in the numbers for specific cases. Integrating these approximations in a spreadsheet allows us to easily explore design space and identify what is really important and what is not.

In the example shown in Figure 13-36, three cases are explored. In each case, an 0603 capacitor is supplying current to one power and ground pin pair in a BGA package, located some distance away. The vias are 13 mil in diameter. This estimate is for the ESL of the capacitor as though it were not interacting with other capacitors. Case 1 is the starting place, with long and narrow surface traces. The total ESL is found to be about 6.1 nH.

Figure 13-36 Analysis of three typical mounting geometries for an 0603 capacitor, analyzed with an online tool at www.beTheSignal.com.

In case 2, the surface traces are shortened and widened. The resulting ESL is 3.7 nH. Finally, in case 3, the capacitor is moved closer to the package, and the cavity thickness is decreased. The resulting loop inductance is reduced to 1.8 nH.

TIP

This example clearly shows that in typical cases, the loop inductance of the vias is negligible. In most typical cases, especially with thick spacing between the planes, the spreading inductance can be as significant as the surface trace inductance. By careful design of the stack-up, it is possible to routinely achieve less than 2-nH loop inductance.

Surprisingly, the board stack-up plays a significant role in the ESL of the capacitor—in two respects. By moving the top of the cavity closer to the capacitor, the loop inductance of the capacitor and the surface traces is reduced. By making the dielectric thickness of the cavity between the power and ground planes thinner, the spreading inductance is reduced. Adjusting these two design features can bring the ESL from 6 nH to 1 nH in some cases.

Both of these design features are first order and linear in the thickness. Changing via the diameter and moving the capacitor closer to the BGA are log-dependent factors and are of only slight (second- or third-order) importance.

If the surface trace length is also reduced and widened, ESL values as low as 0.5 nH can be achieved. An example of three similar cases is shown in Figure 13-37.

Figure 13-37 Three examples of thin cavity, close to the surface with three different surface traces, resulting in an ESL as low as 0.5 nH, analyzed with an online tool at www.beTheSignal.com.

This model can also be used to assess important design questions such as Is it better to add capacitors under the BGA or on the same surface as the BGA? Figure 13-38 illustrates the two options.

Figure 13-38 Where should the capacitor go: on the same surface as the BGA or directly under the BGA?

Of course, the most common answer to all signal integrity questions is “it depends,” and the only way to get a firm answer is by putting in the numbers.

The right place to put the capacitor is where it will have the lowest loop inductance. Clearly, if the total board thickness is thin, the via loop inductance will be low. If the cavity is far from the surface and thick, the loop inductance of the capacitor on the top will be high. It is possible to find a combination where the top surface capacitor has a much higher loop inductance than the bottom surface capacitor.

However, if the board is thick and the cavity is near the top surface and the cavity is thin, the capacitor on the bottom will have the higher loop inductance. Figure 13-39 summarizes three cases. It shows that placing the capacitor on the bottom can have a loop inductance on the order of 2 nH.

Figure 13-39 Analysis of capacitors on the top and on the bottom of the board. Analyzed with an online tool at www.beTheSignal.com.

If it is possible to achieve lower loop inductance by placing capacitors on the top surface, this is preferred, but as a general rule, if there is the option of doing both, both locations should be used, especially when many capacitors are used in low-impedance applications. When many capacitors are placed around the periphery of the package, their currents can overlap, and the cavity spreading inductance can increase. Placing some of the capacitors under the BGA minimizes the increase in cavity spreading inductance.

TIP

The combination of short, wide surface traces—or via-in-pad technologies—and thin dielectric between the power and ground planes close to the surface can result in typical ESL values from 0.5 to 2 nH. By going to extreme efforts and utilizing interdigitated capacitors, it is possible to achieve loop inductances below 0.5 nH.

If the capacitor mounting inductance is known, based on the design constraints, it will be possible to predict the impedance profile of a collection of capacitors using a 3D field solver. If the mounting inductance changes, as from a stack-up change or a surface-mounting design change, the loop inductance will change, and the impedance profile of the collection of capacitors will change. This is why every PDN design is custom.

TIP

The PDN impedance profile of the combination of capacitors depends very much on the details of the board stack-up, capacitor mounting geometry, and location on the board.

13.16 Combining Capacitors in Parallel

The strategy in engineering the PDN impedance profile is to select the right number and value of capacitors to keep the peak impedance below the target value from where the VRM and bulk capacitors no longer provide low impedance, up to about 100 MHz.

When multiple identical capacitors are connected in parallel, the resulting impedance matches the behavior of an RLC circuit, but the circuit elements values are different.

The equivalent R, L, and C of n capacitors in parallel are:

where:

Cn = equivalent capacitance of n identical real capacitors in parallel

C = capacitance of each individual capacitor

n = number of identical capacitors in parallel

ESRn = equivalent series resistance of n identical real capacitors in parallel

ESR = equivalent series resistance of each individual capacitor

ESLn = equivalent series inductance of n identical real capacitors in parallel

ESL = equivalent series inductance of each individual capacitor

Figure 13-40 shows an example of the impedance profile of multiple identical capacitors in parallel, showing the same general RLC profile but with lower impedance at all frequencies. We are approximating the problem by assuming that the capacitors are independent and their currents do not overlap. The SRF stays the same; it’s the entire impedance profile that scales lower. This is one way of decreasing the impedance profile of a capacitor: Add more of them in parallel.

Figure 13-40 Impedance profile of five identical capacitors added in parallel. With each additional capacitor, the impedance decreases at all frequencies.

However, if the two capacitors have a different value of capacitance or ESL, when they are added in parallel, the behavior is not so simple. Figure 13-41 shows the impedance profiles of two different capacitors with the same ESL and the same ESR. The behavior of the two capacitors in parallel has the same low-impedance dips at the self-resonant frequencies of the individual RLC models. The larger capacitor has the lower SRF. The smaller capacitor has the higher SRF. They each occur when the impedance of the ideal capacitor matches the impedance of the ideal inductance associated with each capacitor. The SRF seen in the parallel combination of capacitors is the same as each individual capacitor’s.

Figure 13-41 The impedance profile of two RLC circuits in parallel, with the same R and L values but different C values. Superimposed is the impedance of the two ideal capacitors and the ideal L and ideal R of both capacitors.

In addition, there is a new feature between the self-resonant frequencies: a peak in the impedance, called the parallel resonant peak, that occurs at the parallel resonant frequency (PRF).

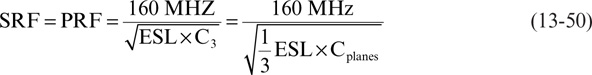

The value of the PRF is difficult to calculate accurately, as it depends on the ESL of the larger capacitor, the C of the smaller capacitor, and the ESR of both of them. If the SRF values are far apart, the PRF is roughly related to:

where:

PRF = parallel resonant frequency, in MHz

C2 = capacitance of the smaller capacitor, in nF

ESL1 = equivalent series inductance of the first capacitor, in nH

For example, if ESL1 = 2 nH and C2 = 10 nF, then the PRF is:

However, when the SRF values are within a factor of 10 of each other, the impedance profile of the parallel combination is distorted from the impedance of the ideal L.The PRF is a more complicated function of the elements, and can more easily be calculated using a SPICE simulation.

TIP

The PRF is one of the most important features of parallel combinations of capacitors because it denotes where there are peaks in the impedance. When few capacitors are used, it’s the parallel resonant impedance that always sets the limit to the PDN performance and must be engineered to lower values.

The peak impedance at the PRF is roughly related to:

where:

Zpeak = peak impedance at the PRF, in Ohms

L1 = equivalent series inductance of the larger capacitor

C2 = capacitance of the smaller capacitor

R1 = equivalent series resistance of the larger capacitor

R2 = equivalent series resistance of the smaller capacitor

This is only approximate and is less accurate as the SRFs of the capacitors are brought closer together. However, it points out the important ways of engineering a reduction in the peak impedance:

• Reduce the ESL of the larger capacitor.

• Increase the capacitance of the smaller capacitor.

• Increase the ESR of both capacitors.

TIP

Where there is the option to use higher-ESR capacitors—referred to as controlled resistance capacitors—they should be considered. A low enough ESR should be selected so that the equivalent ESR of all the capacitors in parallel is just below the target impedance.

The ESR of a capacitor is related to the structure of the parallel plates that make it up and the metallization between the layers. In general, the higher the capacitance, the more plates in parallel and the lower the ESR. Looking at the specifications of a variety of 0402 capacitors can provide a simple generalization for the series resistance of capacitors by capacitor value. Figure 13-42 shows the plotted ESR for various capacitor values, taken off the AVX data sheets.

From the specified ESR, it is possible to derive a simple empirical relationship between the ESR and the capacitance of a capacitor. One empirical approximation is given by:

where:

ESR = equivalent series resistance of the capacitor, in mOhms

C = capacitance of the capacitor, in nF

This simple model is compared with the specified values of ESR in Figure 13-42, and the agreement is seen to be very good.

This suggests that it may be possible to select for higher ESR and lower parallel resonant peak heights if smaller-value capacitors are used. This is especially true when one of the capacitors is the power and ground cavity’s capacitance.

Another important design feature to engineer to decrease the peak impedance value is decreasing the ESL of the larger capacitor or increasing the capacitance of the smaller capacitor. Figure 13-43 shows the impact on the peak impedance as the ESL of the larger capacitor is changed from 10 nH down to 0.1 nH.

Figure 13-43 Impedance profile of a 100-nF and a 10-nF capacitance with ESL of 3 nH in parallel while changing the ESL of the larger capacitor from 10 nH down to 0.1 nH. As the ESL is reduced, the peak impedance drops.

In this example, the larger capacitor is 100 nF, and the smaller one is 10 nF, with an ESL of 3 nH. As the ESL of the larger capacitor is reduced from 10 nH, the peak impedance at the PRF decreases until the SRF of the larger capacitor matches the SRF of the smaller capacitor, in which case there is no peak.

TIP

Reducing the ESL is a significant method of reducing peak impedances.

Unfortunately, due to the complex interactions of the circuit elements, it is not possible to do a simple and accurate analytical analysis of the features of the impedance profile of multiple capacitors. This is especially true as more capacitors are added. Instead, it is critical to use SPICE for such analysis. Luckily, there are many free versions of SPICE readily available on the Internet that can routinely perform this sort of analysis. For examples of these tools, visit beTheSignal.com.