Appendix D. Review Questions and Answers

This appendix contains review questions and answers to help you solidify your understanding of the material covered throughout the book. Try to answer all questions before looking at the answers that follow.

Chapter 1

1.1 Name one problem that is just a signal-integrity problem.

Reflections on a transmission line are just a signal-integrity problem. This is sometimes called “self-aggression” noise from the signal in the transmission line.

1.2 Name one problem that is just a power-integrity problem.

The rail noise on the core’s Vdd supply on the die is just a power-integrity problem. This is also an example of “self-aggression” noise on the Vdd rail, as it comes from the noise on the Vdd rail from the currents in the Vdd rail.

1.3 Name one problem that is just an electromagnetic compliance problem.

The source of ALL radiated emissions is from changing currents in extended conductors which are part of the system. Of course, the source of the currents is only from either signal and return currents or from power or ground currents, so there is always interaction between these three effects. However, many features of signals that do not affect the signals can have a dramatic impact on EMI. One good example is a slight mode conversion in a differential pair, such as a CAT 5 twisted pair. A small amount of common signal on the twisted pair will have no impact on the differential signal, but can cause a complete EMC failure.

1.4 Name one problem that is considered both an SI and PI problem.

The most commonly occurring problem that involves both signals and power integrity is ground bounce. This is the effect in which there is a skewed-up return path—i.e., not a wide uniform plane, and there are signals that share this common return path. When the return path is a narrow path like a lead in a package, it will have more inductance than a wide plane.

Since signal return paths are typically shared by power return paths, the skewed-up return paths could be part of the signal interconnects, or part of the power distribution network. When current flows through this shared, common return path, a voltage is generated. This is “ground bounce.” It is a form of cross talk between signals, or cross talk between power and signals.

1.5 What causes an impedance discontinuity?

An impedance discontinuity occurs when the instantaneous impedance the signal would see changes. This happens whenever the cross-sectional geometry changes. This could be when the signal conductor changes shape, when the return path geometry changes, or both. Discontinuities usually happen at interfaces of structures—from on-die, to packages, to traces on one layer, thru vias, and through connectors.

1.6 What happens to a propagating signal when the interconnect has frequency-dependent losses?

Generally, losses from conductors and dielectrics increase as you go up in frequency. When a signal with a fast edge passes through an interconnect with losses increasing with frequency, the higher frequency components will be attenuated more than the lower frequency components. This effectively decreases the bandwidth of the signal.

A high bandwidth signal will have a short rise time. As its bandwidth decreases, the rise time will increase. This rise time increase is the chief problem with lossy interconnects. When the rise time is comparable to the unit interval of the data pattern, the losses will affect signal quality.

1.7 What are the two mechanisms that cause cross talk?

The fundamental mechanism for cross talk is fringe electric and fringe magnetic field coupling. If all the electric and magnetic fields between the signal and return paths were confined to the vicinity of the signal paths, there would be no cross talk.

We can approximate the electric and magnetic field coupling as circuit elements with coupling capacitance and coupling inductance, which are called mutual capacitance and mutual inductance.

1.8 For lowest cross talk, what should the return path for adjacent signal paths look like?

A wide, solid plane always confines the stray electric and magnetic fields more than any other structure. For the lowest cross talk, always use a wide return plane. Any other structure increases the relative cross talk.

1.9 A low-impedance PDN reduces power-integrity problems. List three design features for a low-impedance PDN.

The power distribution network (PDN) are all the interconnects from the pads of the VRM to the pads of the power rail on the die. One way of reducing the impedance is by reducing the loop inductance in the path. This would be by 1) bringing the power path as close as possible to the ground path, 2) keeping interconnects short, and 3) using wide conductors like planes.

To reduce the interconnect lengths between the planes and the devices, 4) the power and ground planes should be on adjacent layers 5) with a thin dielectric, and 6) positioned as close as possible to the top component layer in the stack up.

1.10 List two design features that contribute to reduced EMI

One of the biggest sources of EMI is common currents on external, twisted pairs, like CAT 5 cables. This is reduced by using a shielded cable like CAT 6, with its shield connected to the chassis. It’s not that the “shield” in anyway shields the fields inside from radiating. It’s that the shield acts as a return path for the common currents on the twisted pair and reduces the external fields from the common currents.

A second problem arises from the connection of the shield. If it is not a 360-degree connection and does not look like an ideal coaxial connection, there will be some total inductance in the return path. When return current flows through this total inductance, it generates a ground bounce voltage and drives new common currents on the outside shield of the cable.

1.11 When is it a good idea to use a rule of thumb? When is it not a good idea to use a rule of thumb?

The starting place for tackling any problem should be applying a rule of thumb to estimate what to expect. This initial value will help drive your engineering judgment. When you are ready to sign off on a design, when the accuracy of the value to 10% or better is important, do not use a rule of thumb—use a numerical simulation with a verified process.

1.12 What is the most important feature of a signal that influences whether it might have a signal-integrity problem?

All signal-integrity problems increase with shorter rise time. Generally, when the rise time of a signal is 10 nsec or longer, the interconnects are pretty transparent and signal-integrity problems will be small. But, as the rise time decreases, signal-integrity problems will get worse. Generally, if the rise time is 1 nsec or less, interconnects are not transparent; and if you don’t worry about signal integrity, your product probably will not work the first time.

1.13 What is the most important piece of information you need to know to fix a problem?

The root cause. If you don’t know the correct root cause, your chance of fixing a problem is based on pure luck. Not only must you know the root cause, but you must have confidence you have the correct one. This is usually by thinking of as many consistency tests as you can, and trying them.

1.14 Best design practices are good habits to follow. Give three examples of a best design practice for circuit board interconnects.

1. Route all signals as uniform transmission lines.

2. Avoid using branches when routing signal lines.

3. Always use a continuous return path under each signal line.

4. Consider using a termination if the line is long enough or rise time short enough.

5. Always use as short a surface trace as possible for capacitors so their mounting looks as close to via in pad as practical.

6. Avoid messing up return paths or overlapping return currents of different signal paths

1.15 What is the difference between a model and a simulation?

A model is the electrical description of a physical structure, component, or device. It is the input information to the simulator, written in the language the simulator understands. For example, for a SPICE-like circuit simulator, the language of models is circuit elements such as capacitors, resistors, inductors, and transmission lines.

A simulator is an engine that computes electric or magnetic fields, S-parameters, voltages or currents in the time or frequency domain. Sometimes an S-parameter description of an interconnect can be used as a behavioral model of the interconnect and inserted in a simulation tool.

1.16 What are the three important types of analysis tools.

The simplest type of analysis tool is a rule of thumb. This is easy to use, but not intended to be very accurate. It’s designed to be the starting place of any analysis and helps establish solid engineering judgment.

The next, more accurate tool is an analytical approximation. While they can sometimes look complicated, this is not measure of their accuracy. They can be integrated into a spreadsheet and what-if scenarios evaluated. Their accuracy is not well established.

The potentially most accurate analysis tool is a numerical simulation. Although the value of this type of analysis can be very high, it also comes at a higher cost in expertise, learning curve, and actual dollar cost of the tool.

1.17 What is Bogatin’s rule #9?

Before you do a measurement or simulation, always anticipate what you expect to see. If you are wrong and you see something that is different than you expected, there is a reason for it. Do not use the result until you can understand why the result is not what you expect. Maybe you did something wrong, or the tool is wrong.

If you are correct, and you see what you expect, you get a nice warm feeling that maybe you do understand what you are doing. It is an important confidence builder.

The corollary to Rule #9 is that there are so many ways of screwing up a measurement or simulation, you cannot do enough consistency tests to help test the quality of your result.

1.18 What are three important reasons to integrate measurements somewhere in your design flow?

The input information to many simulators are material properties. These can often only be obtained from measurements.

The accuracy of models of components can only be validated by measurements.

Many simulation tools are intrinsically accurate. However, the process used to set up the problem and integrate it into the simulation tool may not be done correctly. The best way to validate a simulator tool and process to use it is by comparing the results to measurements on a well-characterized test vehicle.

1.19 A clock signal is 2 GHz. What is the period? What is a reasonable estimate for its rise time?

The period of a 2 GHz clock signal is 1/F = 0.5 nsec. If the rise time is about 10% of the period, the rise time would be 0.05 nsec, or 50 psec. This is just a rough estimate of what fraction of the period the rise time might be. It could be as long as 50% the period.

1.20 What is the difference between a SPICE and an IBIS model?

A SPICE model describes an active device as a combination of voltage and current sources and capacitors, inductors, and resistors. These are circuit element models which can often be related to specific physical features that make up the microscopic model of the device.

An IBIS model of a driver is often described as a behavioral model of the device. It consists of the behavior of the voltage-current curves of the driver under different load conditions. There is no connection between the behavior of the I-V curves and any physical design features.

1.21 What do Maxwell’s Equations describe?

They relate how electric and magnetic fields interact with currents, charges, and each other. Most importantly, Maxwell introduced two important new features in his equations. The first is the idea that a changing electric field acts just like a current, but is not the motion of physical charges. He termed it displacement current. This is a critically important concept in signal integrity.

The second important innovation he introduced in his equations was the coupling between a changing electric field generating a changing magnetic field, which then generates a changing electric field. It’s this mutual interaction that is the origin of propagating electromagnetic fields.

When you combine the linear differential equations between E fields and B fields, you get a linear, second order differential equation in just the E field and just the B field. The solution to these equations are propagating electric and magnetic fields—light.

1.22 If the underlying clock frequency is 2 GHz, and the data is clocked at a double data rate, what is the bit rate of the signal?

With two bits in every clock period, the bit rate would be 4 Gbps. The underlying clock frequency of a data rate, when there are two bits per cycle, is called the Nyquist frequency.

Chapter 2

2.1 What is the difference between the time domain and the frequency domain?

The time domain is the real world. The frequency domain is a mathematically constructed world.

In the real world, events happen sequentially with a time stamp and interval between events. An important property of the time domain in the real world is causality. This means, a response cannot happen before a stimulus.

In the time domain, we describe a signal as a voltage at discrete instants in time. A waveform is a voltage vs time display.

The frequency domain is a mathematical construct. In this precisely defined domain, the only type of waveforms that can exist are sine waves. The collection of all the various sine waves in a signal is a spectrum. A signal is then a voltage amplitude and phase at discrete frequency values.

2.2 What is the special feature of the frequency domain and why it is so important for signal analysis on interconnects?

In the frequency domain, the only type of waveform that can exist is a sine wave. Some physical effects have a natural response that matches the shape of sine waves.

This is the case when the physical effects are described by second order, linear differential equations. The solutions for these equations are sine waves. This means sine waves are naturally occurring in such systems.

Electrical circuits with resistors, capacitors, inductors, and transmission lines are described by linear, second order differential equations. This means that sine waves are naturally occurring in electrical circuits.

Many of the voltage vs time responses of electrical circuits will look like combinations of sine waves. Often, these waveforms can be described in a simpler way by just a handful of sine waves in the frequency domain than by voltage vs time in the time domain. When this is the case, you can often have a simpler solution in the frequency domain than in the time domain. This often translates to a shorter time to the answer by passing through the frequency domain than staying in the time domain.

2.3 What is the only reason you would ever leave the real world of the time domain to go into the frequency domain?

Since the real world is in the time domain, your first choice is always to stay in the time domain to solve problems. The only reason you would ever leave the real world to detour through the frequency domain, this mathematically constructed world, is to get to the answer faster.

Not all problems can be solved more quickly in the frequency domain. But when it works, the frequency domain can be an important shortcut. This is why you should become bilingual and learn to think and act in both the time domain and the frequency domain.

2.4 What feature is required in a signal for the even harmonics to be nearly zero?

In a time-domain waveform that is repetitive, each harmonic in the frequency domain will be a multiple of the repeat frequency. If the waveform is symmetric—that is, whatever happens in the first half of the period is exactly the same, with a negative sign in front of it—all even harmonics will have a zero amplitude. There will be no even harmonics in the frequency domain.

However, if there is any asymmetry between the first and second half of the period of the waveform, some even harmonics will appear. For example, if the signal is a square wave with a duty cycle of 50%, there will be no even harmonics. If the duty cycle is NOT 50%, there will be even harmonics.

If the waveform has some features that happen in the first half of the period of the waveform that doesn’t exist in the second half—like a rise time different than a fall time—there will be even harmonics.

2.5 What is bandwidth? Why is it only an approximate term?

The bandwidth of a signal is the highest sine-wave-frequency component that is significant in the spectrum of the signal. This means that you can eliminate all the frequency components of the signal above its bandwidth, and when you re-create the waveform, not have any important impact on the signal.

It is as though you send original signal through a low-pass filter with a steep high-frequency stop at the bandwidth. When you compare the original and filtered signal, they should be the same for all important features you care about.

But the terms “significant” and “care about” are vague terms. If you define the similarity of the original and low-pass filtered waveform as no difference to 10% in voltage vs time or no difference to 1% or no difference to 1%, you will get a different value for the bandwidth.

This makes the term bandwidth an approximate term. If you care about the 1% differences, you should not use the term bandwidth but include the whole signal waveform or the whole spectrum.

2.6 In order to perform a DFT, what is the most important property the signal has to have?

In order for a discrete Fourier transform to be most useful in describing a signal in the frequency domain, you should make sure the signal is repetitive and there are a whole number of cycles within the time window you use to calculate the DFT.

If this is the case, you will see harmonics as multiples of the repeat frequency of the signal and the spectrum will be independent of the number of cycles in the time interval.

If you choose a time interval that does not contain a whole number of cycles, the spectrum that results will depend specifically on the time interval you choose and will not be intrinsic to the signal.

2.7 Why is designing interconnects for high-speed digital applications more difficult than designing interconnects for rf applications?

Signals in high-speed digital applications have a wide bandwidth. This means interconnects must be well-behaved over a wide frequency range. Signals in the rf world have a narrow bandwidth, centered over the carrier frequency. This means interconnects must be well behaved at one frequency, the carrier frequency.

I think it is easier to design an interconnect for specific impedance properties at one frequency than over a wide range of frequencies.

Of course, “easier” is a subjective term. My friends working in the rf world would probably say their designs are harder to engineer than high-speed digital designs because they require much tighter control of impedance and can’t tolerate cross-talk levels that are as high as in digital designs.

2.8 What feature in a signal changes if its bandwidth is decreased?

The bandwidth is like the value of the frequency cliff in the low-pass filter. When selected as the bandwidth of the signal, it will be the lowest frequency at which the original signal and the filtered signal should look the same.

If you send a signal through a low-pass filter, the chief feature in the output signal that changes when you decrease the cliff frequency is the rise time of the signal. The lower the bandwidth, the longer the rise time.

2.9 If there is −10 dB attenuation in an interconnect, but it is flat with frequency, what will happen to the rise time of the signal as it propagates through the interconnect?

It the frequency response of the −10 dB attenuation is flat, this means every frequency component in the spectrum of the signal would see the same attention. The shape of the spectrum would stay the same; it would just be scaled down, everywhere, by −10 dB, which is a drop to about 30% of the original amplitude.

Since the rise time is related to the relative drop from the frequency components in the spectrum and the shape stays the same, the rise time would be the same. The signal amplitude would just be scaled.

Attenuation by itself does not cause rise-time degradation. It’s the frequency dependence of the attenuation that does.

2.10 When describing the bandwidth as the highest significant frequency component, what does the word significant mean?

The term “significant” is a vague term. It refers to the highest sine-wave-frequency component that needs to be included in any analysis. If you set all the frequency components above the bandwidth to zero and convert the signal back into the time domain, all the important properties of the signal you care about, like the rise time, will be preserved and close enough to the original signals.

Describing the bandwidth of a signal is the same as saying if you send the signal through a low-pass filter with a very steep, cliff wall drop-off, what is the lowest wall frequency you could use and still preserve the important features of the signal?

Different applications might have a different meaning of “significant.” If you want to re-create the rise time of a signal, and get the same 10−90 rise time of the signal after it passes through the cliff wall filter, you would need a cliff wall at about 0.35/rise time.

2.11 Some published rules of thumb suggest the bandwidth of a signal is actually 0.5/RT. Is it 0.35/RT or 0.5/RT?

If you are worrying about the difference between 0.35 or 0.5 in the relationship, don’t use the term bandwidth. You should consider the entire spectrum in your analysis. The term bandwidth, when referring to preserving a rise time, is too vague to distinguish 0.35 or 0.5.

If the rise time of the signal is 10% the period, T, of a square wave, for example, the harmonics will be at multiples of 1/T. This means the resolution of looking at the features of the spectrum will be at 1/T.

The bandwidth, defined by 0.35/RT, is the same as saying a frequency of 0.35/(0.1 × T) = 3.5/T. Saying the bandwidth is 0.5/RT is the same as a frequency of 5/T. The resolution of the spectrum is only 1/T and you are trying to distinguish a value of 3.5/T or 5/T. These two values are within 1.5/T of each other, close to the resolution limit of the spectrum.

2.12 What is meant by the bandwidth of a measurement?

The bandwidth of a measurement is the highest sine-wave-frequency component that you can measure in the system of the probes or fixtures and the device. To quantify this value, you usually define the frequency at which the amplitude of the detected signal is reduced by −3 dB of what is actually there.

In many digital storage scope (DSO) applications, the shape of the frequency response curve has a very sharp drop off at the high-frequency end, due to extensive signal processing. It is customary practice to define the bandwidth of the scope instrument alone as the −2 dB frequency point.

A 1 GHz scope has a −2 dB frequency point at 1 GHz. This would be based on sending sine waves into the scope and looking at the highest frequency that gets in with a signal amplitude down by only −2 dB.

A frequency-domain instrument, like a spectrum analyzer or a network analyzer, typically has a flat response, after calibration, up to the highest measurement frequency. Beyond this, the measured response, is, of course, zero. The bandwidth of the instrument is just the highest measured frequency component.

2.13 What is meant by the bandwidth of a model?

The bandwidth of a model is the highest sine-wave frequency at which the model’s predictions matches any measurement of the real components response to an “acceptable” level of accuracy.

Again, this term of “acceptable” is vague. Depending on the application, it generally means an agreement to within 10% between the measured response and the simulated response of the real component.

Generally, the agreement between the measured and simulated response drops off in accuracy much faster above the model’s bandwidth than below the bandwidth.

2.14 What is meant by the bandwidth of an interconnect?

The bandwidth of an interconnect is the highest frequency that can be transmitted through the interconnect and still meet the required signal performance specification.

Obviously, depending on the application, the requirement will change. If you want to preserve the rise time of the signal and not affect it by transmission through the interconnect, this generally means the frequency at which a signal would have an attenuation of −3 dB.

This assumes the attenuation is linearly frequency dependent. If the attenuation were flat at −3 dB, the rise time would not be degraded at all. If the frequency response were a cliff wall low-pass filter, the frequency at which the output 10−90 rise time were the same as the input rise time might be closer to the −2 dB point.

However, if the application required having just −20 dB of the carrier frequency amplitude at the output, compared to the signal at the input, you could tolerate a much poorer interconnect.

This is why you often add a qualifier to the term bandwidth of the interconnect and refer to the −3 dB bandwidth, or the −10 dB bandwidth, or the −20 dB bandwidth. This is based on what an acceptable attenuation might be for the application.

2.15 When measuring the bandwidth of an interconnect, why should the source impedance and the receiver impedance be matched to the characteristic impedance of the interconnect?

If you define the interconnect bandwidth as the highest frequency at which you have −3 dB of the input signal at the output, there are two reasons why the source and receiver impedance matter, compared to the characteristic impedance of the interconnect.

The amount of signal launched into the transmission line depends on the impedance of the source compared to the impedance of the interconnect. Increase the source impedance and less signal is launched into the transmission line. Likewise, change the receiver impedance and the output voltage at the receiver will vary. Increase the receiver impedance, and more voltage will be measured at the receiver.

If the source and receiver impedances are not matched to the characteristic impedance of the interconnect, then the reflections between the ends of the interconnect will cause ripples in the frequency response of the interconnect. These ripples are not intrinsic to the response of the interconnect. You can change their modulation depth by changing the external conditions of the source and receiver impedances.

You will minimize the effects of the terminations at the ends if you match the terminations to the characteristic impedance of the interconnect. This reveals the intrinsic performance of the interconnect.

Of course, if the interconnect is not a controlled impedance interconnect, and its instantaneous impedance varies down its length, there will be reflections inside the interconnect, which are part of the intrinsic properties of the interconnect. The best you can do is match the source and receiver impedances to the average, or low-frequency characteristic impedance of the interconnect.

This is where you sometimes must define the bandwidth of the interconnect at a specific terminated impedance. Luckily, if you know the interconnect response at one termination value, you can mathematically calculate the response at any other terminations. There is no need to measure every combination.

2.16 If a higher bandwidth scope will distort the signal less than a lower bandwidth scope, why shouldn’t you just buy a scope with a bandwidth 20 times the signal bandwidth?

There are two reasons why higher bandwidth isn’t necessarily better. First is cost. The higher the bandwidth of the scope, the more expensive it is. When purchasing an instrument, you always should consider the useful future use, or “headroom” of the instrument, and your budget.

Like hard drive memory space, you should always buy the highest bandwidth you can afford.

There is a fundamental problem with higher bandwidth measurements. Every receiver has some noise associated with it, even if it is just the digitizing noise of the ADC. Generally, the noise density is flat with frequency. This means that a higher bandwidth measurement lets in more amplifier noise than a lower bandwidth measurement. If there is no signal information at the higher bandwidth, all you are doing is increasing the noise.

The signal-to-noise ratio is literally the ratio of the signal energy to the noise energy. If a higher bandwidth measurement does not increase the signal energy, but only increases the noise energy, you get a lower SNR with a higher bandwidth scope.

This is why most scopes have a feature to allow the user to select the measurement bandwidth at the front of the amplifier. If you have plenty of SNR, it may not matter. But if you are pushing the limits to SNR, you want to use just enough measurement bandwidth to let in all the signal, but not so much as to let in more noise in a frequency range where there is no signal.

If you want to be a master of measurements, always pay attenuation to the bandwidth of your signal and match your measurement bandwidth to be at least twice the signal bandwidth so you don’t lose any signal—but not too much above this, so you don’t add too much noise.

2.17 In high-speed serial links, the −10 dB interconnect bandwidth is the frequency where the first harmonic has −10 dB attenuation. How much attenuation will the third harmonic have? How small an amplitude is this?

In an interconnect that is dominated by dielectric loss, the attenuation of the interconnect, in dB, drops off linearly with frequency. If there is −10 dB at a first-harmonic frequency of 1 GHz, for example, the attenuation at the third harmonic, 3 GHz, will be 3× this or −30 dB.

The amplitude of the first harmonic of the signal at the receiver will be down to 30% of the input signal with −10 dB of attenuation. At −30 dB attenuation, the amplitude will be down to:

This is not much signal left at the third harmonic.

2.18 What is the potential danger of using a model with a bandwidth lower than the signal bandwidth?

The whole purpose of a model is to represent the electrical behavior of the actual component. Its value is in how faithfully or accurately it predicts the actual performance of the real component.

The bandwidth of the model is the highest frequency at which the model’s prediction matches the real component behavior. If the signal has frequency components above the model’s bandwidth, the predictions of the model will no longer be accurate. Although you will get an answer, it will be wrong.

If the signal bandwidth exceeds the model’s bandwidth, the answer will be wrong, but it will be very difficult to quantify how wrong is the answer. This can often be misleading either as worse than reality, in which case you end up over-designing the product, or better than reality, in which case you end up with a product that may not work.

2.19 To measure an interconnect’s model bandwidth using a VNA, what should the bandwidth of the VNA instrument be?

At a minimum, the model’s bandwidth should be at least as high as the signal bandwidth, and the instrument’s bandwidth at least as high as the required model’s bandwidth.

If you can afford it, using a model and measurement bandwidth that are 2× the signal bandwidth adds a factor of two margin, which accounts for the vagueness of the term bandwidth. It’s a question of if you can afford it.

In a VNA, the bandwidth of the instrument is very well defined. It is the highest frequency the VNA goes up to. Generally, the cost of a VNA measurement goes up with higher measurement bandwidth. It’s the price of the VNA, and the cables, the connectors, the calibration system, the fixture design, and the care with which the measurements must be performed.

The bandwidth of the VNA to use should be at least as high as the required bandwidth of the model and extend up to the highest frequency you can afford. But going above 2× the model bandwidth does not add any additional value, unless the application requires knowing the limits. If there is no additional value above 2× the model bandwidth, higher frequency measurements than 2× the model’s required bandwidth should be used only if it is free.

2.20 The clock frequency is 2.5 GHz. What is the period? What would you estimate the 10−90 rise time to be?

The period is 1/clock frequency. If the clock frequency is 2.5 GHz, the period is 1/(2.5 GHz) = 0.4 nsec.

Of course, just because you know the period doesn’t mean you have any knowledge of the rise time. You have to make some assumptions. Generally, the rise time is about 10% the period in many clocked digital systems. Using this rule of thumb, if the period is 4 nsec, the rise time would be about 0.1 × 0.4 nsec = 0.04 nsec = 40 psec.

However, this assumption fails at extremes. In high-speed serial links, the rise time is often 1/2 the unit interval. The signal goes up and it goes down in one unit interval. If the unit interval is half the underlying clock frequency, called the Nyquist, the rise time is 0.25 × the clock period.

In simple microcontroller circuits, like the Arduino, the clock frequency is 16 MHz. The period is 60 nsec. You would expect the rise time to be about 6 nsec using the 1/10th rule of thumb. When measured, you find the rise time of signals coming off the I/O to be 3 nsec, half the expected rise time.

But sometimes, an ok answer now! is better than a good answer late. If all you know is the period and you need a rough estimate, not knowing anything else about the system or the signal, using the 1/10th rule of thumb is a good starting place.

2.21 A repetitive signal has a period of 500 MHz. What are the frequencies of the first three harmonics?

The first harmonic is the repeat frequency, 500 MHz. The second harmonic is 2× this, or 1 GHz, and the third harmonic is 3× this, or 1.5 GHz. Of course, you don’t have enough information to say anything about the magnitude of the first three harmonics, but these are the frequency values.

2.22 An ideal 50% duty cycle square wave has a peak-to-peak value of 1 V. What is the peak-to-peak value of the first harmonic? What stands out as startling about this result?

The amplitude of the first harmonic is 2/pi = 0.637 V. But, this is the amplitude of the sine wave represented by the first harmonic. The peak-to peak-value of this sine wave is 2× this, or 1.25 V.

What is startling is that the peak-to-peak value of the square wave is 1 V. Yet, the peak to peak of the first harmonic, contained in this signal, is 1.25 V. Its 25% larger than the original signal’s waveform.

It’s in combination with the other harmonics that this peak-to peak-value is brought down to the value closer to 1, as more harmonics are added.

2.23 In the spectrum of an ideal square wave, the amplitude of the first harmonic is 0.63 times the peak-to-peak value of the square wave. What harmonic has an amplitude 3 dB lower than the first harmonic?

The amplitude of each frequency component in the ideal square wave’s spectrum decreases as 1/n. This means the second harmonic amplitude is down to 50% of the first harmonic, and the third harmonic amplitude is down to 1/3 or 33% of the first harmonic amplitude.

An amplitude that is reduced by −3 dB is an amplitude that is down to 71% of the original amplitude. This is somewhere between the first harmonic and the second harmonic. The second harmonic is already down much lower than −3 dB. In fact, it is down by −6 dB from the first harmonic amplitude.

This is important because saying the bandwidth is when the harmonic amplitude is down by −3 dB of the first harmonic amplitude is just blatantly wrong.

2.24 What is the rise time of an ideal square wave? What is the amplitude of the 1001st harmonic compared to the first harmonic? If it is so small, do you really need to include it?

The definition of an ideal square wave is that the rise time is 0 psec. The bandwidth of an ideal square wave is infinite. When you calculate the amplitude of any harmonic of an ideal square wave analytically, you derive the equation:

When the square wave is symmetrical and it has a 50% duty cycle, the even harmonic amplitudes are zero, so this relationship applies to odd values of n only.

You can use this to calculate the amplitude of any harmonic, even the n = 1001 value, as

This is a tiny value compared to the first harmonic. In fact, it is less than 0.1% of the first harmonic amplitude. Surely it is small enough you can ignore it. If you drop off the higher harmonics at n = 1001 and above, even though these are tiny amplitudes, you will end up with a square wave that does not have a 0 psec rise time. It would have a longer rise time.

If you care about a 0 psec rise time, every harmonic, however small, must be included in the spectrum. They are all significant.

2.25 The 10−90 rise time of a signal is 1 nsec. What is its bandwidth? If the 20−80 rise time was 1 nsec, would this increase, decrease, or have no effect on the signal’s bandwidth?

The bandwidth of a 1 nsec rise-time signal is 0.35/1 nsec = 350 MHz. If instead of the 10−90 rise time, you use its 20−80 rise time, the bandwidth of the signal would not change. It is intrinsic to the signal.

However, if the 20−80 rise time were 1 nsec, the 10−90 rise time would be longer than 1 nsec. A longer rise time means a lower bandwidth. You should be careful which rise time you use when you estimate the bandwidth of the signal.

2.26 A signal has a clock frequency of 3 GHz. Without knowing the rise time of the signal, what would be your estimate of its bandwidth? What is the underlying assumption in your estimate?

Of course, it’s the rise time of the signal that determines its bandwidth, not its clock frequency. However, if you don’t know anything else about the signal other than its clock frequency, the bandwidth is about 5 × the clock frequency.

For a clock frequency of 3 GHz, the bandwidth is roughly 5 × 3 GHz = 15 GHz.

In making this connection, you are assuming that the rise time of the signal is about 7% the period. This means if the rise time were actually longer than 7% the period, the bandwidth would be less than 15 GHz. This is a conservative estimate of the bandwidth and generally gives a little higher bandwidth than if the rise time were 10% the period, for example.

2.27 A signal rise time is 100 psec. What is the minimum bandwidth scope you should use to measure it?

The bandwidth of the scope should be at least twice the bandwidth of the signal. If the rise time is 0.1 nsec, the bandwidth is 0.35/0.1 nsec = 3.5 GHz. The scope bandwidth, including its probes, should be at least 2× this, or 7 GHz.

If the scope bandwidth is less than 7 GHz, the rise time measured by the scope will be longer than the actual rise time of the signal.

2.28 An interconnect’s bandwidth is 5 GHz. What is the shortest rise time you would ever expect to see coming out of this interconnect?

An interconnect bandwidth of 5 GHz means that if you send in a signal with a rise time of 1 psec, the rise time coming out will have a bandwidth of 5 GHz. This means a rise time of 0.35/5 GHz = 70 psec.

The shortest rise time signal you could see coming out of the interconnect would be about 70 psec.

2.29 A clock signal is 2.5 GHz. What is the lowest bandwidth scope you need to use to measure it? What is the lowest bandwidth interconnect you could use to transmit it and what is the lowest bandwidth model you should use for the interconnects to simulate it?

If you don’t know the rise time of the signal, you cannot get an accurate measure of the bandwidth of the signal, or the bandwidth of the other features needed. All you can do is roughly estimate. When it costs extra for more performance than you need, or you want to avoid the risk of not providing adequate bandwidth, getting the information you need is really important.

If all you know is that the clock frequency is 2.5 GHz, then you can estimate the bandwidth as 5 × 2.5 GHz = 12.5 GHz. Using this as the starting place, you want to have a scope with a bandwidth of at least 2 × 12.5 GHz, or 25 GHz. This is a bandwidth of the instrument which is 10× the clock frequency.

Generally, at clock frequencies of 2.5 GHz, the rise time is longer than 7% the period, but in this case, you are paying extra for insurance and your lack of more accurate knowledge.

To not degrade the signal rise time to any noticeable extent, you should also use an interconnect with a transmission bandwidth of 2× the signal bandwidth of 25 GHz. Likewise, the model bandwidth should be 25 GHz.

While these are the goals, without knowing the rise time, you may be spending more than you should by using a conservative value of the signal bandwidth. This is why it may be worth it to invest some time and effort into determining the actual signal bandwidth before committing to 25 GHz scopes, interconnects, and models.

Chapter 3

3.1 What is the most important electrical property of an interconnect?

While there are many electrical properties that characterize an interconnect, the most important one is its impedance. This can come in a number of forms. One in particular is the input impedance as a function of frequency.

3.2 How would you describe the origin of reflection noise in terms of impedance?

When a signal is propagating down an interconnect and encounters a change in the instantaneous impedance, a reflection is generated, and the transmitted signal is distorted. It is the impedance environment the signal sees down the interconnect that determines the signal distortion from reflection noise.

3.3 How would you describe the origin of cross talk in terms of impedance?

Cross talk from an aggressor line to a victim line is ultimately due to fringe electric and fringe magnetic fields. You can approximate these fields in terms of small, lumped circuit elements using capacitor and mutual-inductor elements.

The cross talk between two adjacent signal and return paths is due to coupling capacitance or mutual capacitance, and coupling inductance, or mutual inductance. The amount of coupled signal depends on the source voltage and the impedance of these coupled elements.

3.4 What is the difference between modeling and simulation?

Modeling is the process by which you convert a physical interconnect composed of conductors and dielectrics into an equivalent electrical circuit model. You first must construct the circuit topology that describes the structure. Each circuit element in the circuit topology has a few parameters that define the element.

The second step is to calculate a value of the parameters in each circuit element. This can be done by using a rule of thumb, an analytical approximation, or a numerical simulation tool.

Simulation is using the model to predict actual signal waveforms either in the time or frequency domain as currents or voltages.

A simulator takes the circuit model and solves the differential equations each element is a shorthand for, and predict the output waveforms based on an input signal.

3.5 What is impedance?

Impedance is fundamentally the ratio of the voltage across a component to the current through it. This ratio defines the connection between how the current and voltage interact with the component. Impedance usually is frequency dependent, so it is more easily described in the frequency domain, though it is also defined in the time domain.

There are at least five different types of impedance, each with a different qualifier to distinguish them. There is instantaneous impedance, characteristic impedance, input impedance in the time domain, input impedance in the frequency domain, and the impedance matrix for components with more than two terminals.

3.6 What is the difference between a real capacitor and an ideal capacitor?

A real capacitor is the actual physical device you call a capacitor. These physical components are mounted to a circuit board and used in filter applications to block DC voltage, or to provide local charge storage, for example.

An ideal capacitor is the electrical model of the real capacitor. It is an idealized description written in the language the intended simulation understands. Being ideal does not mean it does not describe some of the more complicated behavior of the real capacitor.

The model can have multiple levels of sophistication to take into account both the low frequency and the high frequency properties of the real capacitors.

An important metric of an ideal capacitor is the bandwidth of the model—that is, how high a frequency the predictions of the model, such as its impedance, match the measured properties of the real capacitor.

3.7 What is meant by the bandwidth of an ideal circuit model used to describe a real component?

The bandwidth of an ideal circuit model is the highest frequency at which you would expect good agreement between the predictions of the model’s behavior to still match the measured properties of the real capacitor’s.

This is a measure of how high a frequency you can use this ideal model to approximate the real capacitors. For example, at low frequency, the ideal capacitor can be model as a single ideal C element. As you go up in frequency, a better model is a series RLC circuit. This model can be further refined to account for the frequency dependence of the real part of the impedance.

3.8 What are the four ideal passive circuit elements used to build interconnect models?

The four most commonly used circuit elements to describe interconnects are the resistors, R; the capacitor, C; the inductor, L; and the uniform transmission lines, with a Z0 and a TD.

3.9 What are two differences between the behavior you might expect between an ideal inductance described by a simple L element and a real inductor?

At low frequency, the real inductance should behave pretty much like an ideal inductance. You would be surprised if there was much difference in the measured and modeled properties, if you pick the right value of L.

However, the real inductor would show a real part to the impedance, due to the frequency-dependent series resistance. In addition, at very high frequencies, above about 100 MHz, the impedance of a real inductance begins to flatten out and may even decrease with higher frequency, due to the presence of stray capacitance between the terminal of the inductor.

If you know the actual performance of the real inductance, it’s possible to construct a circuit model for the ideal capacitor out of building block elements, which can closely match the actual behavior of the real inductor.

3.10 Give two examples of an interconnect structure that could be modeled as an ideal inductor.

An engineering change wire added to a board that splices a new route between two pins can often be modeled as a simple inductor. A wire bond inside of an IC package connecting the die pads to the package leads can often be modeled as an ideal inductor.

3.11 What is displacement current, and where do you find it?

Displacement current is the invention of Maxwell. When he looked at the properties of magnetic fields and conduction current, he found that if he treated a dE/dt as a current, he was able to preserve continuity of current through an insulation dielectric.

This was one of the important unifying principles he introduced when he collected his four equations together. He realized there are really two types of current: conduction current and displacement current. The displacement current flows along changing electric field lines and is proportional to how fast the E field lines are changing.

This is how current gets through the insulating dielectric of a capacitor. It flows as the changing E field inside the capacitor when the voltage across the plates changes.

Displacement current will flow between two conductors whenever the voltage across them changes, which means the electric field between them changes. This is how return current flows between the signal and return path as a signal travels down a transmission line.

3.12 What happens to the capacitance of an ideal capacitor as frequency increases?

In the model of an ideal capacitor, the capacitance is absolutely constant with frequency. The capacitance in the C element is constant with frequency. Of course, the impedance of an ideal capacitor ill change, but the value of the capacitance will be constant.

This is slightly modified in many high-end circuit stimulators. Since the real capacitor is typically filled with a dielectric constant that changes with frequency, the capacitance will slightly change with frequency. Some more complex ideal capacitor models include this slight frequency dependence effect.

3.13 If you attach an open to the output of an impedance analyzer in SPICE, what impedance will you simulate?

Many SPICE simulators require that there be a DC path to ground to calculate initial conditions. If there is an open to ground, SPICE will output an error message.

After all, this is the case of an immoveable object encountering an irresistible force. The constant current source will output whatever voltage it needs to in order to keep the current from the source constant. If the impedance is open, this would require an infinite voltage to generate the constant current across the open. Hence, an error message.

This is why it is a good plan to add a shunt resistance across the ends of the constant current source in SPICE. This will always provide a finite, but high resistance to ground, and the constant current can be achieved with a very high, but finite voltage.

3.14 What is the simplest starting model for an interconnect?

The simplest starting model for an interconnect used to be an RLC circuit. All simulators understand R, L, and C elements. But as simulators have become more sophisticated, all simulators now incorporate transmission line elements. This is a far better starting model for an interconnect.

The transmission line model of an interconnect can match the properties of the real interconnect at low frequency, and at much higher frequency. It’s the simplest model that can achieve reasonably good bandwidth.

3.15 What is the simplest circuit topology to model a real capacitor? How could this model be improved at higher frequency?

The simplest circuit topology of a real capacitor is an ideal C element. By choosing the correct parameter for the C value, this model can match the measured impedance of a real capacitor up to the 1 MHz bandwidth and above in some cases.

If you want to get a higher bandwidth model, a second order model would be an RLC circuit topology. The C would be the same as the first order model value, while the L value is about the mounting of the capacitor to the circuit board.

3.16 What is the simplest circuit topology to model a real resistor? How could this model be improved at higher frequency?

The simplest model of a real resistor is just a single R element. This model is usually a good match to a real R into the 10 MHz range. The impedance of a real resistance is very flat with frequency.

For a higher bandwidth model, a series ideal R and L element can be used. This model takes into account the mounting inductance of the resistor. This ideal model can often match the measured impedance of a real resistor into the GHz regime.

3.17 Up to what bandwidth might a real axial lead resistor match the behavior of a simple ideal resistor element?

The presence of the leads in an axial lead resistor generally adds as much as 10 nH of series inductance. You can calculate the difference between the ideal model of a single R element and the increase in impedance from the series L. The higher frequency you go, the bigger the impedance of the series inductance and the larger the impedance of the real resistor.

As a rough metric of good enough, you can take when the impedance of the inductor is more than 10% the impedance of the series resistance. This is the frequency where neglecting the series inductance in the ideal model gives a result that is as much as 10% off from the real resistor.

This condition is when

Or

This is the case for a 50 Ohm resistor and 10 nH of mounting inductance. Below 80 MHz, the simple ideal R element will have an impedance that matches the real resistor within 10%, providing you select the correct resistance value.

3.18 In which domain is it easiest to evaluate the bandwidth of a model?

The term bandwidth is inherently a frequency-domain term; this means it is more easily evaluated in the frequency domain. When evaluating the bandwidth of a model, for example, it is easy to compare the predicted impedance over frequency and the measured impedance over frequency. The frequency above which they do not agree very well is the bandwidth of the model.

3.19 What is the impedance of an ideal resistor with a resistance of 253 Ohms at 1 kHz and at 1 MHz?

This is easy. The impedance of an ideal resistor is constant with frequency. It is exactly equal to its resistance. The resistance of an ideal 253 Ohm resistor is the same 253 Ohms at 1 kHz and at 1 MHz.

3.20 What is the impedance of an ideal 100 nF capacitor at 1 MHz and at 1 GHz? Why is it unlikely a real capacitor will have such a low impedance at 1 GHz?

The magnitude of the impedance of an ideal capacitor is

For the case of a 100 nF capacitor, at 1 MHz and 1 GHz, the impedance is

Wow! It looks like using even just a 100 nF capacitor results in an impedance as low as 1 mOhm at 1 GHz. This looks really low!

Unfortunately, in a real capacitor, there is lead inductance that plays a role. The impedance of the series inductance starts to dominate the real capacitor’s impedance above about 10 MHz. Above 10 MHz, the impedance of the real capacitor will go up, hiding the low impedance of the ideal capacitance of the real capacitor.

3.21 The voltage on a power rail on-die may drop by 50 mV very quickly. What will be the dI/dt driven through a 1 nH package lead?

The relationship between the voltage drop across an inductor and the transient current is

For the case of a 50 mV drop and 1 nH package lead, the transient current that will be driven through the package is

3.22 To get the largest dI/dt through the package lead, do you want a large lead inductance or a small lead inductance?

It’s clear from the previous example that the highest transient current which comes into the on-die capacitance to re-supply the lost charge, occurs when the lead inductance is smallest. This is why you want low inductance in the package lead inductance. It encourages fast current transients into the on-die capacitance, which means less voltage droop on die.

3.23 In a series RLC circuit with R = 0.12 Ohms, C = 10 nF, and L = 2 nH, what is the minimum impedance?

The minimum impedance will always be equal to the R in the circuit. This occurs when the reactance goes to zero. In this example, the minimum impedance is 0.12 Ohms.

3.24 In the circuit in Question 3.23, what is the impedance at 1 Hz? At 1 GHz?

You can calculate the impedance of this series RLC circuit in a few ways. First, you can bring it into a SPICE-like simulator and simulate the impedance at any frequency. Second, you can write an analytical equation for the magnitude of the impedance at any frequency. Using a calculator, you can easily calculate the impedance at any frequency.

Finally, you can roughly estimate the impedance based on which part of the circuit is dominating the impedance. For example, at low frequency, easily in the 1 Hz range, the circuit impedance will be dominated by the capacitor. The impedance will be

At 1 GHz, the impedance will be dominated by the inductor. Its impedance will be

3.25 If an ideal transmission line matches the behavior of a real interconnect really well, what is the impedance of an ideal transmission line at low frequency? High or low?

If the far end of the transmission line is open at the receiver, and you are looking at the front of the transmission line, it will look like a very high impedance at low frequency. As you go to higher frequency, the impedance will drop, until it looks like a short. Even though the transmission line is open at the end, when you look at the front of the line, the transmission line will look like a short.

As you further increase frequency, the transmission line will look like an inductor, increasing its impedance until it looks like an open; then it will drop again and continue this oscillating behavior between an open and a short. A transmission line open at the far end is not a very well-behaved interconnect for high-frequency signals.

3.26 What is the SPICE circuit for an impedance analyzer?

Creating an impedance analyzer in SPICE is easy. All you need is a constant current AC source. This will generate a sine wave of constant current amplitude using whatever voltage amplitude it needs to generate a constant current amplitude.

As long as you make the constant current amplitude a fixed value of 1 A, the simulated voltage on the impedance analyzer is numerically the same as the impedance of whatever is attached to the analyzer. It’s important to note that this is a complex relationship. The phase of the voltage is also the phase of the impedance.

Chapter 4

4.1 What three terms influence the resistance of an interconnect?

The three most important terms influencing the resistance of an interconnect are the bulk resistivity of the conductor material, the length of the interconnect, and the cross-sectional area through which the current will flow.

4.2 While almost every resistance problem can be calculated using a 3D field solver, what is the downside of using a 3D field solver as the first step to approaching all problems?

To use a 3D field solver requires that you have the solver and know how to use it. Most of these tools will output a number. But, there are multiple ways the number can be a meaningless result. Without knowing what to expect, you have no idea if the result out of the field solver is “reasonable.”

If you rely on all of your results from a 3D field solve, you miss the valuable opportunity to get a feel for the number using approximations or rules of thumb. It is much faster to estimate the resistance using a rule of thumb that you can do 50 different estimates in the time it takes to load one problem in the field solver and get a result.

That’s where a simple approximation or a rule of thumb is so valuable. A rule of thumb should always be the first step in estimating the resistance of an interconnect.

4.3 What is Bogatin’s rule #9, and why should this always be followed?

Rule #9 is to never do a measurement or simulation without first anticipating the result. This means you should have an idea of what the answer should be before you start the problem. This is where a rule of thumb that allows a quick, approximate estimate of the answer is so valuable. It calibrates your engineering judgement and gives you a feel for the numbers.

There are so many ways of screwing up a problem, you cannot do too many consistency tests. The first consistency test is checking if your result is consistent with your engineering judgement, which often is based on rules of thumb.

4.4 What are the units for bulk resistivity, and why do they have such strange units?

The units for bulk resistivity are Ohms-cm. What the heck does this mean? It’s not a resistance per volume, it’s not a resistance per area, and it’s not even a resistance per length.

When you calculate the resistance of a uniform length structure, the resistance is in the form of

The resistance will scale linearly with the length of the interconnect and inversely with the cross-sectional area. The proportionality constant is the bulk resistivity of the material. It is a measure of the resistance property of the material.

The units of bulk resistivity are to make the units of resistance come out as Ohms. The Length/Area has units of 1/length. The bulk resistivity has to have units of length in its numerator.

If you had a cube of material, with the length of each side as Len, the Length/Area would be 1/Len. This says the larger the length of a side of the cube, the lower the resistance. While the distance between end faces increases as the side of the edge increases, which would increase the resistance, the cross-sectional area increases with the square of the side of an edge which would drop the resistance faster than the length increases it.

The resistance would be R = rho / Len. The units of rho has to be Ohms-length in order for the resistance to end up in Ohms.

4.5 What is the difference between resistivity and conductivity?

These are both terms that describe the electrical resistance of a piece of the material. The resistivity is a measure of how resistive the material is. The conductivity is a measure of how conductive the material is. They both measure the same material property. One is the inverse of the other:

Since the units of resistivity are Ohms-m, the units for conductivity are 1//(Ohms-m). You call the units of 1/Ohms Siemens. The units of conductivity are Siemens/m. Again, these units don’t make much sense except to get the units to come out to Ohms when calculating the resistance of an extended object.

4.6 What is the difference between bulk resistivity and sheet resistivity?

The bulk resistivity is the intrinsic material property that relates to how much resistance there would be in the material. It doesn’t matter the size or shape of the material or how much you have. All pieces of the same material have the same bulk resistivity.

Sheet resistance refers to the resistance property of a section of the material shaped in a wide, thin, uniform thickness sheet, like a foil of copper.

The sheet resistivity, or the sheet resistance, used interchangeably, refers to the resistance from edge to edge of a square piece of the material cut out from the sheet. If you were to double the length of a side of the square, the distance between the faces you measure resistance increases so the resistance would increase, but the width through which the current travels would also increase, decreasing the resistance. These two features cancel out and the resistance from edge-to-edge stays the same.

This says no matter what the length of the edge of the square, the resistance from edge to edge is the same. You call this resistance of one square, the sheet resistance or the sheet resistivity, or the resistance per square. Every square cut from the same sheet has the same resistance.

4.7 If the length of an interconnect increases, what happens to the bulk resistivity of the conductor? What happens to the sheet resistance of the conductor?

This is a trick question. The bulk resistivity of a material is an intrinsic property of the material, not the geometry. If the length of the interconnect increases, the bulk resistivity of the material stays the same. It is about the material.

Likewise, if the interconnect is composed of a sheet of conductor like a trace on a layer of a circuit board, the sheet resistance is intrinsic to the material that makes up the foil and the foil thickness. If the length of the interconnect changes, the sheet resistance of the foil does not change.

4.8 What metal has the lowest resistivity?

Of all the homogenous materials, other than a superconductor, silver has the lowest bulk resistivity, with a value of about 1.59 × 10−8 Ohm-m. Copper comes in a close second with a resistivity of 1.68 × 10−8 Ohm-m. Note that copper is only 6% more resistive than silver. This is only a small difference. Many times, this slight benefit is not worth the extra cost of using silver with its higher bulk cost and higher manufacturing cost.

It’s often thought that gold is the lowest resistivity material. This is far from the case. In fact, the resistivity of gold is 2.44 × 10−8 Ohm-m. This is 45% higher than copper, which is quite a difference. Why is gold used so often as an interconnect material?

It’s not often the bulk material, it is often just a coating. This is because gold does not corrode or oxidize. It is a good material to have on the surface to enable good soldering and low contact resistance.

4.9 How does the bulk resistivity of a conductor vary with frequency?

Generally, the bulk resistivity of a material is very constant with frequency. This is the case until well above 100 GHz. The resistance of an interconnect will be frequency dependent, but this is not due to the resistivity changing—it is due to the cross-sectional area through which current is traveling changing.

For all applications, assume the bulk resistivity of copper and all other conductors is constant with frequency.

4.10 Generally, will the resistance of an interconnect trace increase or decrease with frequency? What causes this?

The resistance of an interconnect trace will always increase with frequency. This is due to the effect called skin depth. As the frequency of the current increases, the path through the conductor changes in order for the current path taken to reduce the loop inductance of going down through the conductor and back on the return conductor.

Within each conductor, a lower inductance is achieved when the current flows toward the outer surface of the conductor. The higher the frequency, the more the current concentrates to the outer surface. When the cross-sectional area through which the current travels gets thinner, the resistance increases, usually proportional to the square root of frequency.

4.11 If gold has a higher resistivity than copper, why is it used in so many interconnect applications?

Gold’s chief property is that it does not oxidize or corrode. This means that if it is on the outer surface of a conductor, there will be low contact resistance when another gold surface comes in contact. And, since it does not oxidize when solder wets gold, it is a good surface to solder on even after a long time exposed to the air.

Usually the gold on an interconnect is very thin. The typical spec for a connector lead is 30 micro-inches, which is a little less than 1 micron of gold. It’s only enough to protect the underlying metal from oxidation and corrosion.

4.12 What is the sheet resistance of ½-ounce copper?

This is one of those numbers useful to remember. The sheet resistance of ½ ounce copper foil is 1 milli-Ohm per square. You can see where this comes from based on the calculation of sheet resistance. It is given by

1 mOhm/sq is an easy number to remember.

4.13 A 5-mil wide trace in ½-ounce copper is 10 inches long. What is its total DC resistance?

The sheet resistance of ½-oz. copper foil is 1 mOhm per square. To calculate the resistance of the trace, you need to know how many squares are along its length, as each square is 1 mOhm of resistance.

The number of squares is 10 inches/0.005 inches = 2,000 squares. The series resistance is 2,000 squares × 1 mOhm/square or 2 Ohm. This narrow trace, spanning 10 inches, has a resistance of 2 Ohms. This many not be much in a digital circuit, but if it is in a power path, it can be a lot.

4.14 Why does every square cut out of the same sheet of conductor have the same edge to edge resistance?

If you have a piece of sheet cut in the same of a square and measure the edge to opposite edge resistance, you would see that if the distance between the edges doubled, the resistance would double. But if you doubled the width, the resistance would be cut in half.

If you do both, double the length and double the width, you still have a square and the resistance stays the same.

You can see this when looking at the resistance based on the geometry

If in your interconnect, you keep the ratio of the length of the interconnect and the width of the interconnect the same, the resistance does not change. And if the ratio is 1, so you have a square shape, the resistance from edge to edge of the square is a constant that just depends on the bulk resistivity and the foil thickness, which you call the sheet resistance.

4.15 When you calculate the edge-to-edge resistance of a square of metal, what is the fundamental assumption you are making about the current distribution in the square?

When you calculate the edge to edge resistance, you are assuming that the current flows uniformly down the length of the square. You launch the current into the edge and take it out of the other end so that there is the same current density everywhere in the square of conductor. If you make contact with a point on the edge, the resistance you measure would be higher.

4.16 What is the resistance per length of a signal line 5 mils wide in ½-ounce copper?

In half-ounce copper, the sheet resistance is 1 mOhm/sq. A line that is 5 mils wide would have a resistance per length of 1 mOhm/sq/(0.005 inch) = 0.2 Ohms per inch.

4.17 Surface traces are often plated up to 2-ounce copper thickness. What is the resistance per length of a 5-mil wide trace on the surface compared to on a stripline layer where it is ½-ounce thick?

When the thickness of the conductor increases, there is more cross-sectional area for the current to travel and the sheet resistance and the resistance per length of the conductor decreases.

In going from ½ oz. copper in a stripline layer to 2 oz. copper on the surface, the thickness has increased by 4×. This means the resistance has decreased by ¼. The resistance per length of a 5-mil wide trace in ½ oz. copper is 0.2 Ohms/inch. This same trace fabricated on the surface has a resistance of ¼ this, or 0.05 Ohms/inch.

4.18 To measure the sheet resistance of ½-ounce copper using a 4-point probe to 1%, you are resolving a resistance of 1 µOhm. If you use a current of 100 mA, what is the voltage you have to resolve to see such a small resistance?

In order to measure a resistance of 1 µOhm, with a forcing current 0.1 A, the voltage that you would have to measure is V = I × R = 0.1 A × 1 µOhm = 0.1 µV = 100 nV. This is a very tiny voltage.

This means that for routine sheet resistance measurements, an instrument would need to be able to routinely measure 100 nV signal. It is no wonder that these measurements are rather difficult.

4.19 Which has higher resistance: a copper wire 10 mil in diameter and 100 inches long, or a copper wire 20 mils in diameter but only 50 inches long? What if the second wire were made of tungsten?

You could answer this question by calculating the resistance of each wire and looking to see which is larger. Alternatively, you can use scaling to estimate the different resistance.

The first copper wire is 10 mil in diameter and 100 inches long. The second wire is 20 mils in diameter and 50 inches long. This one is obvious. The smaller cross-section wire will have a higher resistance per length. And, it’s longer. Clearly the first wire will have higher resistance.

Suppose you made the second wire out of tungsten. Which wire would be higher resistance?

Now you can apply scaling. The resistance of the wire is basically

The length of the second wire is ½ that of the first wire. The cross-sectional area is 4× that of the first wire. These two factors alone would make the resistance of the second wire ½ /4 = 1/8th that of the first wire. The resistivity of copper is 1.68 × 10−8 Ohm-m. The resistivity of tungsten is 5.6 × 10−8 Ohm-m. This is a factor of 3.3 × higher for the second wire.

This makes the second tungsten wire, a factor of 3.3/8 = 0.42, as large as the first wire. Even with the higher resistivity, the shorter length and larger diameter overcompensates for the higher resistivity.

4.20 What is a good rule of thumb for the resistance per length of a wirebond?

A wire bond, usually made from 1-mil diameter aluminum or gold wire, has a resistance of about 1 Ohm/inch. If the wire bond is 0.1 inches long, its resistance will be 0.1 Ohms.

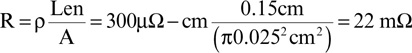

4.21 Estimate the resistance of a solder ball used in a chip attach application in the shape of a cylinder, 0.15 mm in diameter and 0.15 mm long with a bulk resistivity of 15 µOhm-cm. How does this compare to a wire bond?

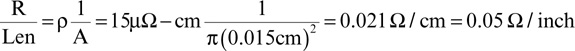

The resistance of a uniform cross-section interconnect is

The resistance per length, for this case of a 0.15-mm diameter cylinder, is then just

The resistance per length of a wire bond is about 20 × the resistance per length of a solder ball. This is mostly due to the larger diameter of the solder ball. If the ball is 0.15 mm long, the resistance of the solder ball will be 0.021 Ohm/cm × 0.015 cm = 0.0003 Ohms. This resistance is pretty insignificant compared to other sources of resistance in the path.

4.22 The bulk resistivity of copper is 1.6 µOhms-cm. What is the resistance between opposite faces of a cube of copper 1 cm on a side? What if it is 10 cm on a side?

The resistance from one face of a cube, 1 cm on a side, to the other, is

If the side of a cube is 10 cm, larger by 10×, the resistance will be lower by 10×, to 0.16 µOhm.

4.23 Generally, a resistance less than 1 Ohms is not significant in the signal path. If the line width of ½-ounce copper is 5 mils, how long could a trace be before its DC resistance is > 1 Ohms?

When the line width for ½ oz. copper is 5 mils, the resistance per length is 1 mOhm/sq /0.005 inches = 0.2 Ohms/inch. This means a length of Len × 0.2 Ohms/inch > 1 Ohms, means a length of > 5 inches has a DC resistance > 1 Ohms. This does not mean the interconnect will not work if it is longer than 5 inches. It just means you should pay attention to see if the 1 Ohm DC series resistance is significant.

4.24 The drilled diameter of a via is typically 10 mils. After plating it is coated with a layer of copper equivalent to about ½-ounce copper. If the via is 64 mils long, what is the resistance of the copper cylinder inside the via?

You can approach this problem in two ways. You can just take the cross-sectional area and length and calculate the end-to-end series resistance. Alternatively, you can do a simpler analysis.

If you slit the via from top to bottom and unwrap the via to flatten it out, the width of the trace would be the circumference, or 3.14 × 10 mils = 32 mils. The length of the via is 64 mils. This means it is about 2 squares long. If the sheet resistance is 1 mOhm/sq and it is 2 squares long, the series resistance of the via will be about 2 mOhms.

4.25 Sometimes, it is recommended to fill the via with silver filled epoxy, with a bulk resistivity of 300 µOhm-cm. What is the resistance of the fillet of silver filled epoxy inside a through via? How does this compare with the copper resistance? What might be an advantage of a filled via?

You can estimate the resistance of the fillet of silver filled epoxy. The resistance will be

You see that the resistance of the silver filled epoxy is more than 10× larger than the copper in the wall of the via. Filling the via with silver filled epoxy will not reduce the series resistance of the via very much.

The value of using silver filled epoxy is so that the top surface is flat and solderable.

4.26 Engineering change wires on the surface of a board sometimes use 24 AWG wire. If the wire is 4 inches long, what is the resistance of the wire?

The resistance of 24 AWG wire is about 0.08 Ohms/m or 2 mOhms/inch. With a wire that is 4 inches long, the resistance of the engineering change wire would be 2 mOhms/inch × 4 inches = 8 mOhms. This is generally a small value and not a significant contribution to the electrical properties of the engineering change wire.

Chapter 5

5.1 What is capacitance?

Capacitance is usually defined as the ratio of the charge separated between two conductors to the voltage between them. While this is correct, it doesn’t say much about what really is capacitance.

The principle behind capacitance is that when you separate charges on two adjacent conductors, there is a voltage difference between them. The capacitance between the plates is really a measure of how efficient the conductors are at storing charge, at the price of voltage.

The more charge you can store for a small amount of voltage difference, the more capacitance the conductors have. If you have conductors that are not very efficient, they can’t store much charge before the voltage goes way up.

The capacitance of two conductors is not related to how much charge is on the conductor, nor what the voltage is. It is about the efficiency of storing the charge at the cost of voltage.

5.2 Give one example where capacitance is an important performance metric.

The input gate capacitance of a receiver is concentrated in a very small region at the pad on the die and directly below it. When a signal is received, it is coming from some impedance—either the drivers output impedance, or the transmission line’s characteristic impedance.

When the signal reaches the gate capacitance, the voltage is increased as current flows in. The time it takes for the input gate capacitor to charge up is a measure of the received signal rise time.

The larger the input gate’s capacitance, the longer it takes to charge and the longer the rise time at the receiver. When this rise time becomes a significant fraction of the unit interval, timing problems result.

5.3 What are two different interpretations of what the capacitance between two conductors measures.

Interpretation 1: Capacitance is the ratio of the charge stored to the voltage across the two conductors. It is a DC effect.