PROCESSORS AND ARCHITECTURE

This appendix lists ARM processor names together with their core name and Instruction Set Architecture (ISA). We have omitted processors designed prior to the ARM7TDMI.

For example, Table C.3 shows that the ARM966E-S processor has a ARM9E core and implements ARM architecture version 5TE. Any ARMv5TE binaries will execute on an ARM966E-S processor.

C.1 ARM NAMING CONVENTION

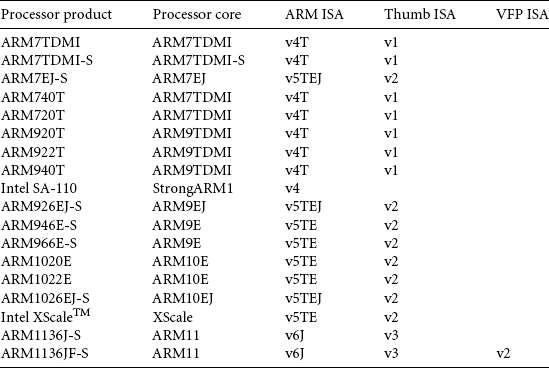

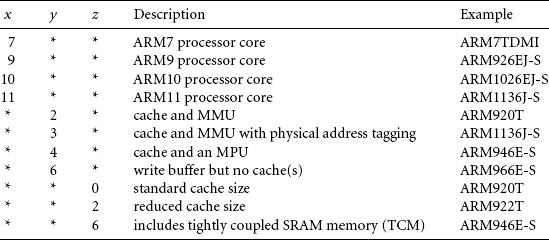

All ARM processors share a common naming convention that has evolved over time. ARM cores have the name ARM{x}{labels}, where x is the number of the core and labels are letters representing extra features, described in Table C.1. ARM processors have the name ARM{x}{y}{z}{labels}, where y and z are numbers defining the processor cache size and memory management model. Table C.2 lists the rules for ARM processor numbering.

Table C.1

| Attribute | Description |

| D | The ARM core supports debug via the JTAG interface. The D is automatic for ARMv5 and above. |

| E | The ARM core supports the Enhanced DSP instruction additions to ARMv5. The E is automatic for ARMv6 and above. |

| F | The ARM core supports hardware floating point via the Vector Floating Point (VFP) architecture. |

| I | The ARM core supports hardware breakpoints and watch points via the EmbeddedICE cell. The I is automatic for ARMv5 and above. |

| J | The ARM core supports the Jazelle Java acceleration architecture. |

| M | The ARM core supports the long multiply instructions for ARMv3. The M is automatic for ARMv4 and above. |

| -S | The ARM processor uses a synthesizable hardware design. |

| T | The ARM core supports the Thumb instruction set for ARMv4 and above. The T is automatic for ARMv6 and above. |

The labels, or attributes, are often subsumed into the architecture version over time. For example, the T label indicates the inclusion of Thumb in ARMv4 processors. However, Thumb is included in ARMv5 and later processors, so it is not necessary to specify the T after this point.

C.2 CORE AND ARCHITECTURES

Table C.3 shows each ARM processor together with the core and architecture versions that the processor uses.