2

Memory Applications for the Intelligent Internet of Things

2.1 Introduction

The Intelligent Internet of Things (IoT) is a term used here for smart networks of processing systems communicating with each other, analyzing the data generated, and responding to the conclusions of this analysis. These networks are expected to improve smart automation in many fields. Examples of such smart networks of systems communicating with each other are: wearable medical devices that take data and transmit it regularly to the network to aid in medical monitoring and evaluation of patients; networks in smart houses that detect motion, fire, smoke, state of door locks; and control cameras or audio devices and turn on/off household equipment under the guidance of a smart network controller. Communicating tags are used everywhere on IoT sensors and they need to be very low cost and work with very low levels of intermittently harvested energy. Energy harvesting is a requirement for the many sensors required in such ubiquitous networks since replacing batteries would be prohibitive. Where batteries are used, ultralow power is required. The many devices used in an IoT network must be very low cost.

Data storage is needed in smart networks. Memories are required to collect the information and process it. Many microcontroller units (MCUs) for IoT have the required memory embedded in the processor. In addition, the processors themselves must have near zero power consumption in standby since most of their time will be spent there. They may need in some cases to power up in the state required without taking time and power to boot‐up. This can be done using nonvolatile nodes in the processors, which can be implemented in some cases using high endurance memory devices such as ferroelectric RAMs (FeRAMs) or magnetic RAMs (MRAMs) on these nodes for power gating. For faster program speed for code and data storage and lower program voltage than Flash memory, resistive RAM (RRAM) could be used. For moderate performance at very low cost, phase change memory (PCM) might be used.

A few of the applications that have been studied for memories for IoT are detailed in this section. These include: ultralow power MCUs with energy harvesting sensors or compact batteries, smart communication tags, networks of wearable medical devices, smart motors, automotive networks, smart meters, and big data search engines.

Annual shipments of MCU with embedded nonvolatile memory were discussed by Renesas in January of 2014 [1]. These are illustrated in Figure 2.1 from 1980 to 2000 along with an indication of the primary embedded nonvolatile memory in each time period: first generation mask ROM, second generation embedded one‐time‐programmable (OTP) memory and third generation embedded Flash. Logic‐based eNVMs are added and a forecast is made to 2020 by extending the data trends. It was estimated by Renesas that MCUs with embedded Flash memories accounted for about 70% of all MCU shipments in 2011.

Figure 2.1 Estimate of shipments of MCU chips with embedded nonvolatile memory (BU annually).

Based on T. Kono et al. (Renesas). IEEE Journal of Solid‐State Circuits, January 2014 [1].

2.2 Comparisons of the Various Nonvolatile Embedded Memories Characteristics

2.2.1 Embedded EEPROM, Flash, and Fuse Devices

An early rewriteble embedded nonvolatile memory was the floating gate electrically erasable programmable read only memory (EEPROM) followed soon after by the dual polysilicon Flash memory. Both of these devices were made in the double polysilicon technology still used for standalone devices. Since conventional CMOS logic technology, in which MCUs tend to be made, does not use double polysilicon, the double polysilicon EEPROM and Flash memories added cost to the process when embedded in a processor technology.

Embedded EEPROM and Flash devices that used single polysilicon and were compatible with the conventional CMOS logic technology, were developed in the 1980s. The cost of the technology was lower than for devices made from double polysilicon but the cell size was larger. For very small amounts of embedded memory, a larger cell size was not a significant cost issue. For larger memory capacity or for off‐chip memory, the double polysilicon technology continued to be used.

A comparison between the characteristics of different types of embedded Flash memories can illustrate the trade‐offs between performance and array size. A comparison of various embedded Flash and EEPROMs as a function of array bit count and write cycles was done in October of 2015 by the University of Brescia [2]. Devices considered were: double polysilicon floating gate embedded Flash, single polysilicon EEPROM, transistor‐based antifuse devices, and polysilicon fuse devices. An illustration of the bit‐count versus write cycle characteristics of these embedded Flash memory technologies is shown in Figure 2.2.

Figure 2.2 Array capacity versus endurance for various types of embedded Flash memory cells.

Based on L. Milani et al. (University of Brescia), IEEE Trans. on Electron Devices, October 2015 [2].

The polyfuse and antifuse solutions for NVM are suitable for one‐time programmable (OTP), small density (<100b) and medium density (<100Kb) applications, but multiple time programmable applications require double poly embedded Flash or single poly EEPROM. The double polysilicon eFlash is suitable for applications of more than 1 M‐bit capacity where the additional cost due to the extra masks and process steps is acceptable. The single poly EEPROM is the best choice for low and medium density applications requiring up to 1 Mb of memory

2.2.2 Embedded Emerging Memory Devices in MCU

Various new memory devices have been investigated to solve the shortcomings of conventional SRAM and Flash storage. These include: magnetic RAM (MRAM), resistive RAM (RRAM), phase change memory (PCM), ferroelectric RAM (FeRAM), and charge trapping Flash memories, such as SONOS, MONOS, and nanoparticle. Many applications discussed here, particularly for IoT, will use the memory embedded in an MCU. The Flash MCU requirements for the various applications differ significantly and affect the type of embedded nonvolatile memory and RAM that can be used in the MCU for that application.

Among the differentiating characteristics of various embedded nonvolatile memories are the endurance to repeated write cycling and the write cycle time. A representation of an analysis done by Qualcomm in June of 2014 of the endurance and write cycle time of various emerging embedded nonvolatile memories is illustrated in Figure 2.3 [3]. This analysis included not only conventional embedded floating gate Flash but also the various emerging memories that are in development and production including: STT‐MRAM, FeRAM, PCM, and RRAM. STT‐MRAM and FeRAM tend to have the longest write cycle endurance, between 1012 and 1015 cycles, and a shorter write cycle time. The 1T1C FeRAM, however, has a destructive read, which means that every read or write cycle affects the endurance. It is, therefore, better suited for applications with limited numbers of read cycles such as datalogging. The 1 T FeRAM does not have a destructive read but is early in its development cycle. PCM and ReRAM have lower endurances at 104 to 106 write cycles with about the same write cycle time as the FeRAM.

Figure 2.3 Write endurance (cycles) versus write time (ns) for different memory cell types including: SST‐MRAM, FeRAM, PCM, RRAM, and embedded Flash memory.

Based on S.H. Kang (Qualcomm), VLSI Technology Symposium, June 2014 [3].

All of the emerging memories have superior characteristics to the conventional embedded Flash. The STT‐MRAM and the FeRAM have better write endurance and shorter write times than the eFlash. The PCM and RRAM have a shorter write time but about the same endurance. The characteristics determine to a large extent the application for which the particular memory is better suited.

The growth of the Internet enabled devices has created many applications that rely on communication between multiple devices and data storage in these devices. This includes: wearable systems, systems for IoT, and search and storage for big data processing. Nonvolatile embedded memories have become a focus of attention due to the large amount of standby power required for embedded SRAM and the limitations of battery technology. Also of concern is the high program/erase voltages, slow read/write speed, and limited endurance of mainstream Flash memory.

A large number of IoT devices are expected. Gartner has forecast that 6.4 billion connected things (IoT) will be in use worldwide in 2016, up 30% from 2015 [4]. They further forecast that this will reach 20.8 billion by 2020. In January of 2013, Cisco ISBG estimated that 50 billion IoT products would be in existence by 2020 at a value in US$ of 14.4 trillion [5].

2.2.3 Required Properties of Embedded Nonvolatile Memories in Various Applications

While standalone nonvolatile memories have standardized requirements agreed on throughout the industry and defined in industry standards committees among users and vendors, embedded nonvolatile memories have reliability dependent on the specific circuit in which they are embedded and the applications for which the circuit is intended. Typical reliability requirements for embedded nonvolatile memories in general MCU applications were indicated by Samsung in May of 2014 and are shown in Figure 2.4 [6]. The special reliability requirements for smart card and automotive MCU applications were also indicated and are shown in Figure 2.5.

Figure 2.4 Typical reliability requirements for NV memory embedded in MCU.

Based on Y.K. Lee et al. (Samsung), IMW, May 2014 [6].

Figure 2.5 Special reliability requirements for nonvolatile embedded memory in MCU for smart card and automotive applications.

Based on Y.K. Lee et al. (Samsung), IMW, May 2014 [6].

Further nonvolatile memory characteristics for various systems intended for IoT applications were discussed by Renesas in April of 2015 [7]. For automotive power train, auto body, and airbag applications, the embedded Flash memory was seen to be adequate for automotive system and performance requirements. As the number of connected systems and the functionality of those systems rose in 2015 for automotive systems, the performance increased for power train, body, and airbag applications. The embedded nonvolatile memory type preferred in Automotive Systems remained the eFlash macro, as shown in Figure 2.6, which indicates the automotive system and performance requirements in 2015.

Figure 2.6 Automotive system and performance requirements in 2015.

Based on T. Yamauchi (Renesas), VLSI‐TSA, April 27, 2015 [7].

These requirements are changing rapidly as the smart connected applications evolve and numbers given here are only indications at a point in time. Automotive electronics remains one of the largest of the Flash MCU sectors. New automotive applications include body and engine processors, infotainment, and driving aids up to completely autonomous cars. Automotive requirements are stringent and include a wide operational temperature range along with high performance and long endurance. This is an application that does not require ultralow power.

Smart card and medical sensors had specification requirements that could be satisfied by embedded Flash memory. For normally off sensor systems it was projected that embedded RRAM or embedded MRAM might also need to be used [7]. Smart cards are another application requiring ultralow power. This includes the rapidly growing bank card application and requires high reliability and secure communications for the card and banking network. Medical devices also required high reliability and secure communications. Smart card and medical device requirements are very different from those of the automotive applications. Power and performance requirements for these systems currently are shown in Figure 2.7. Medical sensors require lower power than smart cards, but do not require the performance at this time, as indicated in the figure.

Figure 2.7 Smart card and medical sensor requirements.

Based on T. Yamauchi (Renesas), VLSI‐TSA, April 27, 2015 [7].

Other IoT applications include: networks of digital utility meters, secure home networks, and networks of portable and wearable medical devices. The multiple sensors required in these connected applications require either ultralow power for infrequent changes of batteries or energy harvesting. These criteria are changing constantly and many other applications with differing requirements exist for Flash MCU. The smart electric grid needs network controllers for digital utility meters. Home networks require security and reliable functionality. Secure wireless network chips need smart crypto‐processors while high performance SSD requires integrated storage class memories.

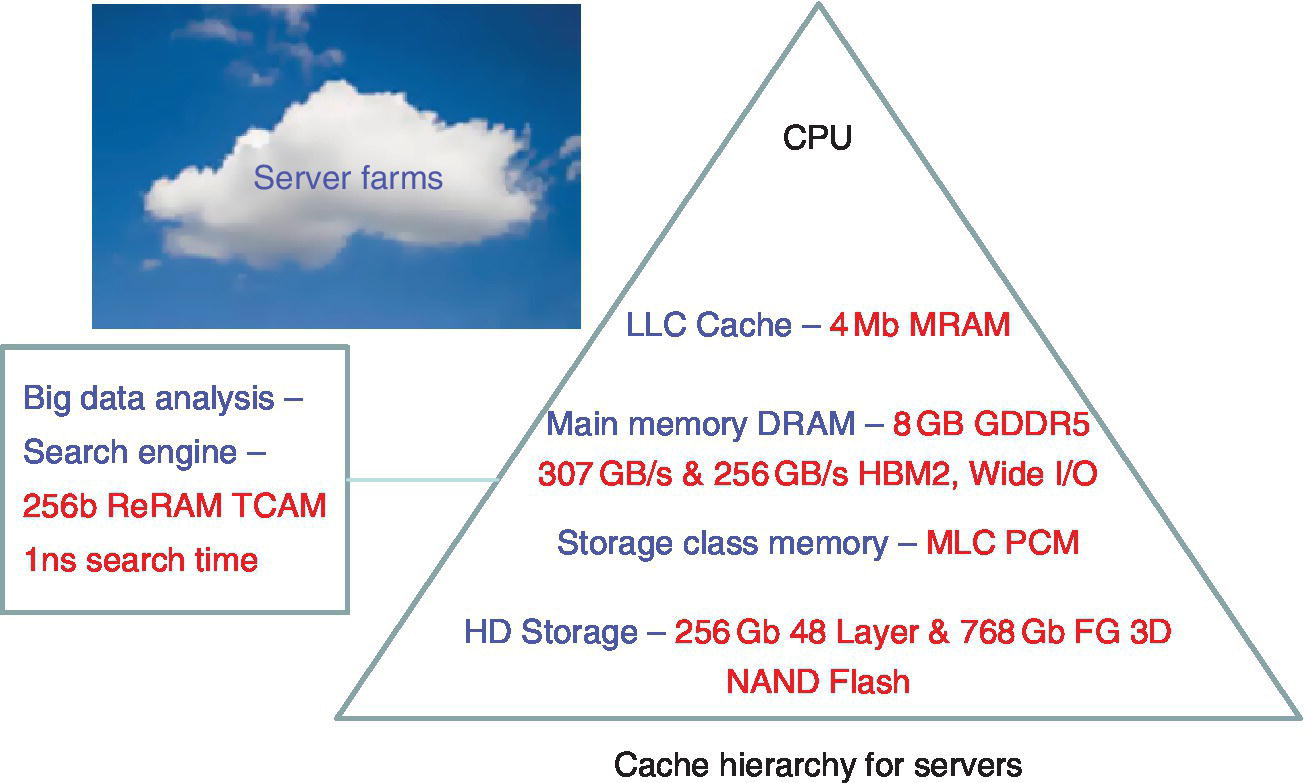

The requirement for the handling of massive data generated by the billions of IoT devices requires large search engines made of nonvolatile memory Ternary CAMs (TCAMs) for high volume data storage in the cloud and at the edge of the Internet perhaps smart computers for processing local data for efficient use. The development of neuromorphic computers with learning capability can perhaps serve this application primarily in vision and hearing analysis. Neuromorphic computers in development are using the analog characteristics of emerging memory chips such as FeRAM, PCM, RRAM, and MRAM.

The predominant types of memory embedded in MCU today are SRAM and Flash NVM with some emerging memories such as FeRAM and RRAM beginning to be used for ultralow power applications. General capabilities of embedded Flash in MCU were discussed by Freescale (now NXP) in May of 2015 and ranged from low end 8‐bit MCU in a 350 nm process, which may have 256 to 512 bytes of Flash, to a high end 32‐bit automotive MCU in a 55 nm process with up to 8.5 MB of Flash memory [8]. Flash memory is used to store boot and application codes, device configuration parameters or personalization information. Requirements are application dependent.

The silicon costs associated with large amounts of embedded Flash in advanced logic processes have to compete with system‐in‐package processes. These systems interconnect discrete memories with an MCU often in stacked chip solution using copper pillar interconnects and through silicon vias (TSV). These packaging costs will come down with time and compete with true embedded Flash. IoT connectivity is causing situations where it is not possible to embed sufficient Flash in the MCU to satisfy the storage requirements for the required amount of data for the application. In this case, integrated MCU and nonvolatile memory system‐in‐package processes might be used. Wafer level integration of high performance memory and processor chips on flexible substrates is also an advancing technology.

Circuits used in IoT applications can be very specialized and require other specifications for the processor and embedded memory. Examples are ultralow power MCU, high speed MCU, and flexible high and low performance devices. In the next section the characteristics of MCU being introduced for some of these specialty applications that occur in the Internet of Things area are discussed.

2.3 Circuits Using Ultralow Power MCU with Embedded Memory for Energy Harvesting

2.3.1 Introduction to Ultralow Power MCU Using Energy Harvesting

Ultralow power MCUs are used today in systems powered by coin batteries or energy harvesters where electrical system energy is not feasible. These MCU serve a variety of IoT applications like wireless home automation, security systems, and wearable medical electronics. In future IoT networks, these applications are more likely to be powered by energy harvesting or coin cell batteries and, as a result, require electronics that consumes very low energy.

The Internet of Things (IoT) uses sensors and MCUs on various devices that are connected through the Internet. With IoT, trillions of sensors are used on devices for collecting information such as temperature, humidity, motion, strain, magnetic field strength, etc. In some cases it is feasible to harvest solar, electromagnetic, or mechanical energy and store it in batteries or capacitors to power these devices.

2.3.2 Ultralow Power MCU with Embedded Flash Memory for Energy Harvesting

Many wireless sensor applications make use of energy harvesting. Ultralow power sensor nodes in wireless sensor networks are being developed for applications such as wearable devices.

A Flash MCU intended for energy harvesting applications was discussed by ST Microelectronics in January of 2014 [9]. This MCU was intended for cost‐sensitive applications and used a low end RISC processor core. Target applications included IoT and smart energy devices. This Flash MCU had 16KBytes to 128KBytes of embedded Flash memory and was expected to bridge the 8‐bit and 16‐bit MCU world. The MCU had crystal‐less USB2.0 and CAN interfaces with a self‐calibrated clock system. It also had a battery charger detection system, controlled power management, and separate power for analog and digital I/Os to support low voltage digital and high voltage analog operation.

2.3.3 Ultralow Power MCU with Embedded FeRAM Memory for Energy Harvesting

It was expected that the energy harvesting applications would require the use of emerging memories with microampere operating and nanoampere standby capabilities. A Texas Instrument’s MCU with an embedded two transistor and two ferroelectric capacitor (2T2C) FeRAM cell was used as an ultralow power processor for this application [10]. This MCU ran up to 25 MIPS. Clock frequencies could be relatively slow ranging, in this case up to 16 MHz. The power supply was specified for battery operation from 1.8 to 3.6 V. The device was optimized for ultralow power mode operation including a 1.7 μA standby current and a 15 nA shutdown current. Active power was typically 126 μA/MHz. The embedded FeRAM memory offered 1015 cycle read and write endurance. The electrical characteristics of the MCU with embedded FeRAM for energy harvesting are summarized in Figure 2.8.

Figure 2.8 Characteristics of an embedded FeRAM MCU for energy harvesting sensor applications.

Based on Texas Instruments Press Release, March 24, 2015 [10].

For computing devices that are transiently powered, such as in energy harvesting systems, the logic state needs to be retained on power down. Such a computing device depends on an intermittent power supply that has bursts of energy that are very short, often less than 100 ms. Purdue University in January of 2014 discussed such transiently powered computers (TPCs) [11]. The primary concern when using conventional embedded Flash memory with higher power processors is that frequent system reboots can result. An SRAM or Flash memory could be used with a battery, but the battery would tend to run down due to the long erase/write time of the Flash memory. A method was followed called Quick Recall, which used ferroelectric memory to enable long running computations in TPCs. This method saved and restored a checkpoint in only 12.6 μs, which is a significantly shorter time than would be required with Flash memory. A Texas Instruments MCU with embedded FeRAM was used. The system showed a significant improvement in program execution time over using an MCU with embedded Flash memory.

Checkpointing performed at previously determined points in the program stored a snapshot of system state in the FeRAM. In case of a fault, the system went back to the most recent check point. To avoid interfering with the normal computations, checkpointing with FeRAM is done only when a drop in the supply voltage occurs. The checkpointing was completed before the power was lost by choosing an appropriate trigger voltage for the FeRAM to begin the checkpointing operation. The program state retained was that of the global variables in use by the program. This study showed that transiently powered computers could do computations even when they receive power for periods as short as 5 ms.

An energy harvesting device can also be made using a low power single ferroelectric transistor (FeFET) memory. An example of an energy harvesting device using an FeFET was given by Panasonic in June of 2014 [12]. The advantage of the FeFET over the 1T1C FeRAM is that the endurance is not affected by a read cycle since the device does not require rewrite after read.

The FeFET energy scavenger used a low cost cantilever‐type 28 μm piezoelectric polyvinylidene fluoride (PVDF) film with a screen printed silver (Ag) ink electrode laminated on to a 0.125 mm polyester substrate. The PVDF cantilever converted energy from mechanical vibration into electric power. A reusable battery‐less impact logging device using a vibration energy scavenger and an FeFET was shown to be functional and suitable for portable use. Figure 2.9 shows the PVDF cantilever in the circuit with the FeFET memory.

Figure 2.9 Circuit schematic of PVDF piezoelectric vibration energy scavenger cantilever in circuit with FeFET memory.

Based on Y. Kaneko et al. (Panasonic), DRC, June 22, 2014 [12] (permission of IEEE).

The FeFET used a ferroelectric material as a dielectric layer in a MOS FET structure, as shown in Figure 2.10. The FeFET consisted of a stack of ferroelectric Pb(Zr, Ti)O2 (PZT) perovskite oxide film on a 30 nm thick SrRuO2 bottom gate deposited on a sliced stacked trench oxide (STO) substrate by pulsed laser deposition. This combination enabled oriented growth of ZnO on top of the PZT layer with a sharp ZnO/PZT interface.

Figure 2.10 Schematic illustration of an FeFET with stacked ZnO/PZT/SrRuO2 structure.

Based on Y. Kaneko et al. (Panasonic), DRC, June 22, 2014 [12] (permission of IEEE).

2.3.4 Ultralow Power MCU with Embedded RRAM Memory for Energy Harvesting

When solar energy is harvested to power an IoT application, a boost converter can be used to increase the solar battery voltage so a nonvolatile memory can be programmed and the sensor data stored. In November of 2015, Chuo University discussed a boost converter for RRAM programming in low power IoT applications [13]. An embedded RRAM was used for the code and data storage since it has faster program speed and smaller program voltage at 3 V than NAND Flash, which uses about 20 V for programming. A RRAM cell was assumed to use 3.0 V SET voltage and 25 μA program current. A representation of the 1T1C structure of the RRAM cell array is shown in Figure 2.11.

Figure 2.11 Schematic circuit diagram of the 1T1C resistive RAM (RRAM) cell array structure.

Based on T. Ishii et al. (Chuo University), IEEE A‐SSCC, November 2015 [13].

2.3.5 Ultralow Power MCU for Energy Harvesting Power Management

Another circuit using solar energy harvesting was discussed in August of 2015 by Cypress Semiconductor [14]. This family of energy harvesting power management integrated circuits (PMIC) consisted of single chip solar cells as small as 1 cm2 in area. These devices were fully integrated circuits making them a potential for use in smart homes, commercial buildings, and factories. The circuits were able to monitor physical and environmental conditions for these smart buildings.

The solar cells were naturally dependent on placement and available light for energy harvesting applications. Startup power was 1.2 μW and current consumption was as low as 250 mA, which optimized the power available for sensing, processing, and communications depending on the application. A complete, battery‐free energy harvesting system could pair the PMIC with a Bluetooth module for low energy connectivity.

Another energy harvesting device was introduced by TI in 2016 [15]. It was designed to efficiently extract microwatts to milliwatts of power generated from a variety of high output impedance DC sources, such as solar generators or thermal electric generators, without collapsing these sources. Battery management features were used to ensure that the associated rechargeable battery was not overcharged by the extracted power or depleted beyond safe limits by a system load. The cold start voltage was 330 mV. The device allowed continuous energy harvesting from a source as low as 100 mV. Full operating quiescent current was typically 488 nA and the maximum charge current was 100 mA.

2.4 Ultralow Power Battery Operated Flash MCU

2.4.1 Introduction to Ultralow Power Battery Operated Flash MCU

Ultralow power MCUs serve a variety of IoT applications like energy metering, home automation, security systems, industrial control, and portable medical electronics, as indicated in Figure 2.12. These applications are likely to be either powered by energy harvesting or by low current batteries and require very low energy operation along with zero power standby and rapid wakeup from standby.

Figure 2.12 Ultra‐low power IoT battery operated applications used with emerging memory technologies.

Some emerging memory devices, such as RRAM and FeRAM, switch faster than Flash memory, operate at lower voltages, and have a lower operating current. Like Flash memory, they are nonvolatile. MCU with these emerging memories embedded in the processor chip could provide extended battery operating life for portable devices if they are also capable of being manufactured in conventional CMOS processes at low cost.

Ultralow power battery operated Flash MCU require low current consumption to prolong battery life. This low current can be obtained by various current detection and power management control circuits. Separating power for analog and digital circuits can help. Using lower current EEPROMs can also reduce current consumption. Operational modes such as fast wake‐up from standby and longer times in low power states combined with fast switching can also reduce power. Various of these power lowering options that have been used are shown in Figure 2.13. These include: current detection circuits, power management control circuits, separate power for analog and digital circuits, low current EEPROM macros, fast wake‐up from standby and longer times in low power states with fast switching.

Figure 2.13 Power lowering techniques for ultralow power battery operated Flash MCU systems.

2.4.2 Ultralow Power Battery Operated Flash MCU with Embedded Flash Memory

An MCU with embedded Flash memory, targeted at cost‐sensitive battery powered applications, was announced in January of 2014 by ST Microelectronics [16]. This MCU used 16 KB to 128 KB of embedded Flash memory and a low end RISC processor core. Target applications included IoT and smart energy devices. This series was expected to bridge the 8‐bit and 16‐bit world. The MCU had crystal‐less USB 2.0 and CAN communication interfaces with a self‐calibrated clock system. To help control power consumption, it had battery charger detection and system controlled power management. Separate power for analog and digital I/Os helped to support low voltage digital and high voltage analog operation.

In order to target applications operating on smaller batteries such as wearable devices and industrial sensor networks, lower power consumption was required. In February of 2014, STMicroelectronics announced an ultralow power Flash MCU featuring a 32 MHz RISC processor core, a 100 k sps ADC consuming 40 μA, and crystal‐less USB FS2.0 [17]. Up to 64 KB of Flash memory could be integrated along with 2 KB of embedded EEPROM in the CMOS logic technology. Target applications included fitting smaller coin batteries on portable medical equipment such as fitness trackers and glucose meters. The analog‐to‐digital converter (ADC) consumed 40 μA at 100 k sps and up to 200 μA at 1.14 M sps, so a coin battery could operate a fitness tracker for two years. The CMOS technology had low variation over the –25 to 125 °C temperature range.

An energy efficient MCU with RISC core and embedded Flash memory intended for use in ultralow power IoT applications was introduced by Cypress in November of 2015 [18]. The device was optimized for advanced wearables along with a range of ultralow power battery‐powered products. The MCUs offered up to 560 KB of Flash memory and 64 KB of SRAM. The devices had fast wake‐up time from standby, which minimized power consumption by being able to remain in low power states for longer times before switching briefly to active mode. Active current was 40 μA. The device offered the ability to move data between peripherals and RAM without CPU intervention. Communication interfaces offered advanced encryption standard (AES) hardware encryption. AES is a symmetric block cipher used to protect classified information and to encrypt sensitive data. The communication interfaces included: multifunction serial interfaces, USB, a smart card interface, and I2C for digital audio. Some analog peripherals were included.

2.4.3 Ultralow Power Battery Operated MCU with Embedded RRAM

Ultralow power MCUs that are operated on battery optimize the current available by storing data at a low current level during the write operation so the optimum data storage is obtained. An RRAM discussed by Panasonic in July of 2013 was embedded in an 8‐bit MCU and was intended to replace Flash memory [19]. It had stable low current operation as a result of the electric current being kept constant during the RRAM forming process so that the resulting filaments were uniform. A metal oxide RAM (OxRAM) technology was used for the RRAM. This RRAM used Ta2O5 to control oxide density and defects during the deposition of a tantalum layer. The intended battery‐backed applications require low power operation and include devices such as sensors, security systems, and portable healthcare devices. Electrical and reliability characteristics of 8‐bit MCU with embedded RRAM intended for use in battery powered circuits are shown in Figure 2.14.

Figure 2.14 Electrical and reliability characteristics of 8‐bit MCU with embedded RRAM for use in battery powered circuits. An oxide RAM (OxRAM) technology was used for the RRAM.

Based on Panasonic Press Release, July 30, 2013 [19].

The MCU with the embedded RRAM operated at voltages as low as 0.9 V, which permitted low power consumption. Standby current was 60 nA with a 3 V power supply and an operating current of 200 nA during real time clock operation. Compared to a comparable MCU with embedded Flash (eFlash), the power consumption was about half. In a comparable eFlash MCU, the write voltage was given as 2.7 V and the write speed as 30 μs/byte, while in the MCU with eRRAM, the write voltage was 1.8 V and the write speed was 3 μs/byte.

With the embedded RRAM, the device is turned on for a much shorter time and at lower voltage so less current is consumed. The ‘ewrite cycle endurance for the eRRAM was 100 000 cycles, which is comparable to the eFlash. The RRAM still needed to be installed in the back‐end process, after which it was expected to be usable at various process nodes. The initial production was in Panasonic's 180 nm process. In February of 2017 Panasonic and UMC in Taiwan began joint development of a 40 nm RRAM platform [20].

2.4.4 Ultralow Power Battery Operated MCU with Embedded FeRAM

An embedded FeRAM in a low power MCU was discussed by Texas Instruments in June of 2013 [21]. Standby current consumption was reduced to 350 nA by using critical blocks and other architectural tailoring. Fast wake‐up within 6.5 μs from standby mode or sleep mode was achieved using analog precharge current sources. For the lowest system energy, power management was divided into blocks.

A power management block diagram of the MCU is shown in Figure 2.15. This block diagram illustrates the details of the dedicated power subsystem. The system is partitioned into different power domains in order to power‐off circuitry that is currently unused. A low dropout (LDO) linear regulator is used as a low cost, accurate power supply. The real time clock (RTC) domain is separated so only 350 nA of current is consumed while the RTC is running. The memory FeRAM LDO is also separated. The core domains are power gated. The precharge current sources directly source the power gated domains from the 3 V VCC supply for fast startup of the power gated domains.

Figure 2.15 Power management block diagram of the low power FeRAM MCU.

Based on A. Baumann et al. (Texas Instruments), VLSI Circuits Symposium, June 12, 2013 [21].

The major blocks consist of the 16‐bit MCU core and digital logic with dedicated power domains for debug and the real time clock (RTC), power management module (PMM), and analog and memories including FeRAM, RAM, and ROM. Features and target applications of the 16‐bit MCU with embedded FeRAM intended for use in battery powered circuits are shown in Figure 2.16.

Figure 2.16 Features and target applications of 16‐bit MCU with embedded FeRAM intended for use in battery powered circuits.

Based on A. Baumann et al. (Texas Instruments), VLSI Circuits Symposium, June 12, 2013 [21])

The 130 nm CMOS technology used 5‐layer copper (Cu) metal interconnects. Chip size was 0.12 mm2. The MCU ran at 16 MHz and the FeRAM capacity was 64 KB. A block diagram of the MCU with eFeRAM is shown in Figure 2.17. Blocks shown are: the clock, nonvolatile FeRAM, RAM, and 16b RISC processor.

Figure 2.17 Block diagram of the MCU with eFeRAM.

Based on A. Baumann et al. (Texas Instruments), VLSI Circuits Symposium, June 12, 2013 [21].

Many IoT sensing applications require extended battery life for sensing and measurement applications. In March of 2016, TI announced an MCU with embedded FeRAM that offered a configurable low leakage transimpedance amplifier with 20 times lower leakage than previous solutions and therefore potentially offered an extended battery life [22]. The MCU included a configurable analog, which reduced printed circuit board (PCB) space. The analog integration permitted connecting to a wide range of sensors. It integrated a ferroelectric RAM nonvolatile memory. The fast read and write of the FeRAM permitted configuring the amount of memory allocated for application code or data by eliminating the boundaries between Flash and RAM. The FeRAM MCU offered a higher performance than the previous generation MCU, which used Flash. Applications targeted included: medical health and fitness and building automation. TI proposed adding an energy harvesting IC to extend the battery life even further.

2.5 Nonvolatile MCUs Using Emerging Memory for Nonvolatile Logic

For MCUs in battery powered or energy harvesting applications, it is essential that standby power be ultralow. This can be accomplished in the logic by power gating, which is turning off the power in a block of circuits. If a nonvolatile memory cell is associated with a logic node then the logic state of that node is stored in the event of power‐down and can be restored on startup. This latter technique essentially eliminates standby power. In this case, the MCU does not need to be supplied with power during standby and comes up in the previously stored state when the power is restored.

2.5.1 Nonvolatile Logic Arrays Using FeRAM

The state of a nonvolatile data Flip‐Flop (nvDFF) can be stored in an embedded FeRAM capacitor. In February of 2013, MIT and TI discussed the design of an nvDFF with embedded ferroelectric capacitors that sense data [23]. The nvDFF was integrated into the ASIC design flow with a power management unit and a simple interface to the brown‐out detection circuitry. This design managed power by operating normally “off”. The process technology included embedded ferroelectric (FE) capacitors that store data. Prior to sensing, the FE capacitors are programmed to opposite data states. Identical charging currents integrate the difference in remnant charge between the two FE capacitors, as shown in the circuit schematic in Figure 2.18. The first node to cross the diode voltage drop plus a PMOS threshold pulls the internal node of the sense latch high.

Figure 2.18 Illustration of ferroelectric (FE) capacitors connected to a nonvolatile data flip‐flop (nvDFF).

Based on M. Qazi et al. (MIT, TI), ISSCC, February 2013 [23].

The FIR filter was designed with 96 nvDFFs and about 500 gates. For the target application, which was an MCU, about 5000 nvDFFs were retained. The nvDFF has a split supply rail so sensing current ramps can be perturbed. With zero skew, all nvDFFs in the five measured chips, a total of about 21 000 nvDFFs, operated without failure and the distribution of skew indicated a below 1 ppm failure for an unskewed nvDFF. The additional energy cost from nodes glitching in the FIR filter, cycle overhead, and programmable memory unit (PMU) energy is about 1.780 pJ out of 3.439 pJ.

Commercial ultralow power (ULP) MCUs need to balance different requirements by providing high performance and very low standby power along with fast wake‐up time for various real time applications. In November of 2013, TI and TSMC discussed a full high voltage threshold (HVT) 8 MHz 75 μA/MHz nonvolatile logic (NVL)‐based MCU with zero standby power and fast 384 ns wake‐up time [24]. In this processor, nonvolatile miniarrays are distributed though the logic domain of the MCU, which take a snapshot of the state of all sequential elements before the MCU goes into a power‐gated standby mode. Upon wake‐up, no boot‐up is required.

These miniarrays use ferroelectric capacitors for fast low power nonvolatile state retention. The ferroelectric capacitors are programmable capacitors that retain their programmed state without a power source. The read plus write endurance of the FeRAM is >1015.

A high bandwidth parallel connection between the flip‐flops and miniarrays helped achieve a fast MCU wake‐up. Nonvolatile logic (NVL) had no impact on MCU active mode performance and power. It added only 3.6% to the chip area. Since the NVL eliminates leakage in standby mode, it permits use of high performance leaky processes in MCU design.

The system architecture of the MCU is shown for a second generation full standard voltage threshold (SVT) 32 MHz nonvolatile logic MCU in the block diagram in Figure 2.19. The SVT SoC has four times higher active mode performance or 30% lower active energy than the HVT SoC, but can still achieve zero leakage using the nonvolatile logic. This created a zero leakage fast wake‐up standby mode and also provided benefits in active power and performance. In particular, it is expected to be useful for energy harvesting applications.

Figure 2.19 System architecture of the MCU showing 32b core and nonvolatile logic (NVL) controller.

Based on S. Khanna et al. (TI, TSMC), A‐SSCC, November 11, 2013 [24].

This 130 nm nonvolatile logic (NVL) based 32b MCU SoC backs up its working state, which includes all flip‐flops, upon receiving a power interrupt. TI reported in January of 2014 that this MCU has zero leakage in sleep mode and requires less than 400 ns to restore the system state on power‐up [25]. A low power technology is used with a 1.5 V power supply. Nonvolatile ferroelectric capacitor‐based miniarrays back up the machine state and permit the chip to wake up instantly after a power cycle. Without the NVL, a chip would either need to keep all flip‐flops powered, which would result in high standby power, or the system would need to spend energy and time rebooting after each power‐up.

NVL permits systems to use leakier processes to achieve higher performance and lower dynamic power while retaining zero leakage in sleep mode. In this case, the addition of the NVL only adds 3.6% to the SoC area. Process cost adders are minimized since only two additional masks are required for the ferroelectric NVL implementation. A functional diagram of the NVL SoC is shown in Figure 2.20.

Figure 2.20 Functional diagram of NVL 32‐bit SoC with FeRAM program and data memory.

Based on S. Khanna et al. (Texas Instruments), IEEE JSSC, January 2014 [25].

The voltage regulation, supply detection and PM state machines are off‐chip. The MCU SoC discussed has zero sleep mode leakage with a 400 ns wake‐up time. The chip has 100% digital state retention. System wake‐up time is reduced from 100 s of microseconds to a few microseconds since no boot‐up is required after a power cycle. Before entering the sleep mode, data from all flip‐flops and latches in the system are transferred to the ferroelectric capacitor‐based NVL arrays.

The NVL can be used in any digital system with two system requirements: the system must be edge triggered synchronous and the clocks for all flip‐flops must be stopped in the inactive state while going into the sleep mode. The SoC has conventional FeRAM memory. The NV elements added to the SoC are tested and the reliability ascertained. NVL bit‐cell read signal margins are measured and there is a test and debug capability.

2.5.2 Nonvolatile Logic Arrays Using MTJ MRAM

Another processor using power gating and a nonvolatile array was described in November of 2013 by Tohoku University and NEC [26]. This power‐gated MPU uses a nonvolatile flip‐flop (nvFF) with a magnetic tunnel junction (MTJ) MRAM type of memory. The nvFF was used to store the MPU’s internal state. The power‐gating operation for this MPU had a 3 μs entry/exit delay penalty during power on and power off. This was one order of magnitude faster than a conventional MPU in deep power‐down mode. An nvFF circuit was developed to obtain this small entry/exit delay with stable fast store and recall. The power‐gated mode was easy to control. This processor core was based on a 32‐bit pipeline architecture.

In the power‐gated MPU, all necessary processor internal states are stored in NV memory. This includes executing programs in the instruction memory and some temporary calculation results in the register file. This means the MPU can immediately return from the suspended state and restart program execution. This move into and from the power‐off mode does not require obtaining or storing data from external memories, which makes the entry/exit delay short. A nonvolatile latch circuit diagram using MTJ MRAM elements in CMOS technology is shown in Figure 2.21.

Figure 2.21 Basic NV latch circuit diagram using magnetic tunnel junction (MTJ) nonvolatile memory elements in CMOS technology.

Based on H. Koike et al. (Tohoku University, NEC), A‐SSCC, November 11, 2013 [26]. (Permission of IEEE).

A detailed SPICE simulation analysis of a CMOS/MTJ hybrid circuit was executed and the design and fabrication of a prototype MPU chip was done. Results showed that power gating had a 3 μs penalty for entry/exit delay. This was an order of magnitude faster than for a conventional MPU deep power‐down.

Processors with MTJ‐MRAM nonvolatile arrays can also be used for intermittent operations.

A fully nonvolatile MCU with an embedded emerging NV‐RAM memory was discussed by NEC and Tohoku University in February of 2014 [27]. This 90 nm CMOS 16‐bit MCU used a three transistor SpinRAM memory consisting of two transistors and one MTJ MRAM (2 T + 1MTJ) and was intended for use in applications such as battery‐powered sensor nodes. The MCU operated at 20 MHz with 145 μW operation with a 1 V power supply in the active state and 4.5 μW intermittent operation with a 120 ns wake‐up time and 0.1% active ratio without needing to forward reboot code from memory. Power consumption was sufficiently low that battery powered sensor nodes were effectively free of maintenance. A block diagram of the MCU with embedded SpinRAM memory is shown in Figure 2.22.

Figure 2.22 Block diagram of nonvolatile 65 KB RAM/ROM unified (2T+1MTJ) SpinRAM MCU.

Based on N. Sakimura et al. (NEC, Tohoku University), IEEE ISSCC, February 2014 [27].

The MCU had a 16b RISC CPU core, a 64 KB RAM/ROM unified SpinRAM macro and other logic circuits including timers, a 32‐bit multiplier, a power management module (PMM), universal serial interfaces (USCI), and a direct memory access (DMA) module. It had some redundant words and columns to replace defective cells and an error correction code (ECC) circuit for write failures.

To eliminate backup and restore overhead through the memory bus, 4096 nonvolatile magnetic flip‐flops (MFF) were used to capture the context of the CPU. Two instructions permitted software to flexibly back up and restore data to the MFFs. V cc was 1.8 V to 3.3 V with a 1 V internal power supply provided by a DC/DC converter. The MCU supported three low power modes: standby mode, power‐gating mode and sleep mode. In standby mode, all cores remained on and the main clock was gated, resulting in a 117 μW leakage current. In power‐gating mode, 1.6 μW was consumed with all cores turned off. In sleep mode the DC/DC converter was turned off and static power was zero.

A similar digital system where there is no distinction between ON and OFF and where the computational state is stored in NV Logic elements was discussed in January of 2014 by Cypress, TI, and MIT [28]. This system was intended to operate from harvested energy without requiring reboot. A nonvolatile D‐Flip‐Flop (nvDFF) was designed in 130 nm CMOS technology. The nvDFF was integrated into an ASIC design flow.

A test case nonvolatile FIR filter is discussed with a power management unit that automatically saved and restored the state of a one‐bit indicator of energy availability. Correct operation was verified over power cycle intervals from 4.8 μs to 1 day. The round trip save–restore energy is 3.4 pJ per nvDFF. Measurements were made to validate the capability to make a 10 parts per minute (ppm) failure rate for embedded system applications.

An illustration of the designed operation of nonvolatile processing is shown in the graph in Figure 2.23, which shows VDD plotted against time. The system performs useful computations in between unpredictable interruptions in the availability of harvested energy. During an interruption the data are retained.

Figure 2.23 VDD versus time of computations in energy harvesting type system with NVDFF showing computations interspersed with times of retained data.

Based on M. Qazi et al. (Cypress, MIT, TI), IEEE Journal of Solid‐State Circuits, January 2014 [28].

2.5.3 Processors with RRAM for Nonvolatile Logic Arrays

The power of many SoCs tends to be dominated by the leakage power of the embedded memories and the status registers. Leakage current and active power can be reduced by power supply scaling to the near threshold range or even into the subthreshold range. Low power memories can also help reduce the leakage. RRAMs are nonvolatile and therefore have low standby power dissipation and can be operated at low voltages. In November of 2014, EPFL, the Swiss Federal Institute of Technology, discussed energy and reliability trade‐offs in a low voltage RRAM‐based nonvolatile flip‐flop (nvFF) design [29]. In this study, RRAM nvFF are optimized for operation in the low voltage and subthreshold ranges. A 180 nm CMOS process was used with a compatible voltage of 2 V and a low current compliance of 10 μA.

Three low voltage nvFF circuits were evaluated for power dissipation and reliability. Topologies are used that have two complementary programmed RRAM devices. Monte Carlo simulations are used to determine parametric variations and confirm data restore operations from the RRAM devices in subthreshold ranges as low as 400 mV. Minimal energy is found for a near voltage threshold (V t) read operation with a total read plus write energy of 735 fJ. A block diagram of a nonvolatile flip‐flop is shown in Figure 2.24. This is a conventional master–slave flip‐flop with write and read registers indicated.

Figure 2.24 Conventional master–slave nonvolatile flip‐flop.

Based on I. Kazi et al. (EPFL), IEEE Trans. on Circuits and Systems, November 2014 [29].

RRAMS can be used in field programmable gate arrays (FPGA) as well as nvFF. In December of 2014, CEA and LETI Minatec discussed RRAMS for both FPGA and for nvFF [30]. In FPGAs, replacing the SRAM with RRAM saves area since the cell size of the RRAM is smaller than that of the SRAM and the nonvolatility suppresses standby power consumption. The leakage current through the RRAM during operation depends on the high resistance state (HRS) value. For this reason, a specific type of RRAM, a conductive bridge RAM (CBRAM) with a dual layer electrolyte stack and resistance ratio (high resistance state divided by low resistance state) greater than 10, was suggested to minimize operating leakage current. The resistance ratio is also called the ON/OFF current ratio. The CBRAM was made of a dual layer of solid electrolyte, HfO2 and GeS2, embedded between an Ag electrode and a W plug.

The use of RRAM in fixed logic circuits such as nvFFs permits zero standby leakage and fast power ON/OFF operation. The requirements for an RRAM in an nvFF are: endurance, low operating voltage, and fast ON/OFF operation. An HfO2/Ti metal oxide RRAM cell, an OxRAM, with less than 10 ns switching time at 1 V and endurance up to 108 cycles was also suggested for this application. This OxRAM’s active layer was HfO2 between TiN and Ti/TiN electrodes. A schematic cross‐section is shown in Figure 2.25. Figure 2.25(a) shows the OxRAM stack and Figure 2.25(b) shows the CBRAM stack with GeS2 and with the HfO2/GeS2 electrolyte with an Ag top electrode and a W bottom electrode. Devices with a large memory window such as the HfO2/GeS2 CBRAM enable high density, low leakage cells for FPGA. Cells with low voltage, time switching, and high endurance such as the HfO2/Ti OxRAM permit a fast switching fixed logic design.

Figure 2.25 Schematic of (a) OxRAM RRAM stack and (b) CBRAM with HfO2/GeS2 electrolyte.

Based on E. Vianello et al. (CEA LETI), IEDM, December 2014 [30].

Nonvolatile SRAMs (nvSRAM) are conventionally constructed using two nonvolatile memory devices and a 6 T SRAM. In June of 2015, several Taiwanese labs and universities discussed an RRAM‐based 7T1R nonvolatile SRAM [31]. The nvSRAM had a two times reduction in stored energy and 94 times reduction in restore energy for frequent‐off and instant‐on applications. The store energy is reduced by using only a single RRAM device rather than the two normally used. Also the DC short current is suppressed during the restore operation by using a pulsed overwrite method. A circuit schematic of the 7T1R nvSRAM cell is shown in Figure 2.26.

Figure 2.26 3D circuit schematic illustration of 7T1R nvSRAM.

Based on A. Lee (NTHU, NDL, NCHU, EOL ITRI), Symposium on VLSI Technology, June 2015 [31].

A high restore yield was attained by using a differentially supplied initialization method. This initialization and overwrite 7T1R nvSRAM improved breakeven time by 6 times compared to previous nvSRAMS. A 16 K‐bit 7T1R nvSRAM was made using an HfOx RRAM in a 90 nm CMOS process. In SRAM mode the read operation was the same as for the 6 T SRAM. The separation of CVDD lines permitted applying different voltages to VDDQ and VDDQB to improve the write margin.

In February of 2016, Tsinghua University, NTHU, and the University of California, Los Angeles, discussed a 65 nm RRAM enabled nonvolatile processor that had a 6 times reduction in restore time and a 4 times higher clock frequency when using Adaptive Data Retention and Self‐Write termination [32]. The processor used an adaptive nvFlipFlop with RRAM, a code storage RRAM macro, and an adaptive nvSRAM using RRAM. The system architecture of the RRAM enabled nvProcessor is shown in Figure 2.27.

Figure 2.27 System architecture of the RRAM enabled NV‐processor.

Based on Y. Liu et al. (Tsinghua University, National Tsing Hua University, University of California, Los Angeles), ISSCC, February 2016 [32].

A 65 nm fully logic compatible RRAM based nonvolatile processor (NVP) achieved time and space adaptive data retention. A one macro nvSRAM with self‐write termination (SWT) was integrated to increase the clock frequency and reduce stored energy. The adaptive retention made the RRAM write endurance, which was 106–1012 cycles, sufficient for most applications. The NVP operated at 100 MHz with 20 ns per 0.45 J restore time/energy. It had a 6 times reduction in restore time, more than 6000 times reduction in restore energy, and 4 times higher clock frequency than previous designs.

In October 2014, an OxRAM‐based pulsed latch was described by the University of Grenoble Alpes [33]. A schematic diagram of the nonvolatile scan flip‐flop is shown in Figure 2.28. The operating modes included store and restore. This device was made in 28 nm CMOS fully depleted SOI (FDSOI) technology. It used a nonvolatile flip‐flop (nvFF), thereby providing an ultralow standby power design for emerging connected devices for the Internet of Things (IoT), which operated on battery or harvested energy sources. The inclusion of nonvolatility in the flip‐flop eliminated power consumption in the sleep mode while maintaining the system state. The nvFF was designed as an OxRAM based pulsed latch tied to a regular flip‐flop to provide an ultrawide voltage range. The addition of nonvolatility cut off the flip‐flop leakage but used a 63 pJ data store and restore. This added less than a 15% delay penalty.

Figure 2.28 Schematic diagram of nonvolatile scan flip‐flop.

Based on A. Levisse et al. (University of Grenoble Alpes), IEEE SOI‐3D‐Subthreshold Microelectronics Technology, October 2014 [33].

2.6 Communication Protocols for Memory Sensor Tags

2.6.1 Radio Frequency Identification (RFID) Tags

Radio frequency identification (RFID) tags are used to identify and track everything from warehouse inventory to automobiles on freeways [34]. To increase usage, RFID tags must be very low power and low cost. For smart RFID tags containing SoC with embedded memory to be used, the application must require both fast access and nonvolatile reprogrammability. For example, RFID tags can reduce costs in automated manufacturing while maintaining control by recording stages of automated manufacturing. They can be used in retail tracking of expensive inventory and large shipping containers. RFID is also used in access control, payment systems, automatic meter reading systems, and many others.

RFID tags in retail are an upgrade from the ubiquitous Universal Product Code (UPC) bar code, which is on most retail products and could potentially replace them as the cost falls. While UPC is a read only memory (ROM), the RFID chip has the potential to be a read and/or write memory, that is, a ROM, a PROM (programmable read only memory), or an EEPROM (an electrically erasable programable read only memory). RFID tags can be inductively coupled consisting of metal coils and antenna powered by a magnetic field generated by the RFID reader, which induces a current in the tag. It can also be capacitively coupled using conductive ink instead of metal coils to transmit data.

RFID tags can be passive, semipassive or active. They all consist of a microchip and an antenna. Passive RFID tags rely on the reader for power and can be read up to 20 feet away.

Active and semipassive tags contain a battery. Data are stored in the RFID tag chip. When the chip’s antenna receives a signal from the RFID reader’s antenna, the tag uses its antenna to send a radio wave signal back to the reader. The power used by the chip to send its signal can either come from an internal battery or from energy harvesting most frequently coming from the reader’s electromagnetic field. Active and semipassive tags can broadcast high frequencies from 850 to 950 MHz that can be read 100 feet or more away. Additional batteries can be used to boost the range of the tag. High frequency RFID tags such as in smart cards can have a range of 3 feet or less. Other signal enhancement devices can be used. For example, traffic monitors include automated tolls that generally use RFID tags affixed to the car’s windshield (windscreen). The windshield enhances the signals, which are read by readers powered by electricity and can have a range of about 12 meters.

The RFID tag, to be useful, must have assigned a unique identifier and trillions of devices might eventually require identifiers. The electronic product code (EPC) identifier is commonly used and contains 96 bits of information. Information stored in the RFID chip is usually written in the product markup language (PML). The issue today for the universal acceptance of RFID is cost reduction in tags and readers. The processor in an RFID tag can be a conventional silicon MCU with embedded nonvolatile memory, but still needs to be cost reduced. Plastic printed roll‐to‐roll processing of RFID tag circuits including the MCU and memory has been developed and promises to eventually reduce the cost of an RFID tag; however, the performance of printed circuits is not yet as high as that of silicon.

2.6.2 Near Field Communications (NFC)

Near field communications (NFC) is a short range wireless communications protocol that uses RF signaling and enables communications between electronic devices that are either touched together or within a range of a few centimeters, generally less than 4 cm, permitting passing the device in front of the scanner. NFC devices combine RF signaling and an MCU with host interface circuitry and memory. The NFC protocol simplifies the pairing of Bluetooth or Wi‐Fi devices. The host interface can be a 38.4 kbps universal asynchronous receiver/transmitter (UART) or a 1 Mbps serial port.

NFC tags let everyday objects interact with smart devices such as cell phones and other mobile terminals. In February of 2015, Panasonic’s NFC tag platform was shown [35]. These tag ICs use low power, fast nonvolatile FeRAM along with secure data transmission with standardized encryption and authentication. They are compatible with NFC compliant mobile terminals. This NFC chip tag integrated RF, signal‐conditioning, host interface circuitry, and a 4 k‐bit embedded FeRAM in a surface mount package. Applications included: home appliances, health care systems, wearable medical devices, digital paper, smart keys, and smart meters. The FeRAM had 10 year data retention and a 0.33 mA current at 1 Hz compared to an EEPROM with a 2 mA current at 1 MHz. Write speed for 64 bytes was 154 μs compared to an EEPROM at 7.6 ms.

An RFID chip can have an EPC interface as well as an NFC interface. The EPC is similar to a bar code and acts as an identifier for retail inventory when using RFID tags. A fully integrated dual frequency RFID chip with both an NFC type 3 interface and EPC Gen2V2 RF interface was announced in April of 2015 by EM Microelectronics [36]. This circuit was intended for supporting EPC functionality for retail logistics and inventory control and for communicating directly with the consumer for marketing and advertising and product registration. This chip had a common rewriteable memory area, a unique ID, and security features. It also had a dual interface memory access of NFC or EPC and user data of more than 2Kb.

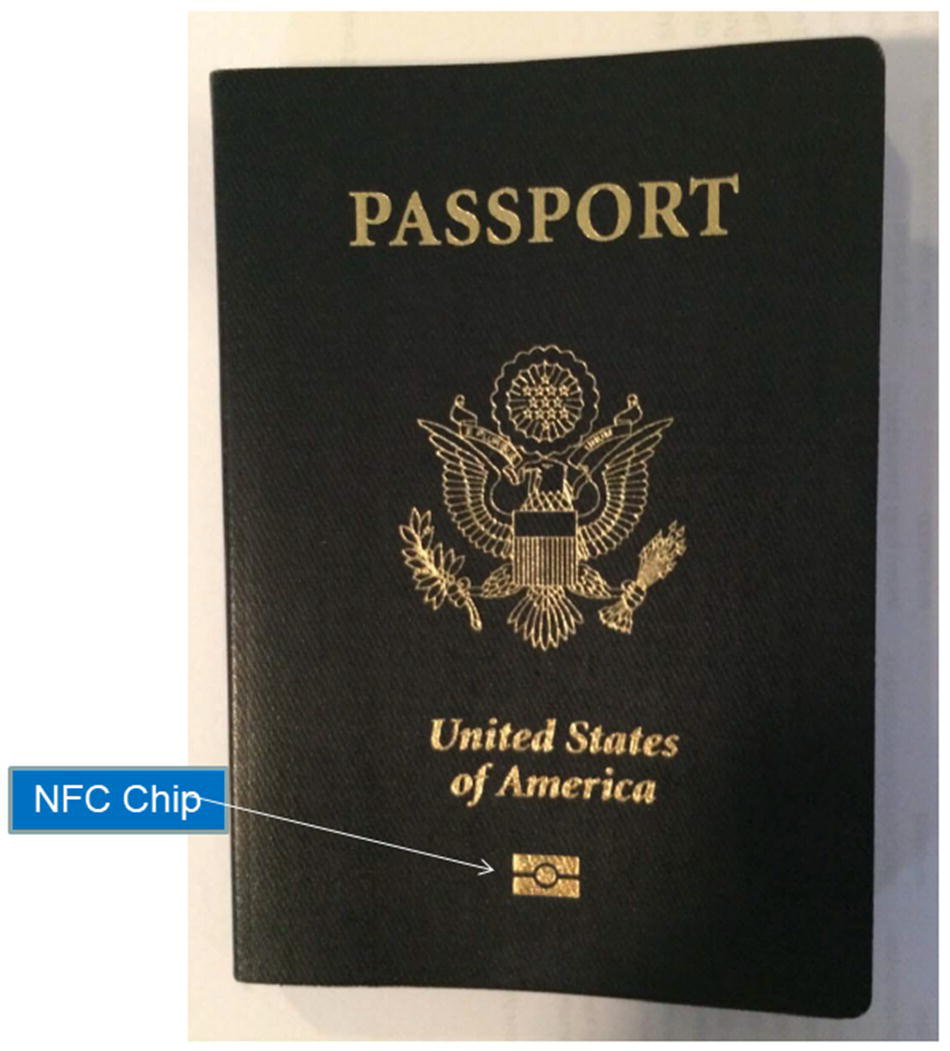

An example of the use of NFC is the US Passport, which has a chip with an embedded Flash processor with an NFC capability of being read when the cover is open. Figure 2.29 shows the closed cover of a US Passport with the location of the NFC chip indicated. The Passport uses an RFID chip, which is read using an NFC scanner. It can be read only when the passport is open due to a metal shield that is embedded in the cover of the passport.

Figure 2.29 Picture of US Passport with the cover closed, with the position of the NFC chip indicated.

Photo by B. Prince.

Tags can either be passive or active. Passive tags collect energy from an interrogating reader interface while active tags have a local power source. An example of an NFC tag family was introduced in February of 2016 by NXP for smart home applications. These tags combined a passive NFC interface and a contact I2C interface together with a nonvolatile memory [37]. This tag offered zero power capability along with password protection, full memory access from both interfaces, and an originality signature for protection against cloning. This second generation part had four times the data transfer performance of the first generation along with backward compatibility to earlier generations. It had a pass‐through mode with a 64‐byte SRAM buffer, a 1912 bit EEPROM user memory, 32‐bit password protection, NFC Type 2 tag, and a 7B serial number. An originality signature was based on elliptic curve cryptography for authentication. It used energy harvesting from the NFC field to power external devices. The operating temperature range was –40 to +105 °C.

2.6.3 Bluetooth‐Based Beacons and Sensor Nodes

Bluetooth is a standard protocol for securely transmitting data using a 2.4 GHz wireless link. It is used for short range, low power, and low cost wireless transmission between electronic devices. Standard Bluetooth has a range of 1–100 meters with a point‐to‐point topology while Bluetooth Smart has a range of 10–100 meters with a point‐to‐point star topology. Bluetooth can be used for smart retail beacons, which can recognize a nearby shopper’s mobile device and transmit information to the targeted shopper. See Figure 2.30 for an illustration of a shopper with a smart phone interacting with a retail beacon.

Figure 2.30 Illustration of retail beacon interacting with individual shopper’s smartphone.

These beacons can be preprogrammed to respond to particular user profiles. Macy’s department stores are reported to have implemented Bluetooth beacons [38]. In September of 2014, they reported expanded use of low energy beacons to include several departments in all stores. These beacons enabled a shopper, who elected to be in the system, to receive discount coupons and rewards while they were in a store based on their location in the store. Another possible application for beacons is in museum exhibits where exhibits can detect the presence of a user and transmit interesting information about nearby exhibits. Criteria for transmission might include a defined transmission range to avoid interference between individual beacons.

An illustration of a chip for a Bluetooth beacon was announced in December of 2014 by EM Microelectronics [39]. This was a coin‐sized beacon consuming less than 25 μA average current that typically provided 12 months operation from a single CR2032 coin battery included in the beacon. The beacon used an EMM ultralow power MCU. The 0.9 V 8‐bit RISC Flash MCU contained from 5 KB to 16 KB of Flash EEPROM and a miniature antenna that made the beacon detectable 75 meters away by an advanced smart phone. Its rugged package made it suitable for outdoor music festivals, sporting events, and arenas.

An early low energy Bluetooth compatible chip was introduced by Nordic Semiconductor in June of 2012 [40]. This multiprotocol Bluetooth 2.4 GHz RF Flash‐based SoC was designed as a single chip solution for applications such as fitness and healthcare wearable sensors. It included 256 KB of embedded Flash and 16kB of RAM. Peripherals included: SPI, two‐wire, ADC. The power supply range was 1.8 to 3.6 V. It included a DC/DC converter for 3 V coin cell batteries. A complete Bluetooth protocol stack was included along with 2.4 GHz RF protocols and 128 KB of Flash and 10kB of SRAM were available for an application code.

A Bluetooth Module Add‐on for IoT Designs was introduced in August of 2015 by Silicon Labs. This Bluetooth module was intended to help developers reduce development costs and improve compliance by adding a “plug and play” Bluetooth to their designs [41]. The module provided precertified use in the markets of North America, Europe, and Asia Pacific. The modules were preloaded with the Bluetooth 4.1 compliant software stack and were field upgradable to Bluetooth 4.2 and beyond.

Two Bluetooth ICs that supported Bluetooth Low Energy (LE) ver. 4.1 communications were introduced in November of 2015 by Toshiba [42]. One tag integrated a built‐in Flash ROM and the other supported both Flash ROM and NFC Forum Type 3 Tag for peer‐to‐peer communication. The latter device included a Flash ROM to store user programs and data along with a 64 KB user program area using an internal SRAM to execute various application programs. The chip’s NFC Tag achieved easy Bluetooth peer‐to‐peer pairing and power ON/OFF functions by touching another NFC supported mobile device. The built‐in Flash ROM eliminated any need for an external EEPROM and reduced external part counts and PCB size. The NFC tag was powered by small coin cell batteries.

It was expected that these devices would ease adoption of Bluetooth LE communications for small devices such as wearable healthcare devices, sensors, and toys. Characteristics of a typical Bluetooth LE type 3 Tag are shown in Figure 2.31. Communication was an NFC Type 3 Tag at 212 kbps/424 kbps. Security was mutual recognition by Triple DES Message Authentication code (MAC).

Figure 2.31 Characteristics of a typical Bluetooth LE type3 tag.

Based on Toshiba PR, November 17, 2015 [42].

Bluetooth is being added to applications such as connected home, wearables, remote controls, baby monitors, beacons, electronic shelf labels, audio equipment speakers, health and fitness devices, and point of sale equipment. Figure 2.32 is a photo of a wireless Bluetooth Speaker.

Figure 2.32 Illustration of wireless Bluetooth speaker.

Photo by B. Prince.

In February of 2016, Silicon Labs announced an SoC family intended to support these applications [43]. These Bluetooth SoCs consume 8.7 mA in the peak receive mode and 8.8 mA at 0 dBm in the peak transmit mode and offer –94 dBm sensitivity and output power from –30 dBm to +19.5 dBm. The 40 MHz RISC processor had a powerful floating point and DSP capability. It consumed 63 μA/MHz current in the active mode. An integrated hardware cryptographic accelerator permitted autonomous encryption and decryption of Internet security protocols with minimal CPU intervention.

Another MCU intended for wearables, IoT devices, sensor hubs, building automation, personal medical devices, and smartphones was introduced in December of 2015 by STMicroelectronics [44]. This MCU included an RISC core performing at 125 DMIPS and 339 EEMBC CoreMark at 100 MHz. The accelerator helped drive dynamic power down to 89 μA/MHz with STOP current of 6 μA. Communication includes NFC, Bluetooth, or IEEE 802.15.4 radio boards. The devices have from 64 KB to 128 KB of Flash and 32 KB of SRAM. A RUN mode permits the Flash to be powered down for power savings. To save power, sensor data could be captured directly into SRAM while the CPU and Flash remained off. It had six timers including motor control and 32‐bit/100 MHz timers. Communication ports included: SPI, I2C, I2S, USART, and ISO7816 interface along with a 12‐bit DAC.

2.6.4 IoT Devices with Wi‐Fi

A Wi‐Fi platform can be designed to help add ultralow power long range connectivity to IoT designs. Wi‐Fi is supported by laptops, smart phones, tablets, and other connected things, making it useful for device‐to‐cloud or device‐to‐device connectivity. In November of 2015, TI discussed an ultralow power Wi‐Fi platform using a sub‐1 GHz wireless MCU [45]. This wireless MCU offered 20 years of battery life for applications such as: building and factory automation, alarm and security, smart grid, and wireless sensor networks. The chip had an integrated RISC MCU sensor controller, low power modes, and 0.6 μA sleep current. The wireless sensitivity spanned from full building to citywide coverage for over 20 km on a coin cell battery with up to 128 KB of embedded Flash possible. The wireless MCU operated in various ISM bands. Communication protocols included: Bluetooth, Wi‐Fi, Zigbee, and others.

A plug and play Wi‐Fi module for use with Internet of Things (IoT) applications was discussed in February of 2016 by Silicon Labs [46]. The module had good RF performance, a small footprint, easy application development, and fast time to market. It included: a 2.4 GHz 802.11 radio, integrated antenna, global certifications, an MCU, an embedded Wi‐Fi stack, and various Internet protocols. By integrating the 802.11 radio, antenna, MCU and Wi‐Fi stack the module helped reduce development risk and accelerate the time to market. The module was useful for adding Wi‐Fi to industrial M2M systems, wireless sensors, remote controls, thermostats, connected home products, automotive infotainment, point‐of‐sale devices, and fitness and medical equipment. The module included a scripting language to develop and host end applications. It could run in a network co‐processor mode, enabling the host controller to handle applications tasks. The module enabled connectivity up to 300 m to 500 m typically and had a 2.4 GHz transceiver and an integrated high efficiency chip antenna along with peripherals including: UART, I2C, SPI, and USB. A Wi‐Fi protocol stack included protocols for cloud integration. A dedicated host interface was provided to external MCUs running the end application.

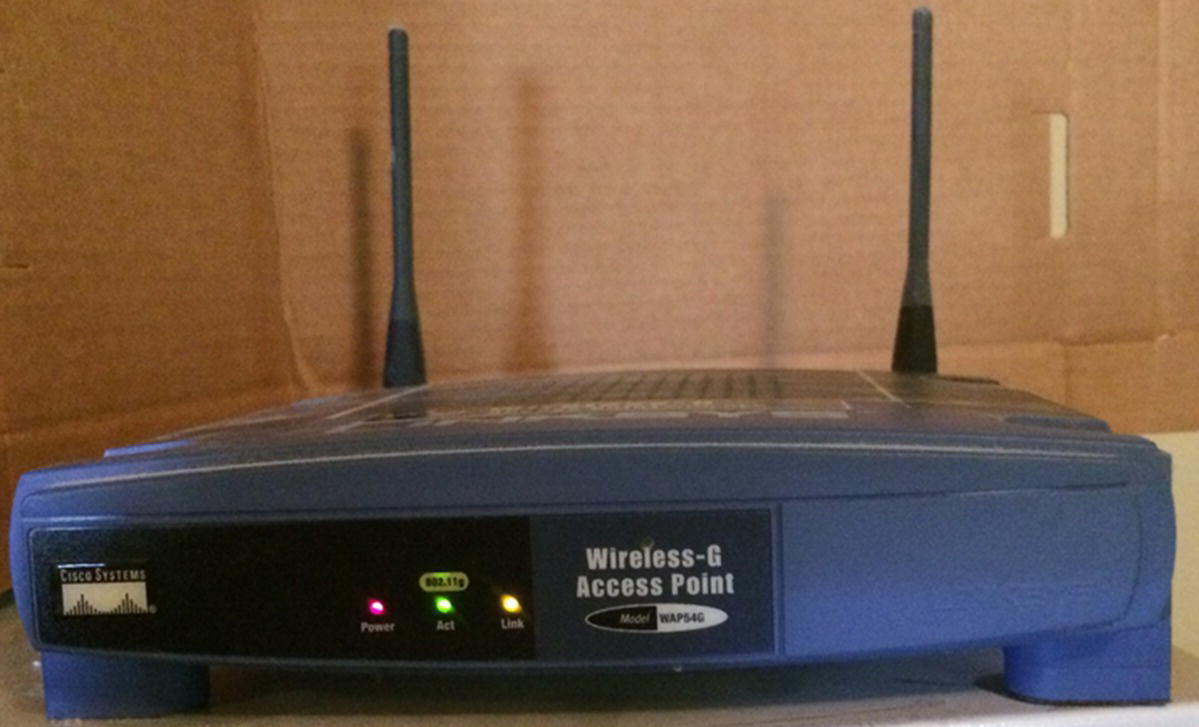

A wireless Wi‐Fi router is a device that performs the functions of a router and also those of a wireless access point. It can provide access to the Internet or to a private computer network. An office Wi‐Fi router is shown in Figure 2.33.

Figure 2.33 Office Wi‐Fi router used in the offices at Memory Strategies International.

Photo by B. Prince.

In February of 2016, Silicon Labs discussed a wireless SoC with embedded Flash [47]. The wireless SoC integrated an RISC processor, a 2.4 GHz radio with up to 19.5 dBm output power, and hardware cryptography. The design included Thread and Zigbee stacks for mesh networks, intuitive radio interface software for proprietary protocols, Bluetooth for point‐to‐point connectivity, and tools to simplify wireless development, configuration, debugging, and low energy design. The wireless portfolio included three options for multiprotocol SoCs optimized for IoT: one had wide output power and range, one had Zigbee and Thread connectivity for mesh networks, and one offered flexible proprietary wireless protocol options for different applications.

The wireless SoCs had a multiprotocol 2.4 GHz RF transceiver in a single chip with up to 256 KB of Flash and up to 32 KB of RAM. Energy modes included: fast wake‐up sleep transitions, a system that enabled autonomous operation of low power peripherals while the MCU core slept. The MCU included floating point capability and consumed 63 μA/MHz in active mode. It integrated a software programmable power amplifier and provided a scalable output power, which ranged from –30 dBm up to +19.5 dBm for applications requiring long range connectivity.

For security, the device had a built‐in hardware cryptographic accelerator, which provided fast, energy efficient autonomous encryption and decryption of Internet security protocols with minimal CPU intervention. The on‐chip accelerator supported algorithms such as AES with 128‐bit or 256‐bit keys, elliptical curve cryptography, and the secure hash algorithm (SHA)‐1 and its follow‐on SHA‐224/256. The hardware cryptography enabled developers to meet evolving IoT security requirements more efficiently than software only techniques.

2.6.5 IoT Devices with USB Connectivity

The Universal Serial Bus (USB) interface is a fast serial bus technology that permits an electronic device to be connected to a computer. USB Flash drives are Flash memory for data storage with a built‐in USB interface. Introduced in 1996, it was intended that all USB ports supply 5 V. USB2 could pull up to 100 mA while USB3 could draw from 150 mA to 900 mA.

An MCU was introduced in May of 2015 by Silicon Labs that enabled USB connectivity for a range of IoT applications including: smart metering, home and building automation, alarm and security systems, smart accessories, and wearable devices [48]. This 32‐bit MCU was based on a RISC core, low energy peripherals, and a range of memory options. It had an energy management system with five energy modes ranging from active mode to deep sleep mode. In deep sleep mode the MCU had 0.9 μA standby current with a 32.8 kHz RTC, RAM/CPU state retention, brown out detector, and power‐on‐reset circuitry active. Active power consumption dropped to 130 μA/MHz at 24 MHz with read word code using a prime number algorithm. There was a 2 μs wake‐up time from standby mode. On‐chip peripherals included: analog comparator, supply voltage comparator, on‐chip temperature sensor, programmable current DAC (IDAC), and a 12‐bit ADC with 350 μA current consumption at a 1 MHz sample rate. On‐chip AES encryption permitted secure wireless connectivity for IoT applications such as smart meters and wireless sensor networks. The chip eliminated many discrete devices by using a full‐speed USB PHY, an on‐chip regulator, and resistors.

IoT devices with USB connectivity for applications such as remote controls and thermostats have been introduced. In February of 2016, Silicon Labs introduced its 8‐bit MCU portfolio for IoT, which included low power capacitive touch control and USB connectivity [49]. One such MCU had speeds of up to 48 MHz and 8–64 KB Flash sizes and can be used for higher end personal medical devices, remote controls, and thermostats. These have a high precision internal oscillator, a clock recovery circuit, a full speed USB transceiver, along with an on‐chip battery charger detection module.

2.6.6 Single Wire Connectivity

Single wire connectivity has the advantage of minimizing the pins on the package to reduce the size of the package. In August of 2015, Atmel introduced a 2‐pin, self‐powered single‐wire serial EEPROM for the IoT and other markets [50]. The part was self‐powered by a parasitic power method over the data pin. It required just one data and one ground pin, which eliminated the requirement for external power. It had a plug and play 64‐bit serial number for identification. The device’s ultralow power requirements included a standby current of 700 nA, write current of 200 μA, and read current of 80 μA at 25 °C. The power scheme eliminated the need for external capacitors and rectifiers. The device had a high write endurance capability permitting more than one million cycles per memory bit. This device was targeted at IoT applications including wearables such as smart fitness and healthcare devices and consumables.

The devices followed the I2C protocol, which allows low overhead migration from existing EEPROMS and the capability of connecting up to eight devices on the same bus. The part had a security register with a 64‐bit factory programmed serial number and an extra 16‐bytes of user programmable and permanently lockable EEPROM storage for a unique serial number for inventory tracking and asset tagging. The data could be permanently protected. Different low voltage battery requirements were supported including low voltage applications at 1.7–3.6 V and 2.7–4.5 V for use with Li‐ion polymer batteries.

2.6.7 Zigbee Interface

Zigbee is a standard interface with a mesh topology and a range of 10–100 meters. Its maximum datarate is 250 kbit/s at 2.4 GHz [51]. It is intended as a communications protocol for creating personal area networks with low power digital radios for applications such as home automation and medical device data collection. It is a low power, low data rate, close proximity, personal area wireless network that is intended to be simpler than Bluetooth or Wi‐Fi.

2.6.8 ANT Interface

ANT is a proprietary interface with a range of 30 meters at 0 dB m. It is an adaptive isochronous network technology that ensures coexistence with other ANT devices. Each transmission occurs in an interference free time slot within the defined frequency band. Transmission is for less than 150 μs per message, which permits a single channel to be divided into numerous time slots [52].

2.7 Wearable Medical Devices

2.7.1 Overview of Wearable Medical Devices

Portable medical systems are a growing market due to the increasing proportion of Seniors in the population worldwide. These portable systems require large high performance memory but must have low power for battery operation. The wearable electronics part of this application includes devices for medical, fitness, and wellness, such as step tracking, heart rate and blood pressure monitors, blood glucose monitors, insulin pumps, hearing aids, and other. To service this application, suppliers of smart connected wearable devices will require low power platforms with simple basic features that include: a simple user interface, embedded processing for data collection, and sensors for environmental tracking. The portable medical system application also includes devices such as: miniature medical sensors, portable datalogging equipment, medical and pharmaceutical tracking, and implantable medical devices such as defibulators and pacemakers. Figure 2.34 is an illustration of a wireless network of wearable medical devices.

Figure 2.34 Wireless network of medical devices to medical suppliers and monitors.

Portable medical devices are expected to use embedded EEPROMS and Flash memory as well as fast access, low power nonvolatile emerging memories such as FeRAMs, Conductive Bridge (CB) RAMS, and MRAMs. Powering these devices will require either long term batteries or energy harvesting systems. These devices will need to be networked to medical surveillance systems and medical personnel requiring networks of IoT communication devices.

These portable networked medical devices are expected to be used increasingly by the aging population, which the United Nations estimates today at 900 million including 250 million in developed countries and another 650 million in developing countries [53]. This total is expected to grow to 1.2 billion by 2025. With medical care improving worldwide, these higher value portable medical and tracking devices could provide another large market for fast, low power nonvolatile memories.

2.7.2 Miniature Hearing Aids Using FeRAM Memory