CHAPTER 6

The Physical Basis of Inductance

Inductance is a critically important electrical property because it affects virtually all signal-integrity problems. Inductance plays a role in signal propagation for uniform transmission lines as a discontinuity, in the coupling between two signal lines, in the power distribution network, and in EMI.

In many cases, the goal will be to decrease inductance, such as the mutual inductance between signal paths for reduced switching noise, the loop inductance in the power distribution network, and the effective inductance of return planes for EMI. In other cases, the goal may be to optimize the inductance, as in achieving a target characteristic impedance.

By understanding the basic types of inductance and how the physical design influences the magnitude of the inductance, we will see how to optimize the physical design for acceptable signal integrity.

6.1 What Is Inductance?

There is not a single person involved with signal integrity and interconnect design who has not worried about inductance at one time or another. Yet, very few engineers use the term correctly. This is fundamentally due to the way we all learned about inductance in high school or college physics or electrical engineering.

Typically, we were taught about inductance and how it relates to flux lines in coils. We were introduced to the inductance of a coil with figures of coiled wires, or solenoids, with flux lines through them. Or, we were told inductance was mathematically an integral of magnetic-field density through surfaces. For example, a commonly used definition of inductance, L, is:

While all of these explanations may be perfectly true, they don’t help us on a practical level. Where are the coils in a signal-return path? What does an integral of magnetic-field density really mean? We have not been trained to apply the concepts of inductance to the applications we face daily—applications related to the interaction of signals on interconnects as packages, connectors, or boards.

While all this is true, we still need to understand inductance in a more fundamental way. Our understanding of inductance needs to feed our engineering intuition and give us the tools we need to solve real interconnect problems. A practical approach to inductance is based on just three fundamental principles.

6.2 Inductance Principle 1: There Are Circular Rings of Magnetic-Field Lines Around All Currents

There is a new fundamental entity, called magnetic-field lines, that surrounds every current. If we have a straight wire, as shown in Figure 6-1, for example, and send a current of 1 Amp through it, there will be concentric circular magnetic-field lines in the shape of rings created around the wire. These rings exist up and down the length of the wire. Imagine walking along the wire and counting the specific number of field line rings that completely surround it; the farther from the surface of the current, the fewer the number of field line rings we will encounter. If we move far enough away from the surface, we will count very few magnetic-field line rings.

Figure 6-1 Some of the circular magnetic-field line rings around a current. The rings exist up and down the length of the wire.

Where do these magnetic-field lines come from? Why are they created by moving charges in a wire? Like the properties of electric fields coming from charges, the properties of magnetic fields and their interaction with moving charges is built into the very fabric of spacetime. Electric and magnetic fields and their interactions with charges are intrinsic properties of spacetime that seems to have been frozen into the structure of spacetime about 1 nanosecond after the Big Bang. Whatever their origin, their properties seem to be incredibly well described by Maxwell’s Equations.

The magnetic-field line rings around a current have a specific direction, as though they were circulating around the wire. To determine their direction, use the familiar right-hand rule: Point the thumb of your right hand in the direction of the positive current and your fingers curl in the direction the field line rings circulate. This is illustrated in Figure 6-2.

Figure 6-2 The direction of circulation of the magnetic-field line rings is based on the right-hand rule.

TIP

Magnetic-field line rings are always complete circles and always enclose some current. There must be some current encircled by the field line rings.

As we walk along the wire with a current, we can imagine counting each specific magnetic-field line ring we encounter. When we count or measure the magnetic-field lines, it is only the number of rings we count.

In what units do we count the field line rings? We count pens in units of gross. There are 144 pens in a gross. Paper is counted in units of reams, with 500 sheets to each ream. Apples are counted by the bushel. How many apples are there in a bushel? It’s not clear exactly how many apples are in a bushel, but there is some number.

Likewise, we count the number of magnetic-field line rings around a current in units of Webers. There are some number of magnetic-field line rings in a Weber of field lines.

The number of Webers of field line rings we count around the current in the wire is influenced by a number of factors. First is the amount of current in the wire. If we double the current in the wire, we will double the number of Webers of magnetic-field line rings around it.

Second, the length of the wire around which the field line rings appear will affect the number of field line rings we count. The longer the wire, the more field line rings we will count. Third, the cross section of the wire affects the total number of field line rings surrounding the current. This is a second-order effect and is more subtle. As we will see, if the cross-sectional area is increased—for example, if the wire diameter is increased—the number of field line rings will decrease a little bit.

Fourth, the presence of other currents nearby will affect the total number of field line rings around the first current. A special current to watch for is the return current. As the return current of the first wire is brought closer, some of its field line rings will be so big as to also enclose the first current.

When we count the total number of magnetic-field line rings around the first wire, we will count its own rings, plus the rings from its return current. And, since the magnetic-field line rings around the first current circulate in the opposite direction, the total number of rings around the first wire will be reduced due to the proximity of the return current.

On the other hand, the presence of dielectric materials does not affect the number of field line rings around the current.

TIP

Magnetic fields do not interact with dielectric materials at all. There is no change in the number of magnetic-field line rings around a current if it is surrounded by Teflon or by barium titanate.

The fifth factor that may influence the number of magnetic-field line rings around a current is the metal of which the wire is composed. Only three metals affect the magnetic-field lines around a current: iron, nickel, and cobalt (and combinations of them).

These three metals are called ferromagnetic metals. They, or alloys containing them, have a permeability greater than 1. If any magnetic-field line rings are completely contained within one of these metals, the metal will have the effect of dramatically increasing the number of field line rings. However, it is only those field line rings that are circulating internally in the conductor that will be affected. Two common interconnect alloys, Alloy 42 and Kovar, are ferromagnetic because they both contain iron, nickel, and cobalt.

The composition of a wire made of any other metal, such as copper, silver, tin, aluminum, gold, lead, or even carbon, will have absolutely no effect on the number of field line rings around the current.

6.3 Inductance Principle 2: Inductance Is the Number of Webers of Field Line Rings Around a Conductor per Amp of Current Through It

Inductance is fundamentally related to the number of magnetic-field line rings around a conductor, per Amp of current through it.

TIP

Inductance is about the number of rings of magnetic-field lines enclosing a current per amp of the current, not about the absolute value of the magnetic-field density at any one point. Don’t worry about magnetic-field concentration, or density; worry about the number of magnetic-field line rings per Amp of current.

The units we use to measure inductance are Webers of field line rings per Amp of current. One Weber/Amp is given the special name, Henry. The inductance of most interconnect structures is typically such a small fraction of a Henry, it is more common to use nanoHenry units. A nanoHenry, abbreviated nH, is a measure of how many Webers of field line rings we would count around a conductor per Amp of current through it:

where:

L = inductance, in Henrys

N = number of magnetic-field line rings around the conductor, in Webers

I = current through the conductor, in Amps

If the current through a conductor doubles, the number of field line rings doubles, but the ratio stays the same. This ratio is completely independent of how much current is going through the conductor. A conductor has the same inductance if 0 Amps are flowing through it or 100 Amps. Yes, the number of field line rings changes, but the ratio doesn’t, and inductance is the ratio.

TIP

This means that inductance is really related to the geometry of the conductors. The only thing that influences inductance is the distribution of the conductors and, in the case of ferromagnetic metals, their permeability.

In this respect, inductance is a measure of the efficiency of the conductors to create magnetic-field line rings. A conductor that is not very efficient at generating magnetic-field line rings has a low inductance. A conductor has an efficiency whether or not it has current through it. The amount of current in the conductor does not in any way affect its efficiency. Inductance is only about a conductor’s geometry.

Inductance is not about the current in a wire. Inductance is not about how much magnetic field is around a wire. Inductance is not about how much concentration there is in the magnetic-field density around a current. Inductance is not about the energy stored in the magnetic field. Inductance is only about the efficiency of how good the conductor geometry is in creating magnetic-field line rings per amp of current.

We can apply this simple definition to all cases involving inductance. What makes it complicated and confusing is having to keep track of how much of the current loop we are counting the field line rings around and which other currents are present, creating field line rings. This gives rise to many qualifiers for inductance.

To keep track of the source of the magnetic-field line rings, we will use the terms self-inductance and mutual inductance. To keep track of how much of the current loop around which we are counting field line rings, we will use the terms loop inductance and partial inductance. Finally, when referring to the magnetic-field line rings around just a section of an interconnect, while the current is flowing through the entire loop, we will use the terms total inductance, net inductance, and effective inductance. These last three terms are used interchangeably in the industry.

Just using the term inductance is ambiguous. We must develop the discipline to always use the qualifier of the exact type of inductance to which we are referring. The most common source of confusion about inductance arises from mixing up the various types of inductance.

6.4 Self-Inductance and Mutual Inductance

If the only current that existed in the universe were the current in a single wire, the number of field line rings around it would be easy to count. However, when there are other currents nearby, their magnetic-field line rings can encircle multiple currents. Consider two adjacent wires, labeled a and b, as shown in Figure 6-3. If there were current in only one wire, a, it would have some number of field line rings around it, per amp of current through it, and some inductance.

Figure 6-3 Magnetic-field line rings around one conductor can arise from its own currents and from another current.

Suppose there were some current in the second wire, b. It would have some field line rings around it, per amp of current through it, and hence, it would have some inductance. Some of the field line rings from this wire, b, would also encircle the first wire, a. Around the first wire, a, there are now some field line rings from its own current and some field line rings from the adjacent (second) current, b.

When we count field line rings around one wire, we need a way of keeping track of the source of the field line rings. We do this by labeling those field line rings from a wire’s own currents as the self-field line rings and those from an adjacent current’s as the mutual-field line rings.

The self-field line rings are those field line rings around a wire that arise from its own currents only. The mutual-field line rings are those magnetic-field line rings completely surrounding a wire that arise from another wire’s current.

Every field line that is created by current in wire b and also goes around wire a must be around both of them. In this way, we say the mutual-field line rings “link,” or are around, both of the two conductors.

If we have two adjacent wires and we put current in the second wire, it will have some of its field line rings around the first wire. As we might imagine, if we move the second wire farther away, the number of mutual-field line rings that are around both wires will decrease. Move them closer, and the number of mutual-field line rings will increase.

But, what happens to the total number of field line rings around the first wire? If there is current through both wires, they will each have some self-field line rings. If the currents are in the same direction, the circulation direction of their self-field line rings will be the same. To count the total number of field line rings around the first wire, we would count its self-field line rings plus the mutual-field line rings from the second wire, because they are both circulating in the same direction.

However, if the direction of their currents is opposite, the circulation direction of the self- and mutual-field line rings around the first wire will be opposite. The mutual-field line rings will subtract from the self-field line rings. The total number of field line rings around the first wire will be decreased due to the presence of the adjacent opposite current.

Given this new perspective of keeping track of the source of the field line rings, we can make inductance more specific.

TIP

We use the term self-inductance to refer to the number of field line rings around a wire per Amp of current in its own wire. What we normally think of as inductance we now see is really specifically the self-inductance of a wire.

The self-inductance of a wire will be independent of the presence of another conductor’s current. If we bring a second current near the first wire, the total number of field line rings around the first may change, but the number of field line rings from its own currents will not.

TIP

Likewise, we use the term mutual inductance to refer to the number of field line rings around one wire per Amp of current in another wire.

As we bring the two wires close together, their mutual inductance increases. Pull them farther apart, and their mutual inductance decreases. Of course, the units we use to measure mutual inductance are also nH, since it is the ratio of a number of field line rings per Amp of current.

Mutual inductance has two very unusual and subtle properties. Mutual inductance is symmetric. Whether we send 1 Amp of current in one wire and count the number of field line rings around the other wire or send 1 Amp of current through the other and count the field line rings it produces around the first, we get exactly the same ratio of field line rings per Amp of current. In this respect, mutual inductance is related to the field line rings that link two conductors and is tied to both of them equally. We sometimes refer to the “mutual inductance between two conductors” because it is a property shared equally by the two conductors. This is true no matter what the size or shape of each individual wire. One can be a narrow strip and the other a wide plane. The number of field line rings around one conductor per Amp of current in the other conductor is the same whether we send the current in the wide conductor or the narrow one.

The second property is that the mutual inductance between any two conductors can never be greater than the self-inductance of either one. After all, every mutual-field line ring is coming from one conductor and must also be a self-field line ring around that conductor. Since the mutual inductance between two conductors is independent of which one has the source current, it must always be less than the smallest of the two conductors’ self-inductance.

6.5 Inductance Principle 3: When the Number of Field Line Rings Around a Conductor Changes, There Will Be a Voltage Induced Across the Ends of the Conductor

So far, we have discussed what inductance is. Now we will look at the “so what”: Why do we care about inductance? A special property of magnetic-field line rings is that when the actual, total number of field line rings around a section of a wire changes, for whatever reason, there will be a voltage created across the length of the conductor. This is illustrated in Figure 6-4. The voltage created is directly related to how fast the total number of field line rings changes:

Figure 6-4 Voltage induced across a conductor due to the changing number of magnetic-field line rings around it.

where:

V = voltage induced across the ends of a conductor

ΔN = number of field line rings that change

Δt = time in which they change

If the current in a wire changes, the number of self-field line rings around it will change, and there will be a voltage generated across the ends of the wire. The number of field line rings around the wire is N = L × I, where L in this example is the self-inductance of the section of the wire. The voltage created, or induced, across a wire can be related to the inductance of the wire and how fast the current in it changes:

TIP

Induced voltage is the fundamental reason inductance plays such an important role in signal integrity. If there were no induced voltage when a current changed, there would be no impact from inductance on a signal. This induced voltage from a changing current gives rise to transmission line effects, discontinuities, cross talk, switching noise, rail collapse, ground bounce, and most sources of EMI.

This relationship is, after all, the definition of an inductor. If we change the current through an inductor, we get a voltage generated across it. We sometimes describe this voltage as an induced electromotive force (EMF). This is a new voltage source, and it will act like a battery to pump current from the minus side to the plus side. The voltage polarity is created to drive an induced current that would counteract the change in current. This is why we say that “an inductor resists a change in current.”

If we happened to have an adjacent current in another wire, near the first wire, some of the field line rings from this second wire may also go around the first wire. If the current in the second wire changes, the number of its field line rings around the first wire will change. This changing number of field line rings will cause a voltage to be created across the first wire. This is illustrated in Figure 6-5. These changes in the mutual-field line rings contribute to the induced voltage across the first wire. When it is another conductor in which the current changes, we typically use the term cross talk to describe the induced voltage in the adjacent conductor. This induced voltage is a source of noise, an unwanted signal. In this case, the voltage noise generated is:

Figure 6-5 Induced voltage on one conductor due to a changing current in another and the subsequent changing mutual-field lines between them are a form of cross talk.

where:

Vnoise = voltage noise induced in the first, quiet wire

M = mutual inductance between the two wires, in Webers

I = current in the second wire

Because the voltage induced depends on how fast the current changes, we sometimes use the term switching noise or delta I noise when describing the noise created when the current switches through a mutual inductance.

To be able to analyze real-world problems that involve multiple conductors, we need to be able to keep track of all the various currents that are the sources of field line rings. The effects are the same; it’s just more complicated when there are many conductors, each with possible currents and magnetic-field line rings.

6.6 Partial Inductance

Of course, real currents only flow in complete current loops. In the previous examples, we have been looking at just a part of a circuit, where the only current that exists is the specific current in the part of wire we had drawn. As we counted field line rings, we ignored the rings from current in the rest of the current loop to which this wire segment belonged. When we look at the field line rings around part of a loop from currents in only part of the loop, we call this type of inductance the partial inductance of the wire.

It is important to keep in mind that when we speak of partial inductance, it is as though the rest of the loop does not exist. In the view of partial inductance, no other currents exist, except in the specific part of the conductor in which we are looking. The concept of partial inductance is a mathematical construct. It can never be measured, since an isolated current can never exist.

TIP

In reality, we can never have a partial current; we must always have current loops. However, the concept of partial inductance is a very powerful tool for understanding and calculating the other flavors of inductance, especially if we don’t know what the rest of the loop looks like yet.

Partial inductance has two flavors: partial self-inductance and partial mutual inductance. What we have been discussing above has really been the partial inductance of parts of two wires. More often than not, when referring to the inductance of a lead in a package, or a connector pin, or a surface trace, we are really referring to the partial self-inductance of this interconnect element.

The precise definition of partial self- and partial-mutual inductance is based on a mathematical calculation of the number of field line rings around a section of a wire. Take a fixed-length section of conductor that might be part of a current loop. Rip it out of the loop so it is isolated in space but maintains its original geometry. On the ends, put large planes that are perpendicular to the length of the conductor. Now imagine injecting 1 A of current, appearing suddenly in one end of the wire, traveling through the wire, coming out the other end, and disappearing back into nothing when it exits.

The only current that exists in the universe is in the section of wire between the end planes. From this small section of current, count the number of field line rings that fit between the two end-cap planes. The number of field line rings counted, per the 1 A of current in the wire section, is the partial self-inductance of that section of the conductor. Obviously, if we make the part of the wire longer, the total number of field line rings surrounding it will increase and its partial self-inductance will increase.

Now bring another short section of interconnect near this first section. Inject current from nowhere into the second wire and have it disappear out the opposite end. This partial current will create magnetic-field line rings throughout space, some of which will fit within the plane end caps of the first partial section of wire, completely enclosing the first wire segment. The number of field line rings around the first conductor segment, per Amp of current in the second wire, is the partial mutual inductance between the two sections.

Obviously, in the real world, we can’t create from nothing a current into the end of the wire without it coming from some other part of a circuit. However, we can perform this operation mathematically. The term partial inductance is a very well-defined quantity; it just can’t be measured. As we shall see, it is a very powerful concept to facilitate optimizing the design for reduced ground bounce and calculating the other, measurable terms of inductance.

There are only a few geometries of conductors with a reasonably good approximation for their partial self-inductance. The partial self-inductance of a straight, round conductor, illustrated in Figure 6-6, can be calculated to better than a few percent accuracy using a simple approximation. It is given by:

Figure 6-6 Geometry for the approximation of the partial self-inductance of a round rod. The length of the wire, d, is also represented by Len.

L = partial self-inductance of the wire, in nH

r = radius of the wire, in inches

Len = length of the wire, in inches

For example, an engineering change wire is typically 30-gauge wire, or roughly 10 mils in diameter. For a length that is 1 inch long, the partial self-inductance is:

TIP

This gives rise to an important rule of thumb: The partial self-inductance of a wire is about 25 nH/inch, or 1 nH/mm. Always keep in mind that this is a rule of thumb and sacrifices accuracy for ease of use.

We see that the partial self-inductance increases as we increase the length of the conductor. But, surprisingly, it increases faster than just linearly. If we double the length of the conductor, the partial self-inductance increases by more than a factor of two. This is because as we increase the length of the wire, there are more field line rings around this newly created section of the wire from the current in the new section, and some field line rings from the current in the other part of the wire are also around this new section.

The partial self-inductance decreases as the cross-sectional area increases. If we make the radius of the wire larger, the current will spread out more, and the partial self-inductance will decrease. As we spread out the current distribution, the total number of field line rings will decrease a little bit.

TIP

This points out a very important property of partial self-inductance: The more spread out the current distribution, the lower the partial self-inductance. The more dense we make the current distribution, the higher the partial self-inductance.

In this geometry of a round rod, the partial self-inductance varies only with the natural log of the radius, so it is only weakly dependent on the cross-sectional area. Other cross sections, such as wide planes, will have a partial self-inductance that is more sensitive to spreading out the current distribution.

Using the rule of thumb above, we can estimate the partial self-inductance of a number of interconnects. A surface trace from a capacitor to a via, 50 mils long, has a partial self-inductance of about 25 nH/inch × 0.05 inch = 1.2 nH. A via through a board, 064 mils thick, has a partial self-inductance of about 25 nH/inch × 0.064 inch = 1.6 nH.

Both the approximation and the rule of thumb are very good estimates of the partial self-inductance of a narrow rod. Figure 6-7 compares the estimated partial self-inductance for a 1-mil-diameter wire bond, based on the rule of thumb and the approximation given above, with the calculation from a 3D field solver. For lengths of typical wire bonds, about 100 mils long, the agreement is very good.

Figure 6-7 Partial self-inductance of a round rod, 1 mil in diameter, comparing the rule of thumb, the approximation, and the results from the Ansoft Q3D field solver.

The partial mutual inductance between two conductor segments is the number of field line rings from one conductor that completely surround the other conductor’s segment. In general, the partial mutual inductance between two wires is a small fraction of the partial self-inductance of either one and drops off very rapidly as the wires are pulled apart. The partial mutual inductance between two straight, round wires can be approximated by:

where:

M = partial mutual inductance, in nH

Len = length of the two rods, in inches

s = center-to-center separation, in inches

This formidable approximation takes into account second-order effects and is often referred to as a second-order model. It can be simplified by a further approximation when the separation is small compared to the length of the rods (s << Len) as:

This is a first-order model, as it ignores some of the details of the long-range coupling between the rods. What it sacrifices in accuracy is made up for by its slight advantage in ease of use. Figure 6-8 shows the predictions for the mutual inductance between two rods, as the rods are moved farther apart, and how they compare with the predictions from a 3D field solver. We see that when the partial mutual inductance is greater than about 20% of the partial self-inductance (i.e., when mutual inductance is significant), the first-order approximation is pretty good. It is a good, practical approximation.

Figure 6-8 Partial mutual inductance between two round rods, 0.1-inch long, as their center-to-center separation increases, comparing the accurate approximation, the simplified approximation, and the result from Ansoft’s Q3D field solver.

For example, two wire bonds may each have a partial self-inductance of 2.5 nH if they are 100 mils long. If they are on a 5 mil pitch, they will have a partial mutual inductance of 1.3 nH. This means that if there were 1 A of current in one wire bond, there would be 1.3 nH × 1 Amp = 1.3 nanoWebers of field line rings around the second wire bond. The ratio of the partial mutual inductance between the two wire bonds to the partial self-inductance of either one is about 50% with this separation.

From the graph of the mutual inductance and spacing, a good rule of thumb can be identified: If the spacing between two conductor segments is farther apart than their length, their partial mutual inductance is less than 10% of the partial self-inductance of either one and can often be ignored.

This says that the coupling between two sections of an interconnect is not important if the sections are farther apart than their length. For example, two vias 20 mils long have virtually no coupling between them if they are spaced more than 20 mils apart, center to center.

The concept of partial inductance is really the fundamental basis for all aspects of inductance. All the other forms of inductance can be described in terms of partial inductance. Package and connector models are really based on partial inductances. The output result of 3D static field solvers, when they calculate inductance values, is really in partial-inductance terms. SPICE models really use partial-inductance terms.

TIP

If we can identify the performance design goals in terms of how we need to optimize each type of inductance, we can use our understanding of how the physical design will affect the partial self- and mutual inductances of a collection of conductors to optimize the physical design.

6.7 Effective, Total, or Net Inductance and Ground Bounce

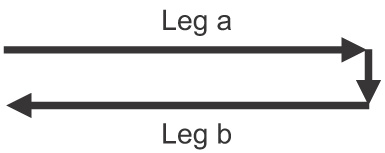

Consider a wire that is straight for some length and then loops back on itself, as shown in Figure 6-9, making a complete loop. This sort of configuration is very common for all interconnects, including signal and return paths and power paths and their “ground”-return paths. For example, it is common to have adjacent power- and ground-return wire bonds in a package. The pair could be adjacent signal and return leads in an IC package, or they could be an adjacent signal and a return plane pair in a circuit board.

When current flows in the loop, magnetic-field line rings are created from each of the two legs. If the current in the loop changes, the number of field line rings around each half of the wire would change. Likewise, there would be a voltage created across each leg that would depend on how fast the total number of field line rings around each leg was changing.

The voltage noise created across one leg of the current loop depends on how fast the total number of field line rings around the leg changes, while it is part of this complete current loop.

The total number of field line rings around one leg arises from the current in that leg (the partial self-field line rings) and the field line rings coming from the other leg (the partial mutual-field line rings). But, the field line rings from the two currents circulate around the leg in opposite directions, so the total number of field line rings around this section of the loop is the difference between the self- and mutual-field line rings around it. The total number of field line rings per Amp of current around this leg is given the special name effective inductance, total inductance, or net inductance.

TIP

Effective, net, or total inductance of a section of a loop is the total number of field line rings around just this section, per Amp of current in the loop. This includes the contribution of field line rings from all the current segments in the complete loop.

We can calculate the effective inductance of one leg based on the partial inductances of the two legs. Each of the two legs of the loop has a partial self-inductance associated with it, which we label La and Lb. There is a partial mutual inductance between the two legs, which we label Lab. We label the current in the loop, I, which is the same current in each leg but, of course, going in opposite directions.

If we could distinguish the separate sources of the field line rings around leg b, we would see that some of the field line rings come from the current in leg b and are self-field lines. Around leg b, there would be Nb = I × Lb field line rings from its own current. At the same time, some of the field line rings around leg b are mutual-field line rings and come from the current in leg a. The number of mutual-field line rings coming from leg a, surrounding leg b, is Nab = Lab × I.

What is the total number of field line rings around leg b? Since the current in leg a is moving in the opposite direction of leg b, the field line rings from leg a, around leg b, will be in the opposite direction of the field line rings from the current in leg b. When we count the total number of field line rings around leg b, we will be subtracting both sets of field line rings. The total number of field line rings around leg b is:

We call (Lb − Lab) the total, net, or effective inductance of leg b. It is the total number of field line rings around leg b, per Amp of current in the loop, including the effects of all the current segments in the entire loop. When the adjacent current is in the opposite direction, as when the two legs are part of the same loop and one leg has the return current for the other leg, the effective inductance will determine how much voltage is created across one leg when the current in the loop changes. When the second leg is the return path, we call this voltage generated across the return path ground bounce.

The ground-bounce voltage drop across the return path is:

Vgb = ground-bounce voltage

Ltotal = total inductance of just the return path

I = current in the loop

Lb = partial self-inductance of the return path leg

Lab = partial mutual inductance between the return path and the initial path

If the goal is to minimize the voltage drop in the return path (i.e., the ground-bounce voltage), there are only two approaches. First, we can do everything possible to decrease the rate of current change in the loop. This means slow down the edges, limit the number of signal paths that use the same, shared return path, and use differential signaling for the signals. Rarely do we have the luxury of affecting these terms much. However, we should always ask.

Second, we must find every way possible to decrease Ltotal. There are only two knobs to tweak to decrease the total inductance of the return path: Decrease the partial self-inductance of the leg and increase the partial mutual inductance between the two legs. Decreasing the partial self-inductance of the leg means making the return path as short and wide as possible (i.e., using planes). Increasing the mutual inductance between the return path and the initial path means doing everything possible to bring the first leg and its return path as close together as possible.

TIP

Ground bounce is the voltage between two points in the return path due to a changing current in a loop. Ground bounce is the primary cause of switching noise and EMI. It is primarily related to the total inductance of the return path and shared return current paths. To decrease ground-bounce voltage noise, there are two significant features to change: Decrease the partial self-inductance of the return path by using short lengths and wide interconnects and increase the mutual inductance of the two legs by bringing the current and its return path closer together.

Surprisingly, decreasing ground bounce on the return path requires more than just doing something to the return path. It also requires thought about the placement of the signal current path and the resulting partial mutual inductance with the return path.

We can evaluate how much the total inductance of one wire bond can be reduced by bringing an adjacent wire bond closer, using the approximations above. Suppose one wire bond carries the power current and the other carries the ground-return current. They would have equal and opposite currents. In this case, the partial mutual inductance between them will act to decrease the total inductance of one of them: Ltotal = La − Lab. The closer we bring the wires, the greater the partial mutual inductance between them and the greater the reduction in the total inductance of one of the wire bonds.

If each wire bond were 1 mil in diameter and 100 mils in length, the partial self-inductance of each would be about 2.5 nH. Using the approximation above for the partial self-inductance and the partial mutual inductance, we can estimate the net or effective inductance of one wire bond as we change the center-to-center spacing, s.

When the spacing is greater than 100 mils, the partial mutual inductance is less than 10% of the partial self-inductance. The effective inductance of one wire bond is nearly the same as its isolated partial self-inductance. But, when we bring them as close as 5 mils center-to-center pitch, the mutual inductance increases considerably, and we can reduce the effective inductance of one wire bond down to 1.3 nH. This is a reduction of more than 50%. The lower the effective inductance, the lower the voltage drop across this wire bond and the less ground-bounce voltage noise the chip will experience.

If the effective inductance of one wire bond, when the other current is far away, is 2.5 nH and there is 100 mA of current that switches in 1 nsec (typical of what goes into a transmission line), the ground-bounce voltage generated across the wire bond is Vgb = 2.5 nH × 0.1A/1 nsec = 250 mV. This is a lot of voltage noise. When the two wire bonds are routed close together, with a center pitch of 5 mils, the ground-bounce noise is reduced to Vgb = 1.3 nH × 0.1A/1 nsec = 130 mV—considerably less.

TIP

This demonstrates a very important design rule: To decrease effective inductance, bring the return current as close as possible to the signal current.

Suppose we have the opposite case: Suppose that both wires will be carrying power current. This is often the case in many IC packages because multiple leads are used to carry power and carry the ground return. If we look at the net inductance of one of the power wires and bring an adjacent power wire nearby, what happens?

In this case, both currents are in the same direction. The mutual-field line rings will be in the same direction as the self-field line rings. The mutual-field line rings from the second wire will add its field line rings to the field line rings already around the first wire. The net inductance of one of the power wires will be Ltotal = La + Lab.

If the goal is to minimize the net inductance of the power lead, our design goal, as always, is to do everything possible to decrease the partial self-inductance of the lead. However, in this case, because the field line rings from the adjacent wire are in the same direction, we must do everything possible to decrease their mutual inductance. This means spacing the wires out as much as possible.

We can estimate the net or effective inductance of one wire bond when the adjacent one carries the same current, for the two cases of current in the same direction or in opposite directions, as we pull them farther apart. This is plotted in Figure 6-10.

Figure 6-10 Total inductance of one 100-mil-long wire bond when an adjacent wire bond carries the same current, for the two cases of the currents in the same direction and in opposite directions. The wires are pulled apart, comparing the total inductances with the partial self- and mutual inductances.

As long as the two wires are farther apart than their length, the net inductance is not much different from the partial self-inductance of one. As they are brought closer together, the net inductance decreases when the currents are in opposite directions but increases when the currents are in the same direction.

TIP

A good general design rule to minimize the net inductance of either leg in the power distribution system is to keep similar parallel currents as far apart as their lengths.

In other words, if there are two adjacent wire bonds, each 100 mils long and both carrying power, they should be at least 100-mils center to center. Any closer, and their mutual inductance will increase the effective inductance of each leg and increase the switching noise on one of the wires. This is not to say that there is no benefit for parallel currents in close proximity. It’s just that their effectiveness is reduced over the maximum possible gain.

A common practice in high-power chips is double bonding—that is, using two wire bonds between the same pad on the die and the same pad on the package. The series resistance between the two pads will be decreased because of the two wires in parallel, and the equivalent inductance of the two wire bonds will be reduced compared to that when using only one wire bond. The closer the wires, the higher the mutual inductance, and the larger the effective inductance. But, since there are two in parallel, the equivalent inductance is half the total inductance of either one.

When double bonding, the wire bond loops should be created to keep the wires as far apart as possible. This is in keeping with the general principle that total inductance is decreased if we can spread out the same direction current paths. If they are 50 mils long and can be kept 5 mils apart, the partial self-inductance of either wire bond would be about 1.25 nH, and their partial mutual inductance would be about 0.5 nH. Their effective inductance would be 1.75 nH. With the two in parallel, their equivalent inductance would be 1/2 × 1.75 nH = 0.88 nH. This is reduced from the 1.25 nH expected with just one wire bond. Double bonding can, in fact, decrease the equivalent inductance between two pads.

As another example, consider the vias from a decoupling capacitor’s pads to the power- and ground-return planes below, as illustrated in Figure 6-11. Suppose the distance to the plane below is 20 mils, and the vias are 10 mils in diameter. Is there any advantage in using multiple vias in parallel from each pad of the capacitor?

Figure 6-11 Via placement for decoupling capacitor pads between Vcc and Vss planes. Top: Conventional placement. Bottom: Optimized for low total inductance and lowest voltage-collapse noise: s2 > via length, s1 < via length.

If the center-to-center spacing, s, between the vias is greater than the length of a via, 20 mils, their partial mutual inductance will be very small, and they will not interact. The net inductance of either one will be just its partial self-inductance. Having multiple vias in parallel from one pad to the plane below will reduce the equivalent inductance to the plane below inversely with the number of vias. The more vias we have in parallel, the lower the equivalent inductance. In Figure 6-11, this means s2 must be roughly at least as large as the distance to the planes, 20 mils. Likewise, if it is possible to bring vias with opposite currents closer together than their length, the effective inductance of each via will be reduced. If it is possible to place the vias with s1 less than 20 mils apart, the net inductance of each via will be reduced, the equivalent inductance from the pad to the plane below will be reduced, and the rail-collapse voltage will be reduced.

Another important advantage of multiple vias in the same pad is that the spreading inductance into the power and ground planes will be reduced due to a larger contact area into the planes. This can sometimes be a larger advantage than the reduced inductance of the vias.

TIP

Consider the following design rule for minimizing the total inductance of either path: Keep the center-to-center spacing between vias of the same current direction at least as far apart as the length of the via; keep the center-to-center spacing between vias with opposite-direction current much closer than the length of the vias.

6.8 Loop Self- and Mutual Inductance

The general definition of inductance is the number of field line rings around a conductor per Amp of current through it. In the real world, current always flows in complete loops. When we describe the total inductance of the complete current loop, we call it the loop inductance. This loop inductance is really the self-inductance of the entire current loop, or the loop self-inductance.

The loop self-inductance of a current loop is the total number of field line rings surrounding the entire loop per Amp of current in the loop. With 1 Amp of current in the loop, we start at one end of the loop, walk along the wire, and count the total number of field line rings we encounter from all the current in the loop. This includes the contribution from the current distribution of each section of the wire to every other section.

Let’s look at the loop self-inductance of the wire loop with two straight legs, as in Figure 6-9. Leg a is like a signal path, and leg b is like a return path. As we walk along leg a, counting field line rings, we see the field line rings coming from the current in leg a (the partial self-inductance of leg a), and we see the field line rings around leg a coming from the current in leg b (or the partial mutual inductance between leg a and leg b).

Moving down leg a, the total number of field line rings we count is really the total inductance of leg a. When we move down leg b and count the total number of field line rings around leg b, we count the total inductance of leg b. The combination of these two is the loop self-inductance of the entire loop:

where:

Lloop = loop self-inductance of the twin-lead loop

La = partial self-inductance of leg a

Lb = partial self-inductance of leg b

Lab = partial mutual inductance between legs a and b

This may look familiar, as it appears in many textbooks. What is often not explicitly stated and what often makes inductance confusing is that the self- and mutual inductances in this relationship are really the partial self- and mutual inductances.

The relationship shown in Equation 6-12 says that as we bring the two legs of current closer together, the loop inductance will decrease. The partial self-inductances will stay the same; it is the partial mutual inductance that increases. In this case, the larger mutual inductance between the two legs will act to decrease the total number of field line rings around each leg and to reduce the loop self-inductance.

It is sometimes stated that the loop self-inductance depends on the “area of the loop.” While this is roughly true in general, it doesn’t help feed our intuition much. As we have seen, it is not so much the area that is important as the total number of field line rings encircling each leg that is important.

For example, in Figure 6-12 we show two different current loops, each with exactly the same area. They will have different loop inductances since the partial mutual inductances are so different. The closer together we bring the legs with opposite current, the larger their partial mutual inductances and the smaller the resulting loop inductance.

Figure 6-12 Two loops with exactly the same area but very different loop inductances. Bringing the return section of the loop closer to the other leg reduces the loop inductance by increasing the partial mutual inductance.

There is a reason to think the loop inductance scales with the area of the loop. When we count the total number of magnetic-field line rings surrounding the loop, we have to note that every one of these rings passes through the center of the loop. Counting the total number of rings is really the same as integrating the magnetic-field density over the entire area of the loop.

While the area over which the integral is performed obviously scales with the area, the value of the magnetic-field density inside the loop that we integrate up strongly depends on the shape of the loop and the current distribution.

As we have seen, the underlying mechanism for decreasing loop self-inductance is the increase in the partial mutual inductance between the signal and return paths when the return path is brought closer to the other leg and the loop is made smaller.

There are three important special-case geometries that have good approximations for loop inductance: a circular loop; two long, parallel rods; and two wide planes.

For a circular loop, the loop inductance is approximated by:

where:

Lloop = loop inductance, in nH

R = radius of the loop, in inches

D = diameter of the wire making up the loop, in inches

For example, a 30-gauge wire, about 10 mils thick, that is bent in a circle with a 1-inch diameter, has a loop inductance of:

TIP

This is a good rule of thumb to remember: Hold your index finger and thumb in a circle; a loop of 30-gauge wire this size has a loop inductance of about 85 nH.

This approximation illustrates that loop inductance is not really proportional to the area of the loop nor to the circumference. It is proportional to the radius times ln (radius). The larger the circumference, the larger the partial self-inductance of each section, but also the farther away the opposite-direction currents in the loop and the lower their mutual inductance.

However, to first order, the loop inductance is roughly proportional to the radius. If the circumference is increased, the loop inductance will increase. For the 1-inch loop, the circumference is 1 inch × 3.14, or about 3.14 inches. This corresponds to a loop inductance per inch of circumference of 85 nH/ 3.14 inches ∼ 25 nH/in. As a good rule of thumb, we see again that the loop inductance per length is about 25 nH/inch for loops near 1 inch in diameter.

Figure 6-13 compares the loop inductance predicted by this approximation with the actual measured loop inductance of small copper wires. The accuracy is good to a few percent.

Figure 6-13 Comparison of the measured loop inductance of small loops made from 25-mil-thick wire with different loop radius and the predictions of the approximation. The approximation is seen to be good to a few percent.

The loop inductance of two adjacent, straight-round wires, assuming that one carries the return current of the other, is approximately:

where:

Lloop = loop inductance, in nH

Len = length of the rods, in inches

r = radius of the rods, in mils

s = center-to-center separation of the rods, in mils

For example, the loop inductance of two 1-mil-diameter wire bonds, 100 mils long and separated by 5 mils, is:

This relationship points out that the loop inductance of two parallel wires is directly proportional to the length of the wires. It scales directly with the natural log of the separation. Increase the separation and the loop inductance increases, but only slowly, as the natural log of the separation.

The loop inductance of long, straight, parallel rods is directly proportional to the length of the rods. For example, if the rods represent the conductors in a ribbon cable, with a radius of 10 mils and center-to-center spacing of 50 mils, the loop inductance for adjacent wires carrying equal and opposite current is about 16 nH for a 1-inch-long section.

In the special case where the signal and return paths have a constant cross section down their length, the loop inductance scales directly with the length, and we refer to the loop inductance per length of the interconnect. Signal and return paths in ribbon cable have a constant loop inductance per length. In the example above, the loop inductance per length of the ribbon-cable wires is about 16 nH/inch. In the case of two adjacent wire bonds, the loop inductance per length is 2.3 nH/0.1 inch, or 23 nH/inch.

As we shall see, any controlled-impedance interconnect will have a constant loop inductance per length.

6.9 The Power Distribution Network (PDN) and Loop Inductance

When we think “signal integrity,” we usually think about reflection problems and cross talk between signal nets. Though these are important problems, they represent only some of the signal-integrity problems. Another set of problems is due not to the signal paths but to the power and ground paths. We call this the power distribution network (PDN), and the design of the PDN we lump under the general heading of power integrity. Though power integrity is covered in more depth in Chapter 13, “The Power Distribution Network (PDN),” some of the relevant aspects of the role inductance plays in the PDN are introduced here.

The purpose of the PDN is to deliver a constant voltage across the power and ground pads of each chip. Depending on the device technology, this voltage difference is typically 5 v to 0.8 v. Most noise budgets will allocate no more than 5% ripple on top of this. Isn’t the regulator supposed to keep the voltage constant? If ripple is too high, why not just use a heftier regulator?

The expression “there’s many a slip twixt cup and lip” pretty much summarizes the problem. Between the regulator and the chip are a lot of interconnects in the PDN—vias, planes, package leads, and wire bonds, for example. When current going to the chip changes (e.g., when the microcode causes more or fewer gates to switch, or at clock edges, where most gates tend to switch), the changing current, passing through the impedance of the PDN interconnects, will cause a voltage drop, called either rail droop or rail collapse.

To minimize this voltage noise from the changing current, the design goal is to keep the impedance of the PDN below a target value. There will still be changing current, but if the impedance can be kept low enough, the voltage changes across this impedance can be kept below the 5% allowed ripple.

TIP

The impedance of the PDN is kept low by two design features: the addition of low-loop inductance decoupling capacitors to keep the impedance low at lower frequencies and minimized loop inductance between the decoupling capacitors and the chip’s pads to keep the impedance low at higher frequencies.

How much decoupling capacitance is really needed? We can estimate roughly how much total capacitance is needed by assuming that the decoupling capacitor provides all the charge that must flow for some time period, Δt.

During this time, the voltage across the capacitor, C, will drop as its charge is depleted by ΔQ, which has flowed through the chip. The voltage drop, ΔV, is given by:

where:

ΔV = change in voltage across the capacitor

ΔQ = charge depletion from the capacitor

C = capacitance

How much current, I, flows through the chip? Obviously this depends strongly on the specific chip and will change a lot depending on the code running through it. However, we can get a rough estimate by assuming that the power dissipation of the chip, P, is related to the voltage, V, across it, and the average current, I, through it. Given the chip’s average power dissipation, the average current through the chip is:

The total amount of decoupling needed for the chip to be able to decouple for a time, Δt, is related by:

From this relationship, the time a capacitor will decouple can be found as:

or the capacitance required to decouple for a given time can be found from:

where:

Δt = time during which the charge flows from the capacitor, in sec

0.05 = 5% voltage droop allowed

C = capacitance of the decoupling capacitor, in Farads

V = voltage of the rail, in Volts

P = power dissipation of the chip, in watts

For example, if the chip power is 1 watt, typical for a memory chip or small ASIC running at 3.3 v and with a 5% ripple allowed, the amount of total decoupling capacitance needed is about:

If the regulator cannot respond to a voltage change in less time than 10 microseconds, for example, then we need to provide at least 2 × 10 microsec = 20 microFarad capacitance for decoupling. Less than this, and the voltage droop across the capacitor will exceed the 5% allowed ripple.

Why not just use a single 20-microFarad capacitor to provide all the decoupling required? The impedance of an ideal capacitor will decrease with increasing frequency. At first glance, it would seem that if a capacitor has low enough impedance (e.g., in the 1-MHz range) where the regulator cannot respond, then it should have even lower impedance at higher frequency.

Unfortunately, in real capacitors, there is a loop associated with the connection between the terminals of the capacitor and the rest of the connections to the pads on the chip. This loop inductance, in series with the ideal capacitance of the component, causes the impedance of a real capacitor to increase with increasing frequency.

Figure 6-14 is a plot of the measured impedance of an 0603 decoupling capacitor. This is the measured loop impedance between one end of the capacitor and the other, through a plane below the component. At low frequency, the impedance decreases, exactly as it does in an ideal capacitor. However, as the frequency increases, we reach a point where the series loop inductance of the real capacitor begins to dominate the impedance. Above this frequency, called the self-resonant frequency, the impedance begins to increase. Above the self-resonant frequency, the impedance of the real capacitor is completely independent of its capacitance. It is only related to its associated loop inductance. If we want to decrease the impedance of decoupling capacitors at the higher frequency end, we need to decrease their associated loop inductance, not increase their capacitance.

Figure 6-14 Measured loop impedance of a 1 nF 0603 decoupling capacitor, with a current loop configured as shown, measured with a GigaTest Labs Probe Station.

TIP

A key feature of decoupling capacitors is that at high frequency, the impedance is solely related to their loop inductance, referred to as the equivalent series inductance (ESL). Decreasing the impedance of a decoupling capacitor at high frequency is all about decreasing the loop inductance of the complete path from the chip’s pads to the decoupling capacitor.

The measured loop impedance of six 0603 decoupling capacitors with different values is shown in Figure 6-15. Their impedance at low frequency is radically different since they have orders-of-magnitude different capacitance. However, at high frequency, their impedances are identical because they have the same mounting geometry on the test board.

Figure 6-15 Measured loop impedance of six different 0603 capacitors with capacitances varying from 10 pF to 1 μF, but all with the same mounting geometry, measured with GigaTest Labs Probe Station.

TIP

The only way of decreasing the impedance of a decoupling capacitor at high frequency is by decreasing its loop self-inductance.

The best ways of decreasing the loop inductance of a decoupling capacitor are as follows:

• Keep vias short by assigning the power and ground planes close to the surface.

• Use small-body-size capacitors.

• Use very short connections between the capacitor pads and the vias to the underlying planes.

• Use multiple capacitors in parallel.

If the loop inductance associated with one decoupling capacitor and its mounting is 2 nH and the maximum allowed inductance is 0.1 nH, then there must be at least 20 capacitors in parallel for the equivalent loop inductance to meet the requirement.

From the decoupling capacitors to the chips’ pads, the interconnect should be designed for the lowest loop inductance. In addition to short surface pads and short vias, planes are the interconnect geometry with the lowest loop inductance.

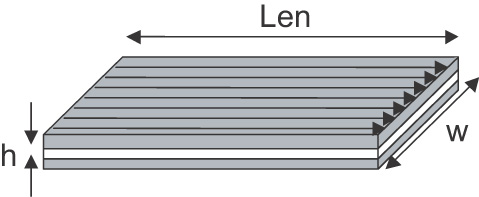

6.10 Loop Inductance per Square of Planes

The loop inductance for a current path going down one plane and back the other, as illustrated in Figure 6-16, depends on the partial self-inductance of each plane path and the partial mutual inductance between them. The wider the planes, the more spread out the current distribution, the lower the partial self-inductance of each plane, and the lower the loop inductance. The longer the planes, the larger their partial self-inductance and the larger the loop inductance. The closer we bring the planes, the larger their mutual inductance and the lower the loop inductance.

Figure 6-16 Geometrical configuration for the current flow in two planes forming a loop. The return current is in the opposite direction in the bottom plane.

For the case of wide conductors, where the width, w, is much larger than their spacing, h, or w >> h, the loop inductance between two planes is to a very good approximation given by:

where:

Lloop = loop inductance, in pH

μ0 = permeability of free space = 32 pH/mil

h = spacing between the planes, in mils

Len = length of the planes, in mils

w = width of the planes, in mils

This assumes the current flows uniformly from one edge and back to the other edge.

If the section is in the shape of a square, the length equals the width, and the ratio is always 1, independent of the length of a side. It’s startling that the loop inductance of a square section of a pair of planes that is 100 mils on a side is exactly the same as for a square section 1 inch on a side. Any square section of a pair of planes will have the same edge-to-edge loop inductance. This is why we often use the term loop inductance per square of the planes, or the shortened version inductance per square or sheet inductance of the board. It makes life more confusing, but now we know this really refers to the loop inductance between two edges of a square section of planes, when the other edges are shorted together.

For the thinnest dielectric spacing currently in volume production, 2 mils, our approximation above estimates the loop inductance per square as about Lloop = 32 pH/mil × 2 mil = 64 pH. As the dielectric thickness increases, the loop inductance per square increases. A dielectric spacing of 5 mils has a loop inductance per square of Lloop = 32 pH/mil × 5 mil = 160 pH.

As the spacing between adjacent planes increases, the partial mutual inductance will decrease, and there won’t be as many field line rings from one plane around the other to cancel out the total number of field line rings. With greater dielectric spacing, the loop inductance increases, and the rail-collapse noise will increase. This will make the PDN noise worse and will also increase the ground-bounce noise that drives common currents on external cables and causes EMI problems.

TIP

Spacing the power and ground planes as close together as possible will decrease the loop inductance in the planes, decreasing rail collapse, ground bounce in the planes, and EMI.

6.11 Loop Inductance of Planes and Via Contacts

Current doesn’t flow from one edge to another edge in planes. Between a discrete decoupling capacitor and the package leads, the connection to the planes is more like point contacts. In the above analysis, we assumed the current was flowing uniformly down the plane. However, in actual practice, the current is not uniform. If the current is restricted due to point contacts, the loop inductance will increase.

The only reason we assumed the current was uniform was because this was the only case for which we had a simple approximation to help estimate the loop inductance. When balancing accuracy versus little effort to get an answer, we chose the path of little effort. The only way to get a better estimate of the loop inductance associated between two planes with real contacts is by using a 3D field solver.

We can gain some insight into how the geometry affects the associated loop inductance between two contact points between the planes. By using a 3D field solver, we can calculate the specific current distribution between the contact points and from the specific current distributions, the resulting loop inductance.

The good news about field solvers is that the accuracy can be very good, and they can include many real-world effects for which there are no good approximations. The bad news is that we can’t generalize an answer from a field solver. It can run only one specific problem at a time.

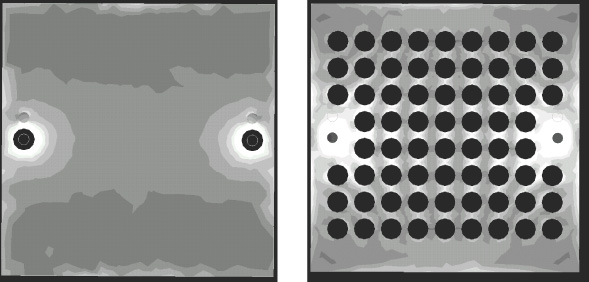

As an example of the impact of the via contacts on the loop inductance between two planes, two special cases are compared. In both cases, a 1-inch-square section of two planes, 2 mils apart, was set up. In the first case, one edge of the top plane and the adjacent edge of the bottom plane were used as the current source and sink. The far ends of the planes were shorted together.

In the second case, two small via contacts were used as the current source and sink at one end, and a similar pair of contacts shorted the planes together at the other end. The contacts were 10 mils in diameter, spaced on 25-mil centers, similar to how a pair of vias would contact the planes in an actual board.

Figure 6-17 shows the current distribution in one of the planes for each case. When the edge contact is used, the current distribution is uniform, as expected. The loop inductance between the two planes is extracted as 62 pH. The approximation above, for the same geometry, was 64 pH. We see that for this special case, the approximation is pretty good.

Figure 6-17 Current distribution in the top plane of a pair of planes with edge contact and a pair with point contacts. The lighter shade corresponds to higher current density. With edge contacts, the current distribution is uniform. With via point contacts, the current is crowded near the contact points. The higher current density creates higher inductance. Simulation with Ansoft’s Q3D field solver, courtesy of Charles Grasso.

When the current flows from one via contact, down the board to a second via contact, through the via to the bottom plane, back through the board and up through the end vias—as would be the case in a real board—the loop inductance extracted by the field solver is 252 pH. This is an increase by about a factor of four. The increase in loop inductance between the planes is due to the higher current density where the current is restricted to flow up the via. The more constricted the current flow, the higher the partial self-inductance and loop inductance. This increase in loop inductance is sometimes referred to as spreading inductance. If the contact area were increased, the current density would decrease, and the spreading inductance would decrease.

The loop inductance between the planes, even with the spreading inductance, will still scale with the plane-to-plane separation. The thinner the dielectric between the power and ground planes, the lower the sheet inductance and the lower the spreading inductance. Likewise, when the dielectric spacing between planes is large, the spreading inductance is large.

TIP

The spreading inductance associated with the via contact points to a pair of power and ground planes is usually larger than the associated sheet loop inductance and must be taken into account to accurately estimate the loop inductance of the planes.

When many pairs of vias contribute current to the planes connecting many capacitors and many package leads, closely spaced planes will minimize the voltage drop from all the simultaneous dI/dts.

The loop inductance in the planes associated with the decoupling capacitor is dominated by the spreading inductance, not by the distance between the chip and the capacitor. To a first order, the total loop inductance of the decoupling capacitor is only weakly dependent on its proximity to the chip. However, the closer the capacitor is to the chip, the more the high-frequency power and return currents will be confined to the proximity of the chip and the lower the ground-bounce voltage will be on the return plane.

TIP

By keeping decoupling capacitors close to the high-power chips, the high-frequency currents in the return plane can be localized to the chip and kept away from I/O regions of the board. This will minimize the ground-bounce voltage noise that might drive common currents on external cables and contribute to EMI.

6.12 Loop Inductance of Planes with a Field of Clearance Holes

A field solver is a useful tool for exploring the impact of a field of via clearance holes on the loop inductance between two planes. Arrays of vias occur all the time. They happen under BGA packages, under connectors, and in very high-density regions of the board.

Often, there will be clearance holes in the power and ground planes of the via field. What impact will the holes have on the loop inductance of the planes? To a first order, we would expect the inductance to increase. But by how much? We often hear that an array of clearance holes under a package—the Swiss cheese effect—will dramatically increase the inductance of the planes. The only way to know by how much is to put in the numbers—that is, use a field solver.

Two identical pairs of planes were created, each 0.25 inch on a side and separated by 2 mils. Two via contacts were connected to each end of the planes. At one end, the vias were shorted together. At the other end, current was injected in one via and taken out from the other. This simulates one end connected to a decoupling capacitor and the other connected to the power and ground leads of a package through vias to the top surface.

In one pair of planes, a field of clearance holes was created in each plane. Each hole was 20 mils in diameter on 25 mil centers. This is an open area of about 50%. For each of the two cases, the current distribution was calculated and the loop inductance extracted with a 3D static field solver. Figure 6-18 shows the current distribution with and without the field of holes. The clearance holes constrict the current to the narrow channels between the holes, so we would expect to see the loop inductance increase.

Figure 6-18 Current distribution on closely spaced planes with contact via points with and without a field of clearance holes. The lighter colors correspond to higher current densities. The holes cause the current to constrict, increasing the loop inductance. Simulated with Ansoft’s Q3D field solver, courtesy of Charles Grasso.

The field solver calculates a loop inductance of 192 pH with no holes and 243 pH with this high density of holes. This is an increase of about 25% in loop inductance for an open area of 50%. We see that holes do increase the loop inductance of planes but not nearly as dramatically as we might have expected. To minimize the impact from the holes, it is important to make the holes as small as possible. Of course, bringing the planes closer together will also decrease the loop inductance of the planes, with or without clearance holes.

It is important to note that while a field of clearance holes in the power and ground planes will increase the loop inductance, the loop inductance can be kept well below a factor of two increase. It is not nearly as much of a disaster as commonly believed.

TIP

The optimum power and ground interconnects, for lowest loop inductance, are planes as wide as possible and as closely spaced as possible. When we use a very thin dielectric between the planes, we reduce the loop inductance between the bulk decoupling capacitors and the chip’s pads. This will decrease the rail collapse and EMI.

Both rail collapse and EMI will get worse as rise times decrease. As we move into the future of higher and higher clock frequencies, thin dielectrics in the power distribution network will play an increasingly important role.

6.13 Loop Mutual Inductance

If there are two independent current loops, there will be a mutual inductance between them. The loop mutual inductance is the number of field line rings from the current in one loop that completely surrounds the current of the second loop per Amp of current in the first loop.

When current in one loop changes, it will change the number of field line rings around the second current loop and induce noise in the second current loop. The amount of noise created is:

where:

Vnoise = voltage noise induced on one loop

Lm = loop mutual inductance between the two rings

dI/dt = how fast the current in the second loop changes

The noise in the quiet loop will arise only when there is a dI/dt in the active loop, which is only during the switching transitions. This is why this sort of noise is often called switching noise, simultaneous switching noise (SSN), or delta I noise.

TIP

The most important way of reducing switching noise is reducing the mutual inductance between the signal- and return-path loops. This can be accomplished by moving the loops farther apart from each other. Since the mutual inductance between two loops can never be greater than the self-inductance of the smallest loop, another way of decreasing the loop mutual inductance is to decrease the loop self-inductance of both loops.

Loop mutual inductance also contributes to the cross talk between two uniform transmission lines and is discussed in Chapter 11, “Differential Pairs and Differential Impedance.”

6.14 Equivalent Inductance of Multiple Inductors

So far, we have been considering just the partial inductance associated with a single interconnect element that has two terminals, one on either end, and then the resulting loop inductance consisting of the two elements in series. For two separate interconnect elements, there are two connection topologies: end to end (in series) or with each end together (in parallel). These two circuit configurations are illustrated in Figure 6-19.

Figure 6-19 Circuit topologies for combining partial inductors in series (top) and in parallel (middle) into an equivalent inductance (bottom).

In either configuration, the resulting combination has two terminals, and there is an equivalent inductance for the combination. We are used to thinking about the equivalent inductance of a series combination of two inductors simply as the sum of each individual partial self-inductance. But what about the impact from their mutual inductance?

The inclusion of the mutual inductance between the interconnect elements makes the equivalent inductance a bit more complicated. We first must evaluate the total inductance of each element from its self-inductance and the contribution of mutual inductance from the other element. Then we combine total inductances either in series or in parallel.

Since the currents in each element are in the same direction, the direction of circulation of all the magnetic-field line rings is in the same direction, and the mutual partial inductances add to the partial self-inductances. In each case, the total inductances are larger than the partial self-inductances, and the equivalent circuit inductances are larger including the mutual inductances than not including them.

For the series combination of two partial inductances, the resulting equivalent partial self-inductance of the series combination is:

The equivalent partial self-inductance when the elements are connected in parallel is given by:

where:

Lseries = equivalent partial self-inductance of the series combination

Lparallel = equivalent partial self-inductance of the parallel combination

L1 = partial self-inductance of one element

L2 = partial self-inductance of the other element

L12 = partial mutual-inductance between the two elements

When the partial mutual inductance is zero, and the partial self-inductances are the same, both of these models reduce to the familiar expressions of the series and parallel combination. The series combination is just twice the self-inductance of one of them, and the equivalent parallel inductance is just half the partial self-inductance of either of them.

In the special case when the partial self-inductance of the two inductors is the same, the series combination of the two inductors is just twice the sum of the self- and mutual inductance. For the parallel combination, when the two partial self-inductances are equal, the equivalent inductance is:

where:

Lparallel = equivalent partial self-inductance of the parallel combination

L = partial self-inductance of either element

M = partial mutual inductance of either element

This says that if the goal is to reduce the equivalent inductance of two current paths in parallel, we do get a reduction, as long as the mutual inductance between the elements is kept small.

6.15 Summary of Inductance