Logic gates

8.1 Logic gates

Digital electronic logic gates are relatively cheap and readily available as integrated circuits. Such gates find a wide range of applications. For example, they might be used to determine when an input signal control system is to be allowed to give an output, as in an alarm system. Such logic gates are essentially just switching devices and this section considers the basics of such devices.

8.1.1 Switching circuits

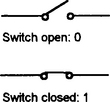

Consider a simple on-off switch (Figure 8.1). If we denote a closed contact by a 1 and an open contact by a 0 then the switch has just two possible states: 1 or 0.

Suppose we have two switches a and b in series. Each switch has two possible states, 0 and 1. Figure 8.2 shows the various possibilities for switches. In (a) both switches are open, in (b) a is open and b is closed, in (c) a is closed and b is open and in (d) a and b are both closed. With (a) the effect of both switches being open is the same as would be obtained by a single open switch; (b) and (c) likewise are equivalent to a single open switch but (d) is equivalent to a single closed switch. Thus we can say that the two elements are equivalent to 0 for (a), (b) and (c) but 1 for (d). In tabular form we can represent the state of the circuit by Table 8.1:Such a table is known as a truth table. If a AND b are 1 then the result is 1. Such an arrangement is known as an AND gate since both a and b have to be 1 for the output to be 1.

Consider two switches in parallel. Figure 8.3 shows the various possibilities for switches. In (a) both switches are open, in (b) a is open and b is closed, in (c) a is closed and b is open and in (d) a and b are both closed. With (a) the effect of both switches being open is the same as would be obtained by a single open switch; (b), (c) and (d) are equivalent to a single closed switch. Thus we can say that the two elements are equivalent to 0 for (a), and 1 for (b), (c) and (d). In tabular form we can represent the state of the circuit by the truth table (Table 8.2):Such an arrangement is known as an OR gate since if a or b is 1 then the result is 1.

Another possible form of switch circuit is where two switches are connected together so that the closing of one switch results in the opening of the other. Figure 8.4(a) illustrates the switch action with (b) showing the upper switch open when the lower switch is closed and (c) the upper switch closed when the lower switch is open. The lower switch is said to give the complement of the upper switch. Table 8.3 is the truth table:Such an arrangement constitutes a NOT switching circuit, since if one switch is 1 then the other switch is not 1.

Logic gates

With a mechanical switch we can represent the two logical states of 0 or 1 as the switch being open and closed. With electronic switches, 0 is taken to be a low voltage level and 1 a high voltage level for what is called positive logic, although the opposite convention (negative logic) can be used with 0 being represented by a high voltage level and 1 by a low voltage level. The 0 and the 1 do not represent actual numbers but the state of the voltage or current. The term logic level is often used with the voltage being said to be at logic level 0 or logic level 1.

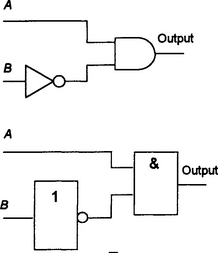

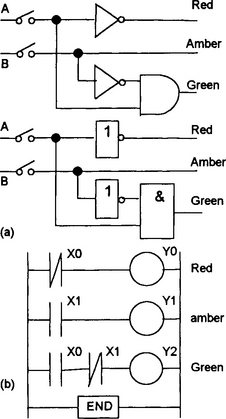

The basic building blocks of digital electronic circuits are called logic gates. A logic gate is an electronic block which has one or more inputs and an output. The output can be either high or low depending on the digital levels at the input terminals. The following sections take a look at the logic gates: AND, OR, INVERT/NOT, NAND, NOR and XOR. Different sets of standard circuit symbols have been developed in Britain, Europe and the United States; an international standard (IEEE/ANSI) has, however, been developed based on squares. In this text, both the IEEE/ANSI form and the older United States form are shown.

The AND gate gives an output 1 when both input A and input B are 1. Figure 8.5 shows the symbol, the associated truth table being given in Table 8.4

The OR gate gives an output 1 when either input A or input B is 1. Figure 8.6 shows the symbol and Table 8.5 the truth table.

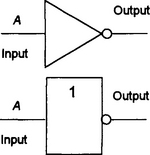

The INVERT or NOT gate has a single input and gives a 1 output when the input is 0. The gate inverts the input, giving a 1 when the input is 0 and a 0 when the input is 1. Figure 8.7 shows the gate symbol and Table 8.6 gives the truth table.

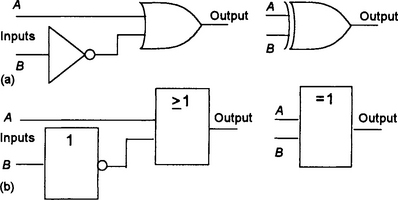

This gate (Figure 8.8) is logically equivalent to a NOT gate in series with an AND gate, NAND standing for NotAND. The symbol for the gate is the AND symbol followed by a small circle, the small circle being used to indicate negation. The gate has the truth table shown in Table 8.7. There is a 1 output when A and B are both not 1, i.e. are both 0.

This gate (Figure 8.9) is logically equivalent to a NOT gate in series with an OR gate. It is represented by the OR gate symbol followed by a small circle to indicate negation. Table 8.8 gives the truth table, there being a 1 output when neither A nor B is 1.

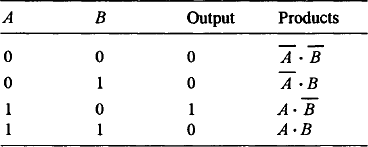

The OR gate gives an output 1 when either input A or input B is 1 or both A and B are 1. The EXCLUSIVE OR gate gives an output 1 when either input A or input B is 1 but not when both are. Figure 8.10 shows the gate symbol and Table 8.9 the truth table.

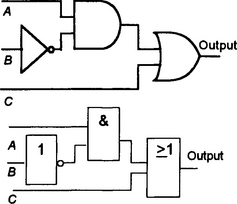

By combining gates it is possible to generate other switching operations. This is illustrated in the following example and discussed later in this chapter.

8.2 Boolean algebra

In this section we look at how we can develop algebraic notation and rules to describe and manipulate logic gate arrangements.

Notation

For the AND operation, i.e. the series connections of switches a and b, a is considered to be multiplied by b. Generally • is used for the multiplication symbol. From truth Table 8.4 we thus have the rules:

For the OR operation, i.e. the parallel connection of switches a and b, a is considered to be added to b. From truth Table 8.5 we have the rules:

For the NOT operation, i.e. the complement with the switches, we use a bar over a symbol to indicate NOT. Thus truth Table 8.6 gives the rules:

Boolean algebra

The binary digits 1 and 0 are the Boolean variables and, together with the operations ⋅, + and the complement, form what is known as Boolean algebra. By constructing the appropriate truth tables the following laws can be derived:

• Anything ORed with itself is equal to itself

See Table 8.10.

• Anything ANDed with itself is equal to itself

See Table 8.11.

• Input sequence for OR and AND

It does not matter in which order we take the inputs for OR and AND gates, the output is the same. This is illustrated by Table 8.12 for OR.

As Table 8.13(a) indicates:

Table 8.13(a)

As Table 8.13(b) indicates.

Table 8.13(b)

Anything ORed with its own negative is 1. See Table 8.14.

Table 8.14

Anything ANDed with its own negative is 0. See Table 8.15.

Table 8.15

Anything ORed with a 0 is equal to itself, anything ORed with a 1 is equal to 1. See Table 8.16.

Table 8.16

| a | a+0 | a+1 |

| 0 | 0 | 1 |

| 1 | 1 | 1 |

Anything ANDed with a 0 is equal to 0, any thing ANDed with a 1 is equal to itself. See Table 8.17.

Table 8.17

| a | a·0 | a·1 |

| 0 | 0 | 0 |

| 1 | 0 | 1 |

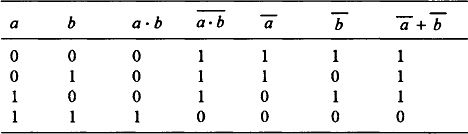

De Morgan laws:

• The complement of the outcome of switches a and b in parallel, i.e. an OR situation, is the same as when the complements of a and b are separately combined in series, i.e. the AND situation. Table 8.18 shows the validity of this.

Table 8.18

• The complement of the outcome of switches a and b in series, i.e. the AND situation, is the same as when the complements of a and b are separately considered in parallel, i.e. the OR situation. Table 8.19 shows the validity of this.

Table 8.19

Using the rules given above, complicated switching circuits can be reduced to simpler equivalent circuits.

8.3 Logic gate systems

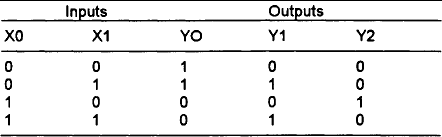

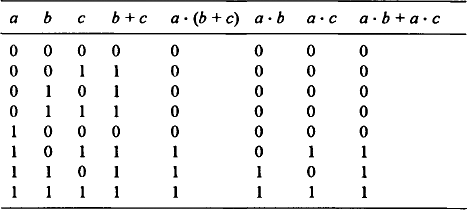

The operations ·, + and the complement can be used to write the Boolean functions for complex switching circuits, the states of such circuits being determined by developing the truth table to indicate all the various switching possibilities. Boolean algebra might then be used to simplify the switching circuits.

Combining gates

By combining logic gates it is possible to represent other Boolean functions and use of Boolean algebra can often be used to simplify the arrangement.

Boolean function generation from truth tables

Often the requirements for a system are specified in terms of a truth table and the problem then becomes one of determining how a logic gate system can be devised, using the minimum number of gates, to give that truth table. The forms to which most are minimised are an AND gate driving a single OR gate or vice versa.

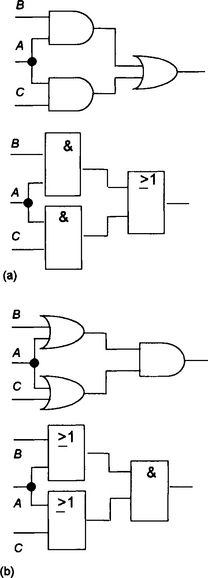

Two AND gates driving a single OR gate (Figure 8.19(a)) give, what is termed, the sum of products form:

Two OR gates driving a single AND gate (Figure 8.19(b)) give, what is termed the product of sums form:

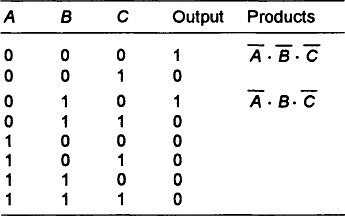

The usual procedure to find the minimum logic gate system is thus to find the sum of products or the product of sums form that fits the data. Generally the sum of products form is used. The procedure used is:

1. Consider each row of the truth table in turn that generates a 1 output and find the product that would fit a row. Only a row of a truth table that has an output of 1 need be considered, since the rows with 0 output do not contribute to the final expression. For example, suppose we have a row in a truth table of: A = 1, B = 0 and output = 1. When A is 1 and B is not 1 then the output is 1, thus the product which fits this is:

2. The overall result is the sum of all the products for the rows giving 1 output.

Karnaugh maps

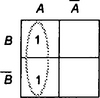

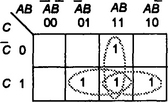

The Karnaugh map is a graphical way of representing a truth table and a method by which simplified Boolean expressions can be obtained from sums of products. The Karnaugh map is drawn as a rectangular array of cells with each cell corresponding to the output for a particular combination of inputs, i.e. a particular product value. Thus, Figure 8.25(a) shows the four-cell box corresponding to two input variables A and B, this giving four product terms. We then insert the function for each input combination, Figure 8.25(b) showing this for an AND gate and Figure 8.25(c) for an OR gate. Figure 8.26 shows how we can represent such maps with input labels A and B for 1 entries and not A and B for 0 entries.

Karnaugh maps not only pictorially represent truth tables but also can be used for minimisation. Suppose we have the following truth table:

Figure 8.27 shows the Karnaugh map for this truth table with just the 1 output shown. On the map this entry is just the cell with the coordinates A = 1, B = 0 and so gives the indicated product. The Karnaugh map enables the minimisation to be spotted visually.

As a further example, consider the following truth table:

Figure 8.28 shows the Karnaugh map for this truth table with just the 1 output shown. This has an output given by:

This can be simplified to:

Thus we have a rule for the map that: when two cells containing a 1 have a common edge then we can simplify them to just the common variable, the variable that appears in the complemented and uncomplemented form is eliminated. To help with such simplifications, we draw loops round Is in adjacent cells. Note that in looping, adjacent cells can be considered to be those in the left- and right-hand columns. Think of the map as though it is wrapped round a vertical cylinder and the left- and right-hand edges of the map are joined together. There are other rules we can develop, namely: looping a quad of adjacent 1s eliminates the two variables that appear in complemented and uncomplemented form and looping an octet of adjacent 1s eliminates the three variables that appear in both complemented and uncomplemented form.

Figure 8.29(a) shows how we can draw a Karnaugh map for three inputs and Figure 8.29(b) for four inputs. Note that the cells are labelled so horizontally adjacent cells differ by just one variable, likewise adjacent vertical cells.

Problems 8.3

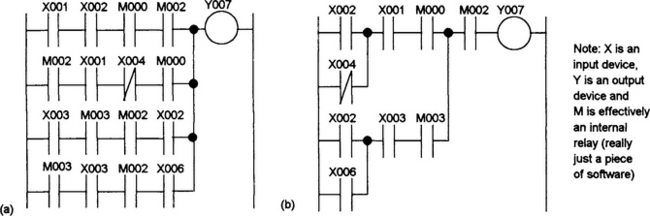

1. State a Boolean function that can be used to represent each of the switching circuits shown in Figure 8.32.

2. Give the truth tables for the switching circuits represented by the Boolean functions:

3. Determine the Boolean functions that could generate the outputs in Figure 8.33.

4. Give the truth table for the switching circuit corresponding to the Boolean function:

5. Draw switching circuits to represent the following Boolean functions:

6. Determine the Boolean equations describing the logic circuits in Figure 8.34, then simplify the equations and hence obtain simplified logic circuits.

7. Draw switching circuits to represent the Boolean functions:

8. Derive the Boolean functions for the truth tables in Table 8.21(a) and (b).

Table 8.21(a)

Table 8.21(b)

9. Determine the Boolean equations describing the logic circuits in Figure 8.35, then simplify the equations and hence obtain simplified logic circuits.

10. For the Karnaugh maps in Figure 8.36, produce the simplified Boolean expression.