Chapter 10. Microwave Oscillators

Chapter Outline

10.4 Basic Oscillator Circuits

10.5 Oscillator Design Examples

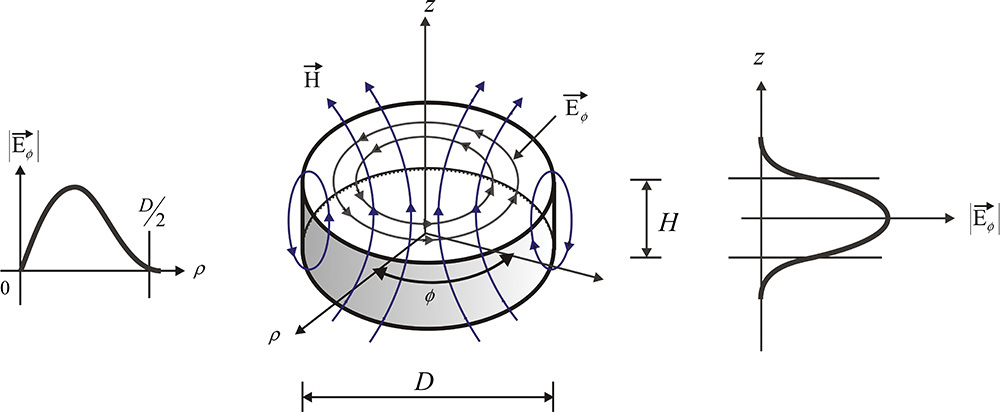

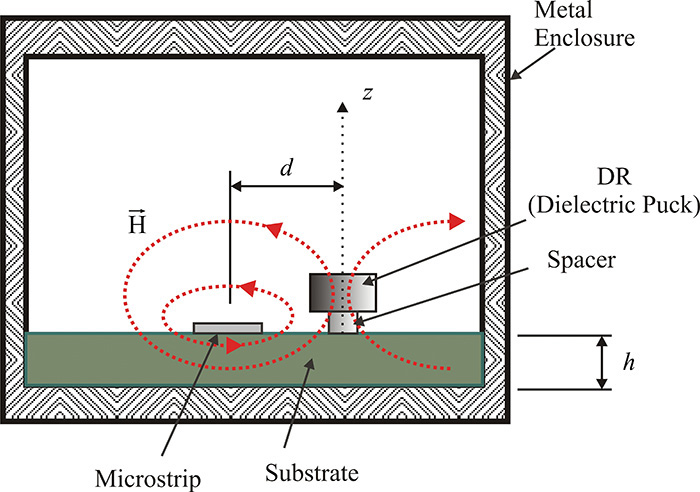

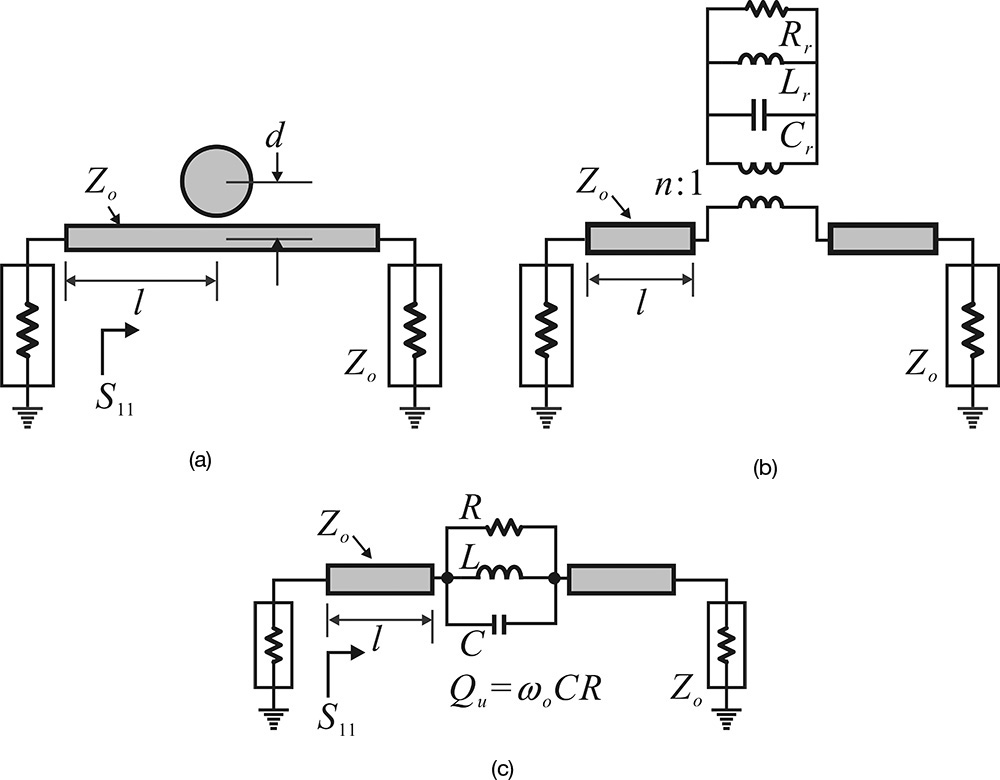

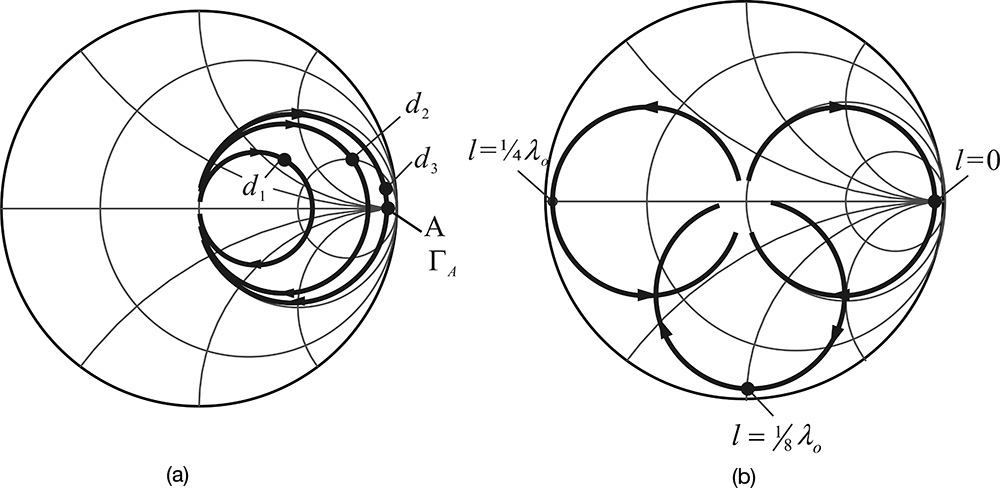

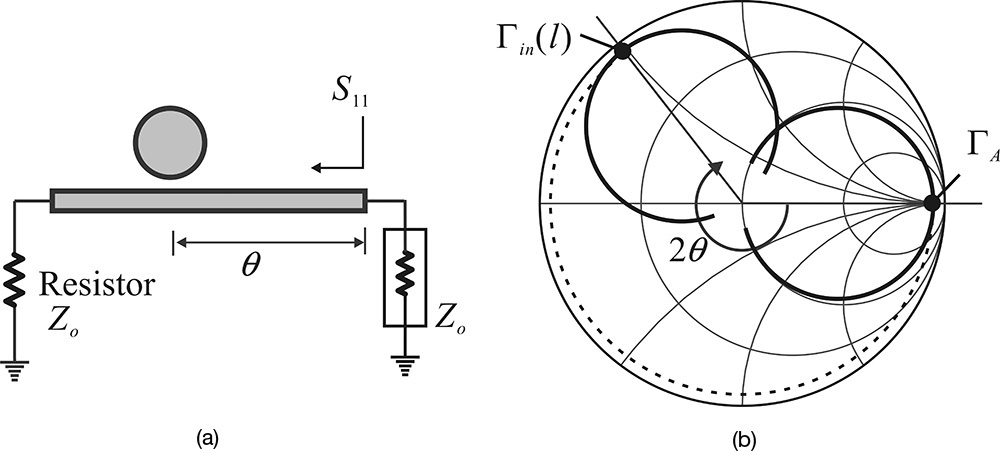

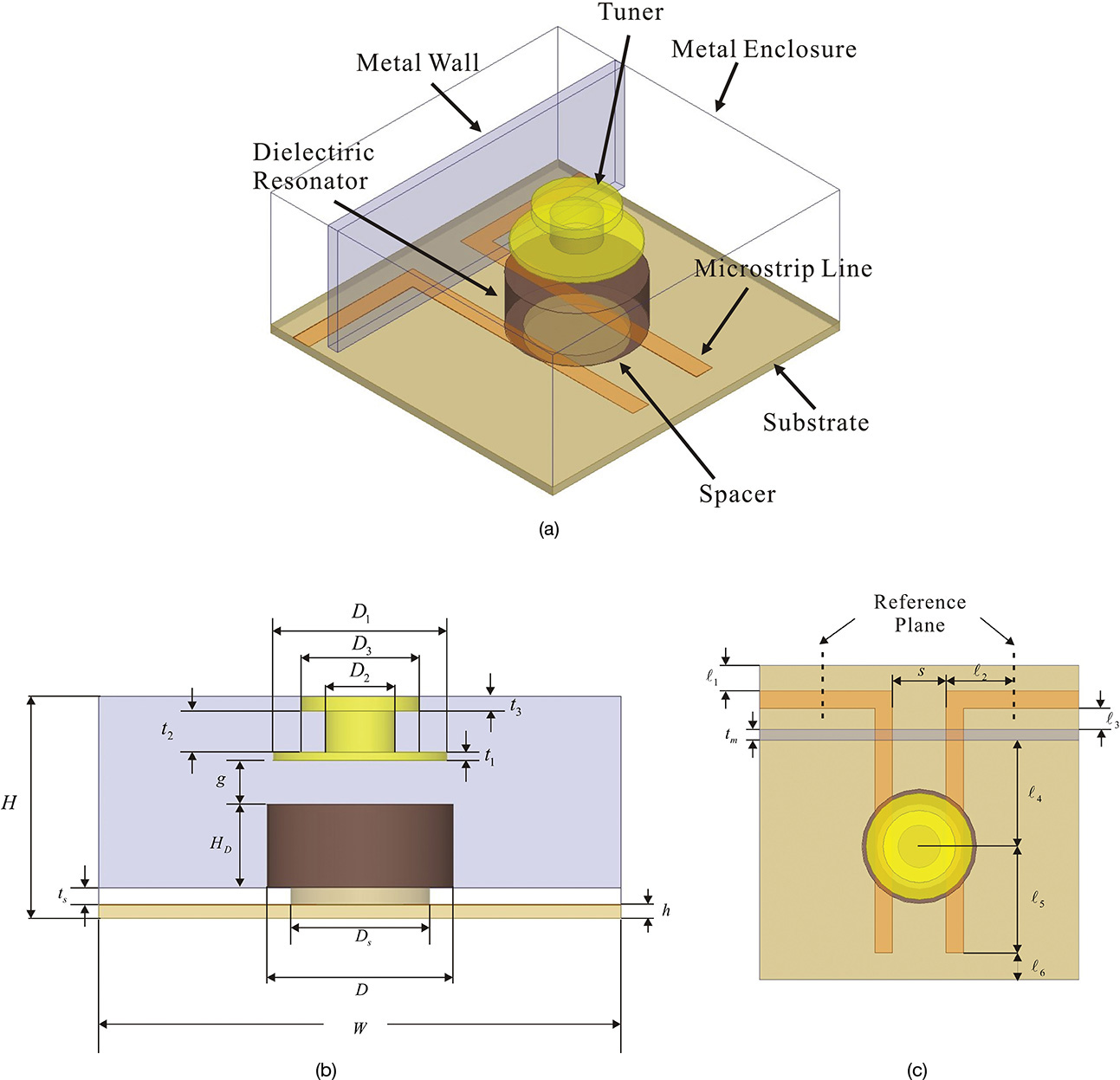

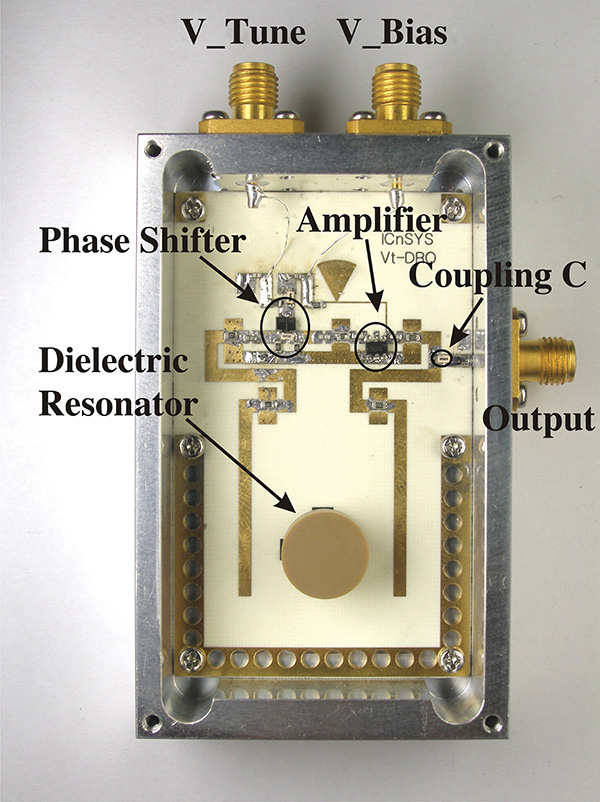

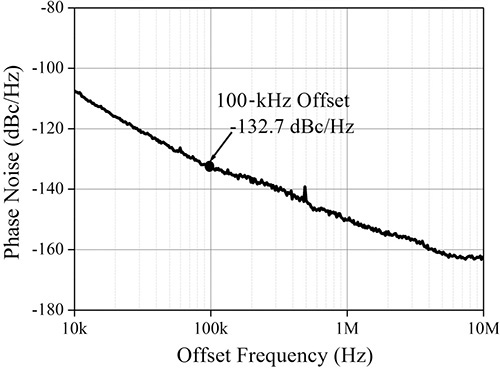

10.7 Dielectric Resonator Oscillators (DRO)

10.1 Introduction

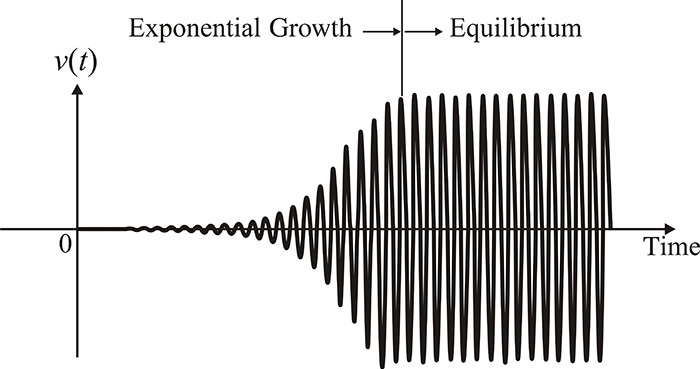

An oscillator is a circuit that generates a high-frequency sinusoidal waveform by converting DC energy delivered from a DC supply. Figure 10.1 shows the formation of an oscillation waveform in the oscillator, which can be divided into two phases: transient and equilibrium states. The amplitude of the sinusoidal waveform with a specific frequency component grows exponentially in the transient state. Then, after passing through the transient state, the waveform reaches the equilibrium state where the sinusoidal waveform with constant amplitude appears.

Thus, an oscillator design must determine whether or not the sinusoidal waveform with the desired frequency grows exponentially for a given circuit, as shown in Figure 10.1; it must then calculate the amplitude and frequency of the oscillation waveform at the equilibrium. For a given circuit, the condition necessary for a sinusoidal waveform with a specific frequency that will grow exponentially is called an oscillation start-up condition or simply oscillation condition. Since the signal level in an oscillation start-up is low, small-signal analysis can be used to examine the oscillation condition that tells whether or not the sinusoidal waveform with a specific frequency can grow exponentially. In contrast, since the signal level is not low enough at the equilibrium, large-signal analysis must be carried out. Therefore, the oscillation condition at equilibrium or simply the equilibrium condition should be described using large-signal parameters. Active devices such as transistors are generally nonlinear, and it is not possible to directly apply a linear circuit analysis concept, such as impedance or reflection coefficient, as a way to describe the oscillation at equilibrium. However, the level of harmonics in an oscillator circuit is generally low and large-signal impedance or gain can be defined by extending the concept of small-signal impedance or gain to describe the oscillation condition at equilibrium. This is explained in Appendix D.

In this chapter, we will discuss not only the oscillation start-up but also the equilibrium conditions. The large-signal impedance and reflection coefficient will be used to describe the equilibrium oscillation condition. Next, we will learn about the transformation of oscillator circuits and their design. The oscillation waveform is not an ideal sinusoidal waveform and its amplitude and phase vary randomly with time. The measurement technique and modeling of the randomly varying amplitude and phase will also be discussed in this chapter.

10.2 Oscillation Conditions

The small-signal oscillation (start-up condition) and large-signal equilibrium conditions of an oscillator circuit can be described in a number of ways. The reason for these various descriptions for the oscillation conditions is related to the ease of measuring the quantities that describe the oscillation conditions and it depends on the type of active devices that have evolved with advances in fabrication technologies. However, although the descriptions of the oscillation conditions may differ, they describe the same oscillation phenomena.

Earlier microwave oscillators were implemented using primarily one-port devices such as Gunn or IMPATT diodes. These oscillators can be decomposed into two parts, active device and load. The decomposed one-port network can easily be described using the impedance or reflection coefficient that can be measured directly. Thus, the one-port oscillation and equilibrium conditions that use the impedances or reflection coefficients are convenient for describing these one-port oscillators. As network analyzers are often used in microwave circuit measurements, the reflection coefficient is more direct and preferred for measurement than is the impedance. Thus, the one-port oscillation condition based on the reflection coefficient is a commonly used metric. The oscillation conditions in ADS are also based on the reflection coefficient. However, the impedance-based one-port oscillation conditions can still be applied to an oscillator circuit analysis after converting the reflection coefficient into the impedance.

Due to recent advances in microwave semiconductor technology, transistors such as the pHEMT or the HBT are primarily used in microwave applications instead of diodes such as the Gunn diode or the IMPATT diode. Thus, instead of the one-port oscillation condition, a technique based on an open-loop gain is more efficient. In other words, since the oscillator that uses transistors is, in general, implemented by a feedback network, the open-loop gain oscillation condition is obviously easy to apply. In this chapter, we will explain the open-loop gain conditions for the oscillator circuits that use transistors.

10.2.1 Oscillation Conditions Based on Impedance

10.2.1.1 Start-Up Conditions

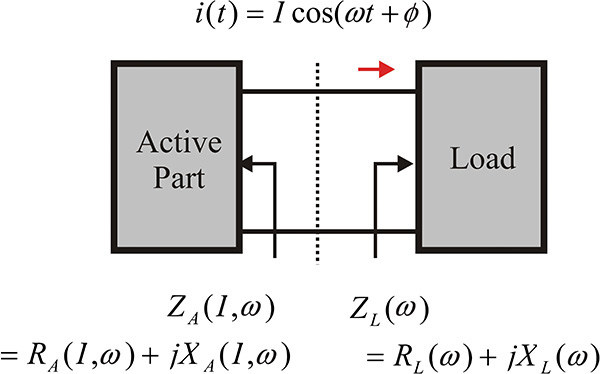

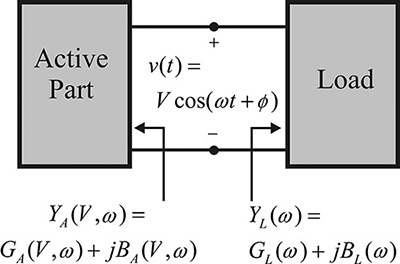

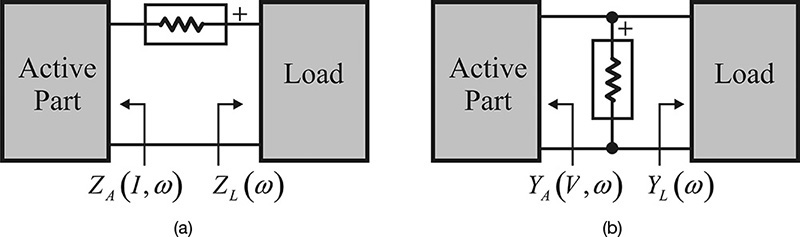

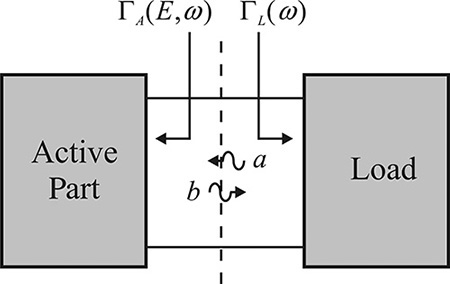

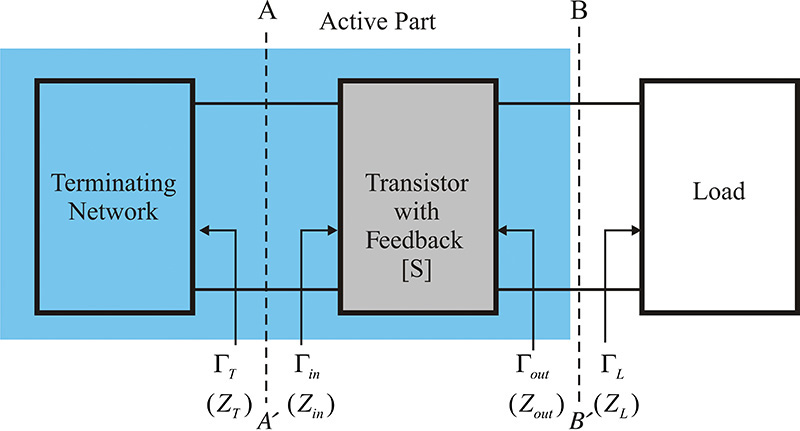

In the oscillation condition analysis based on a one-port circuit, an oscillator can be viewed as a circuit composed of a one-port load and a one-port active part, as shown in Figure 10.2.

Figure 10.2 An oscillator circuit composed of a one-port load and the active part. The oscillator circuit is considered as the series connection of the one-port load and the active part.

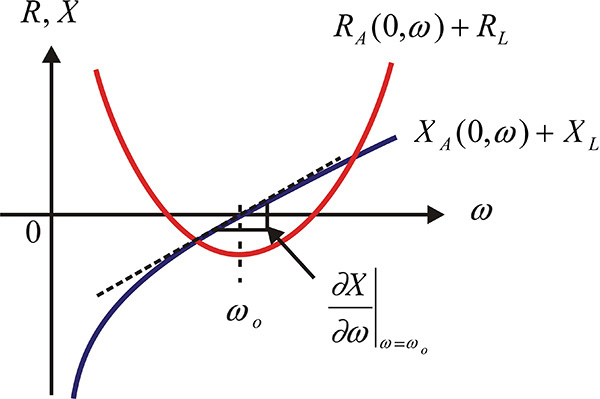

In the oscillator circuit, the active part represents the one-port network that includes an active device, such as the Gunn diode or an IMPATT diode, and has a negative resistance. In general, the impedance of the active device depends on the amplitude of the RF current I, as shown in Figure 10.2. Thus, ZA(I,ω) represents the large-signal impedance. The detailed explanation for obtaining the large-signal impedance, reflection coefficient, and gain using ADS or by measurement can be found in Appendix D. However, the load can be considered as a passive circuit that depends on frequency alone. The impedances of the active part and load can easily be measured using a network analyzer. Defining the impedance shown in Figure 10.2, the sum of the two impedances can be expressed as

Near the oscillation start-up point, the signal level is considered to be small, and since I ≅ 0, Equation (10.1) can be rewritten as Equation 10.2.

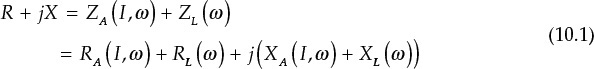

Let the frequency at which the imaginary part X (0, ω) = 0 be at ωo. Also, when R(0, ω) < 0 at ωo, the current I grows exponentially with time, which can be seen to satisfy the oscillation start-up condition. That is, in order to start the oscillation, the following conditions in Equations (10.3a) and (10.3b) must be satisfied, and their frequency-dependent variations are shown in Figure 10.3.

Figure 10.3 Series oscillation condition. The sum of the real part R < 0 and X = 0 at the oscillation frequency ωo. In addition, the slope of X with respect to frequency should be positive.

It must be noted that Equation (10.3b) can be interpreted as a series resonant condition and oscillation does not occur when the condition in that equation is not satisfied. This is the description of the oscillation condition in terms of impedance. A similar description can be obtained in terms of admittance. The load and active part in Figure 10.2 can be considered as a series connection. However, the connection can also be considered as a parallel connection, as shown in Figure 10.4. When viewed as a parallel connection, the voltage is common to both of the one-port circuits, whereas in the case of a series connection, the current is common.

Figure 10.4 Oscillator circuit composed of a one-port load and the active part. The oscillator circuit is considered as the parallel connection of the one-port load and the active part.

The admittances of the active part and load are defined as follows:

YA(V, ω) = GA(V, ω) + jBA(V, ω)

YL(ω) = GL(ω) + jBL(ω)

Denoting the sum of the admittances as Y = G + jB, then Equations (10.4a) and (10.4b),

express the similar start-up conditions that must be satisfied for the oscillation waveform to grow exponentially.

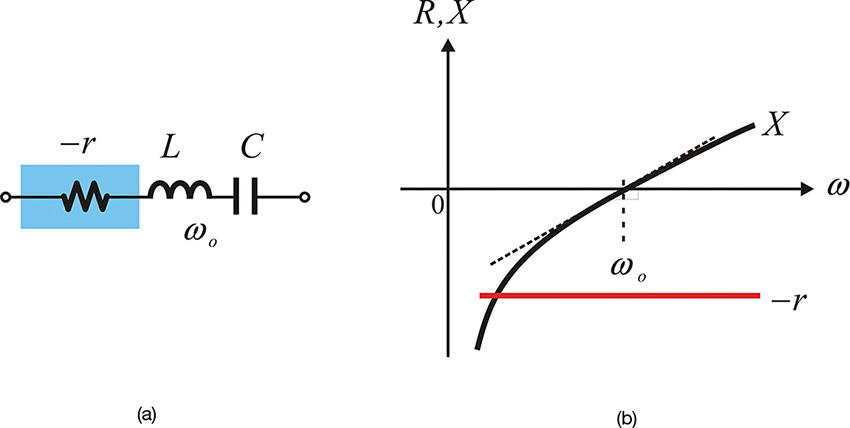

Note that the series oscillation condition in Equation (10.3) is the condition for the exponential growth of the RF current amplitude I, whereas the parallel oscillation condition in Equation (10.4) is the condition for the exponential growth of the RF voltage amplitude V when the active part and load are joined to form an oscillator. The series oscillation condition does not necessarily mean the exponential growth of V. Generally, the series oscillation condition described by the impedance does not satisfy the parallel oscillation condition described by admittance and vice versa. To investigate this, suppose that a fixed load (for example, Zo = 50-Ω load) is connected to the series resonating active part, as shown in Figure 10.5(a). Suppose that the sum of the active part and load impedances satisfies the series oscillation condition near the frequency ωo, X(ωo) = 0, -r + Zo < 0, and the slope is positive.

Figure 10.5 (a) Equivalent circuit of the active part and (b) the real and imaginary parts of the impedance for frequency

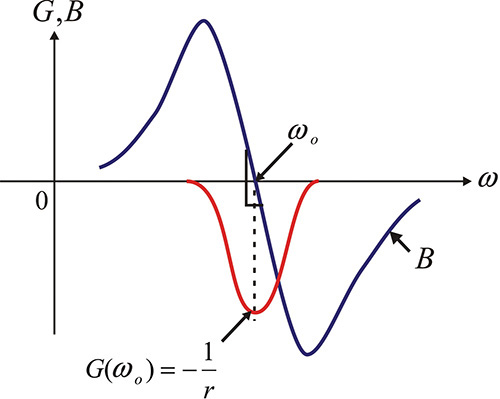

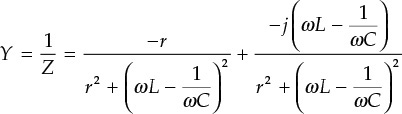

When the active part’s impedance is converted into admittance, the admittance of the active part becomes

The admittance Y can be drawn as shown in Figure 10.6.

Figure 10.6 The admittance that corresponds to the impedance of Figure 10.5(b). Note that the slope of B with respect to frequency is negative at B = 0. Also, |G| < Yo, and parallel oscillation conditions are not satisfied as a result.

The sum of the real part of Y at ωo and the load conductance Yo becomes

That is, as the total conductance is positive and the result does not satisfy the parallel oscillation condition for which the RF voltage amplitude can grow exponentially. Thus, the series oscillation condition in Equation (10.3) does not provide the parallel oscillation condition given by Equation (10.4). Similarly, when the admittance that satisfies the parallel oscillation condition is converted into impedance, the converted impedance does not satisfy the series oscillation condition.

Note that the slope of B in Figure 10.6 can be seen to be negative. Thus, even when it shows positive conductance, if the slope of B at B = 0 is negative, it must be reinvestigated to determine whether or not the series oscillation condition is satisfied. Similarly, in terms of impedance, even though the total resistance R is positive, a point where X is 0 occurs, and if the slope of X is negative, it must be reinvestigated to determine whether or not the parallel oscillation condition is satisfied. Therefore, both oscillation conditions should be simultaneously investigated to check the oscillation condition. The reason for this is that the series oscillation condition describes the condition for the RF current amplitude I to grow exponentially, which is not the exponential growth condition of the RF voltage amplitude V.

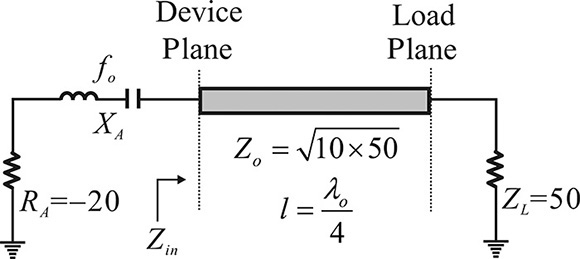

The active part of a series resonant oscillator connected to a load through a quarter-wavelength impedance inverter is shown in Figure 10E.1. To convert the load impedance of 50 Ω into 10 Ω, Zo of the impedance inverter is selected as Zo = (10 × 50)½ = 22.4 Ω. Discuss the oscillation condition at the load plane and the oscillation condition at the device plane in Figure 10E.1.

Solution

The load impedance seen from the active part is 10 Ω. A series resonant circuit is formed at the device plane and a series oscillation then occurs. Thus, the RF current amplitude with the resonance frequency will grow. Conversely, when the active part is seen from the load, the resistance at the resonance becomes Za = –(Zo)2/20 = –25 Ω, which is smaller than the load resistance. However, the impedance of the active part at the load side is given by Equation (10E.1).

The equation above means that the series connection is transformed into a parallel connection through the impedance inverter and a parallel resonance appears at the load side. Thus, since the real part of the active part is smaller than the load, it can be found to satisfy the parallel oscillation condition. Therefore, at the load side, a growth condition of the RF voltage is satisfied. In conclusion, by changing the reference plane, the series oscillation condition can be changed into the parallel oscillation condition.

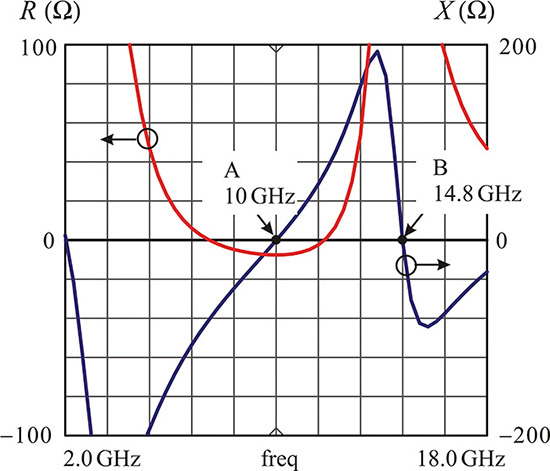

The sum of the active part and load impedance R(0,ω) + jX(0,ω) is computed in Figure 10E.2. Explain where oscillations can occur and also discuss if further investigation is required to check the possibility of oscillation.

Figure 10E.2 Plot of the sum of the active part and load impedances. The series oscillation condition is satisfied at 10 GHz but the parallel oscillation condition may be satisfied at 14.8 GHz. The parallel oscillation condition should be checked again at 14.8 GHz.

Solution

From the figure, the possible point that satisfies the series oscillation condition described by the impedance is point A (10 GHz). However, oscillation is also possible at point B (14.8 GHz), which shows a parallel resonance. When the admittance satisfying the parallel oscillation condition is converted into an impedance, a positive resistance and negative slope appear at the parallel resonant frequency. Since the oscillation condition is investigated using the sum of the impedance alone, the possibility of satisfying the parallel oscillation condition at point B is not certain. Therefore, it is necessary to plot the sum of the admittance at 14.8 GHz (point B) to check the occurrence of a parallel oscillation.

10.2.1.2 Equilibrium Conditions

In Figure 10.2, when the equilibrium is reached, the amplitude of i(t), Io, becomes constant. Applying the KVL, we obtain Equation (10.5),

and since Io ≠ 0,

Rewriting Equation (10.6),

Thus, Equations (10.7a) and (10.7b) must be satisfied at equilibrium.

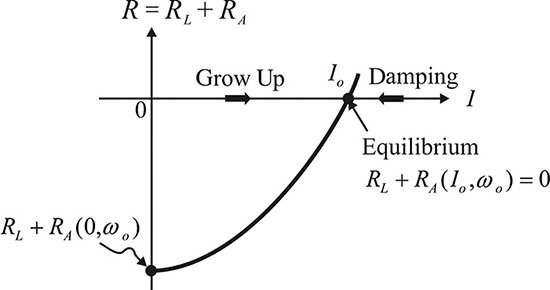

The ωo given by the oscillation start-up condition does not generally satisfy XA(Io,ω) + XL(ω) = 0. Thus, the oscillation frequency at equilibrium can be slightly different from the frequency determined by the oscillation start-up condition. In general, for a high Q circuit, the oscillation frequency primarily appears near the frequency determined by the oscillation start-up condition. Assuming that XA(I, ωo) does not vary with I, the RF current amplitude Io at equilibrium can be found by plotting the sum resistance R with respect to the RF current amplitude I. Figure 10.7 shows a plot of R(I,ω) for I. In Figure 10.7, the value of R at the small-signal I ≅ 0 is found to be negative. The RF current amplitude will increase exponentially, thereby increasing along the x-axis. Conversely, when I is larger than Io at the equilibrium point, since the value of R will be positive, the RF current amplitude decreases exponentially, thereby decreasing along the –x direction. As a result, equilibrium is attained at the point where the value of R is 0, that is, the point where the RF current amplitude is Io and thus a steady-state current amplitude appears.

Figure 10.7 Plot of the series sum resistance with respect to the current amplitude I. For small I, I will grow exponentially because R < 0. In contrast, I will decrease because R > 0 for I > Io. Eventually the equilibrium is formed at Io.

In addition, the real and imaginary parts of the large-signal admittance at equilibrium condition, like the impedance equilibrium condition, are expressed in Equations (10.8a) and (10.8b), respectively.

Similarly, the oscillation frequency at the equilibrium given by Equation (10.8b) is slightly different from the oscillation frequency determined by the oscillation start-up condition. When BA(V,ωo) is assumed to be constant for the change of V, the equilibrium can be seen to be attained at an RF voltage amplitude Vo using reasoning similar to that for the impedance equilibrium condition.

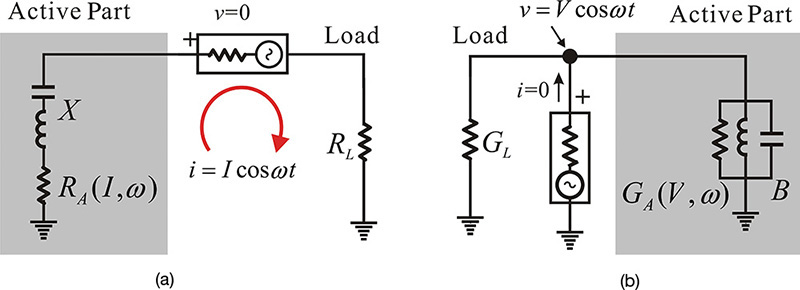

10.2.1.3 Oscillation Start-Up and Equilibrium Condition Analysis Using ADS

Since it is necessary to calculate the sum of the series impedance in order to simulate a small-signal start-up oscillation condition using ADS, a port is inserted in series between the load and the active part, as shown in Figure 10.8(a). After the one-port S-parameter analysis, the impedance of ZA + ZL at the small-signal start-up oscillation can be obtained. However, the admittance YA + YL is obtained by inserting a port in parallel between the load and the active part, as shown in Figure 10.8(b), and then performing S-parameter analysis. Thus, to investigate the possibility of oscillation using the admittance or impedance obtained through S-parameter analysis, two S-parameter analyses should be simultaneously performed, as shown in Figure 10.8.

Figure 10.8 Simulation setup for checking the small-signal oscillation condition: (a) series and (b) parallel

Next, the large-signal equilibrium condition must be calculated in ADS to determine the exact oscillation frequency and amplitude. This is accomplished by connecting a large-signal port, as shown in Figure 10.9, and performing a harmonic balance simulation. For series oscillation, the circuit is connected, as shown in Figure 10.9(a), to determine the equilibrium oscillation point. For parallel oscillation, as shown in Figure 10.9(b), the circuit is connected to determine the equilibrium oscillation point.

From Figure 10.9(a), since the sum of the impedances at the series oscillation equilibrium point is 0, the voltage across the port becomes 0. In that case, the amplitude of the current flowing through the port will only be the RF current amplitude at equilibrium. In contrast, since the sum of the admittance becomes zero at the parallel-oscillation equilibrium point, the current flowing out from the port becomes 0 and thus the RF voltage amplitude across the port will be the amplitude of the voltage at equilibrium.

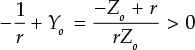

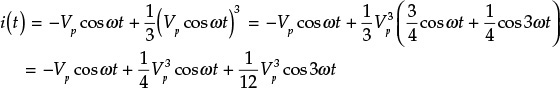

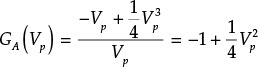

For the active device represented by the current–voltage relationship as

plot the conductance GA of the active device; then, by simulation, plot the total conductance G = GA + GL when GL = 0.2. In addition, obtain the voltage when the total conductance is 0 and verify that the voltage is the oscillation output voltage at equilibrium.

Solution

When a sinusoidal voltage is applied to the active device, the current is

Thus, the large-signal conductance becomes

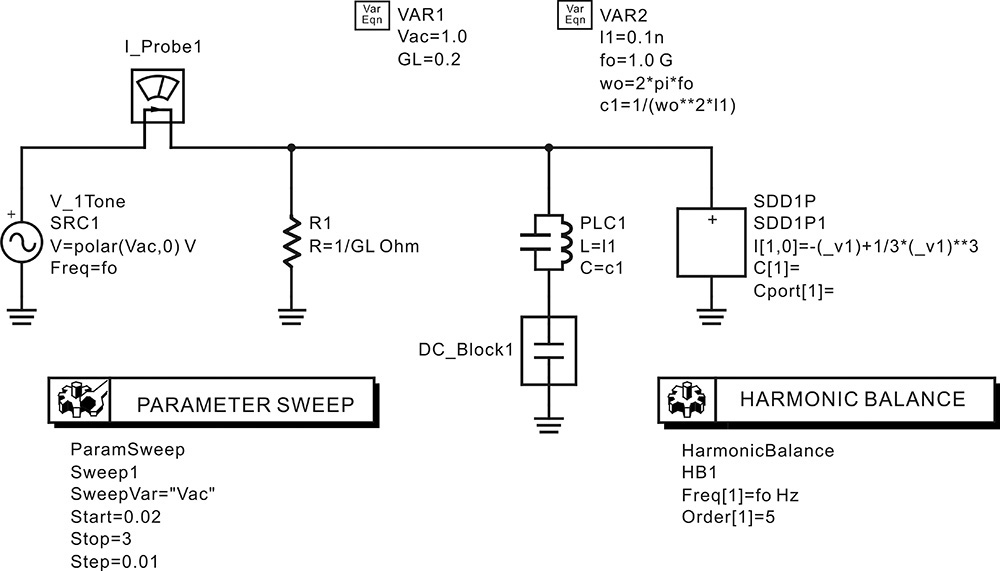

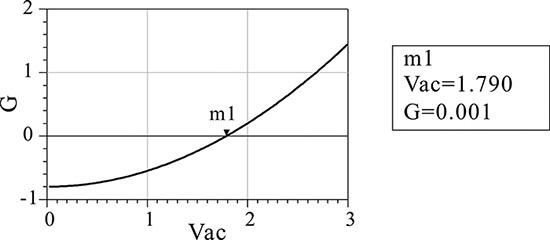

To confirm this by simulation, the given active device can be configured using an SDD (symbolically defined device), as shown in Figure 10E.3. In that figure, the parallel resonant circuit resonating at 1 GHz is connected in parallel with the SDD in order to set the oscillation frequency to 1 GHz. Since the parallel resonant circuit can cause problems at the DC operating point, a DC block is inserted in the parallel resonant circuit. After these settings and the simulation, the following equation in Measurement Expression 10E.1 is entered in the display window to plot the total conductance G, the result of which is shown in Figure 10E.4.

Figure 10E.3 Computation of the large-signal impedance for Vac. DC_Block1 is inserted so as not to disturb the DC bias.

![]() G=real(I_Probe.i[::,1])/Vac

G=real(I_Probe.i[::,1])/Vac

Measurement Expression 10E.1 Conductance G calculation

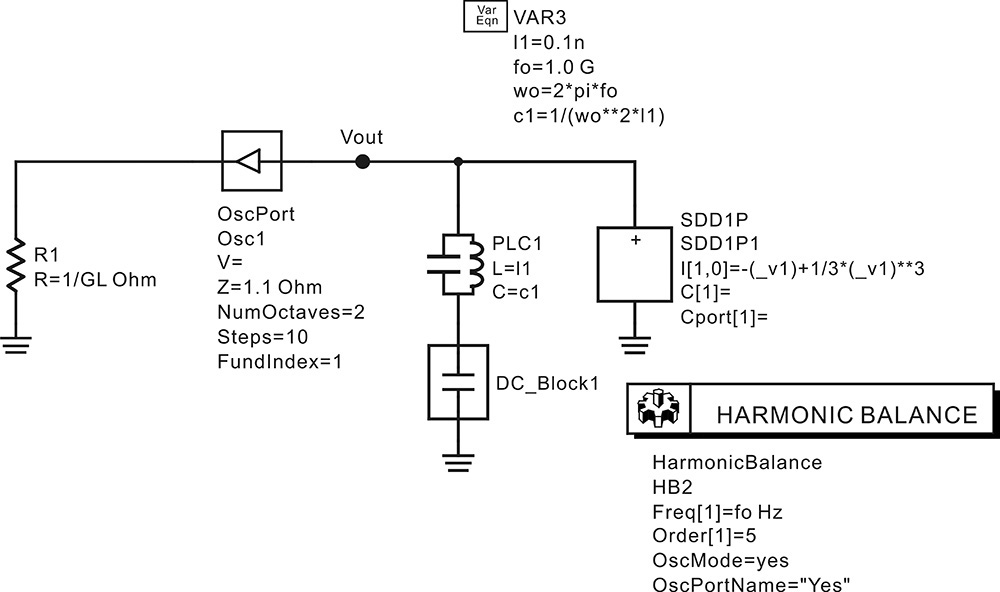

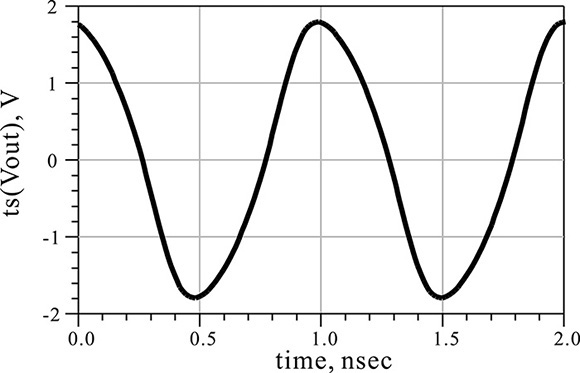

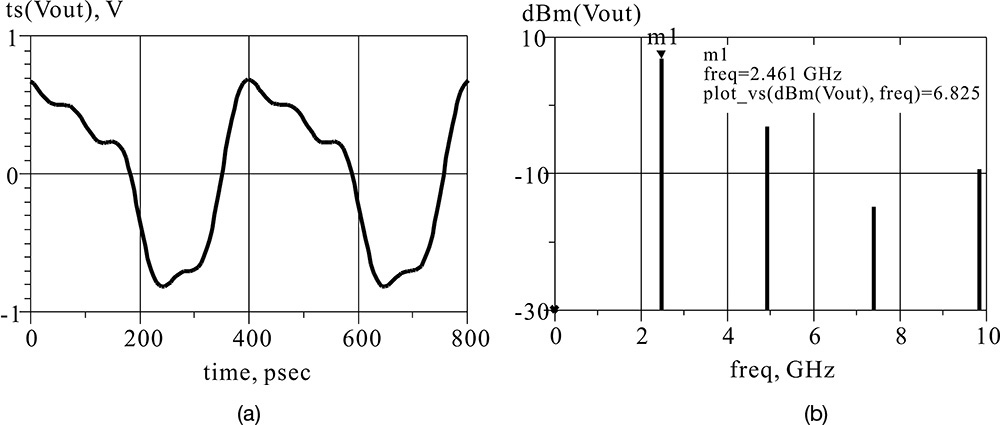

In Figure 10E.4, G is the same as the theoretically calculated conductance, which is found to be a parabola. In addition, the value of Vac where G is 0 can be seen to be approximately 1.8 V. Thus at the oscillation equilibrium, the RF voltage amplitude of 1.8 V will appear. To confirm this, OscPort, which will be explained in the next section, can be used to verify the value of Vac. The oscillation output voltage can be obtained by setting up the schematic shown in Figure 10E.5 and simulating it. The simulated waveform is shown in Figure 10E.6. The waveform in that figure shows a significant amount of distortion due to harmonics, but the amplitude of the oscillation waveform can be seen to be approximately 1.8 V.

Figure 10E.5 Simulation schematic for the oscillation waveform. OscPort in the Harmonic Balance simulator is used to obtain the large-signal oscillation waveform of the oscillator circuit.

10.2.2 Oscillation Conditions Based on the Reflection Coefficient

10.2.2.1 Start-Up and Equilibrium Conditions Based on the Reflection Coefficient

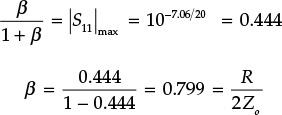

The oscillation condition based on the reflection coefficient is widely used because it is easier to measure the reflection coefficient at high frequencies compared to the measurement of impedance. The oscillation condition based on the reflection coefficient is similar to the oscillation condition based on impedance discussed earlier. In Figure 10.10, the reflection coefficients of the active part and load are defined for the same reference impedance Zo, and their one-port reflection coefficients are ΓA and ΓL, respectively.

Figure 10.10 Oscillator circuit based on the reflection coefficient. ΓA and ΓL are the reflection coefficients defined with the same reference impedance. In the case of ΓA, it is also a function of |a| = E.

When the incident voltage a = E⋅cosωt corresponding to the available power of PA = ½E2 is applied from the load, the new reflected voltage from the load a’ after a round-trip between the active part and the load is expressed in Equation (10.9).

The reflected voltage a’ becomes a new incident voltage that again makes a round-trip between the active part and the load. Thus, for exponential growth, the following start-up conditions must be satisfied, as expressed in Equations (10.10a) and (10.10b).

Here, ΓA(0,ωo) represents the small-signal reflection coefficients of the active part. Equation (10.10a) is the condition that must be satisfied for the signal to grow through the repetition of round-trips, while Equation (10.10b) is the condition requiring that the phase remain unchanged when these round-trips repeat.

In addition, for the oscillation conditions given by Equations (10.10) to be stable, the slope of Equation (10.10b) for the frequency must be negative. This is expressed in Equation (10.11).

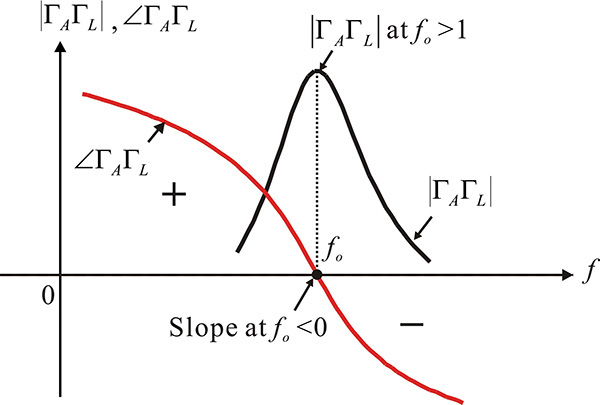

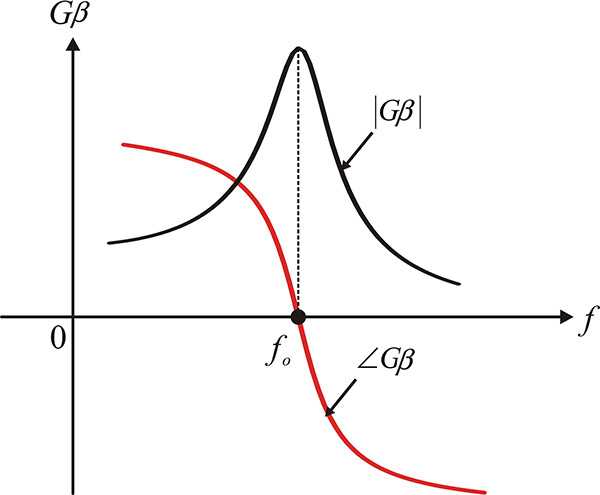

The example of the oscillation condition that satisfies Equations (10.10) and (10.11) is shown in Figure 10.11. The magnitude and phase of ΓAΓL that satisfy the oscillation condition are plotted in that figure, where it can be seen why the condition in Equation (10.11) is necessary. When the frequency is lower than the oscillation frequency, a positive phase occurs, and by repeated round-trips, the frequency increases as the phase continues to increase until it eventually approaches the oscillation frequency. In contrast, when the frequency is higher than the oscillation frequency, the phase becomes negative and, by repeated round-trips, the phase decreases continuously and eventually attains equilibrium at the frequency of oscillation. Thus, Equation (10.11) provides a stable oscillation.

Figure 10.11 Plot of small-signal ΓLΓA, which can be represented by ΓLΓA (0,w). For oscillation at fo,|ΓLΓA (0,w)| > 1 and ∠ΓLΓA (0,w) = 0 at fo should be satisfied. Also, the slope of ∠ΓLΓA (0,w) with respect to frequency should be negative for stable oscillation.

It must be noted that the oscillation conditions given by Equation (10.10) obviously guarantee oscillation. However, oscillation can also occur under other conditions and thus the conditions given by Equation (10.10) are the conditions sufficient for oscillation. Furthermore, the conditions change when the reference impedance, used to measure the reflection coefficients of the active part and load, changes. This is summarized in Appendix F.

The plot of ΓLΓA(E,ωo) for E is shown in Figure 10.12. Similar to the impedance oscillation conditions described earlier, E will grow exponentially at the small-signal because |ΓLΓA(E,ωo)| > 1 and increases along the x-axis, while E decreases when E becomes greater than Eo. Therefore, the equilibrium is achieved at Eo. That equilibrium is expressed in Equations (10.12a) and (10.12b).

Figure 10.12 Plot of ΓAΓL with respect to the available power. For small E, E will grow through repeated round-trip because |ΓLΓA (0,w)| > 1. In contrast, E will decrease because |ΓLΓA (0,w)| < 1 for E > Eo. Eventually the equilibrium is formed at Eo.

In other words, at the equilibrium point, the magnitude of the product of the reflection coefficients due to continuous round-trips is 1 and its phase is 0°.

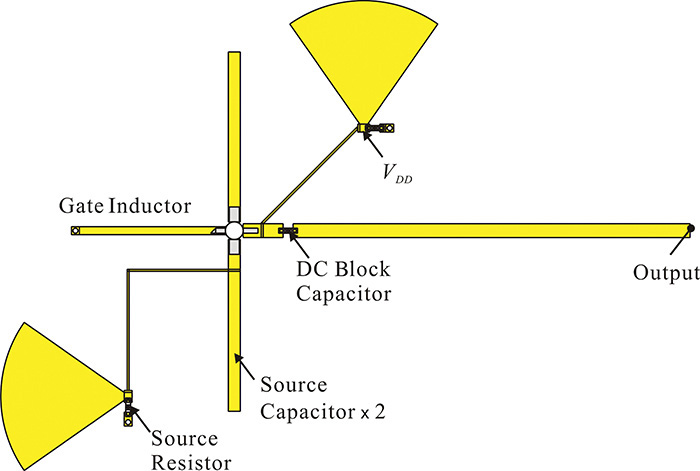

10.2.2.2 Circuit Implementation

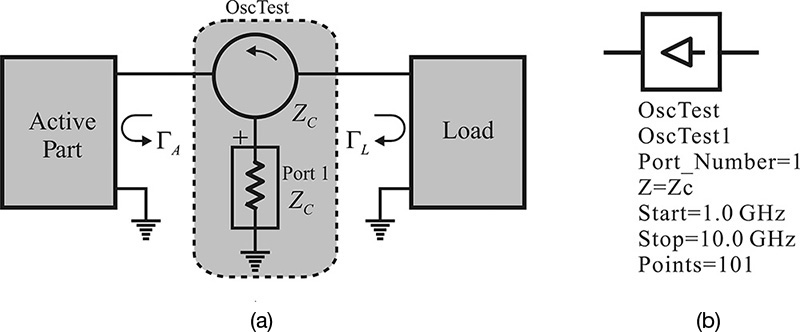

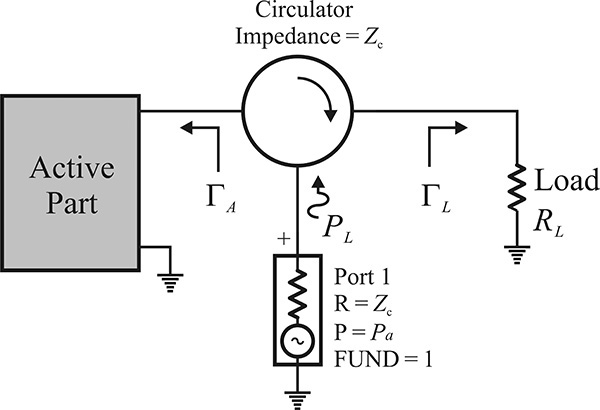

The previously described oscillation condition based on the reflection coefficient can be implemented using a circulator, as shown in Figure 10.13.

Figure 10.13 a) Measurement of ΓAΓL. The reflection coefficient seen from the port becomes ΓAΓL. (b) OscTest in ADS. Z represents the port impedance.

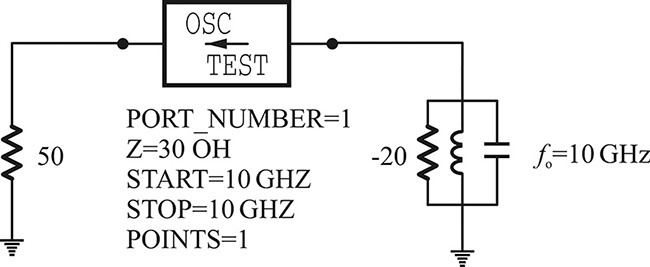

As shown in Figure 10.13(a), when the load and active part are connected to a broadband circulator with the reference impedance ZC, the reflection coefficient S11 at the port can be expressed as S11 = ΓAΓL. Note that the computed ΓAΓL depends on the reference impedance ZC of the port. The different port impedance will result in a different value for ΓAΓL. The oscillation condition based on the reflection coefficient is thus a function of the reference impedance ZC. The circulator and port in the shaded box shown in Figure 10.13(a) are already implemented as OscTest in ADS, as shown in Figure 10.13(b). The variable Z of OscTest represents ZC in Figure 10.13(a). The OscTest computes ΓAΓL for the frequency range that is specified as Start and Stop.

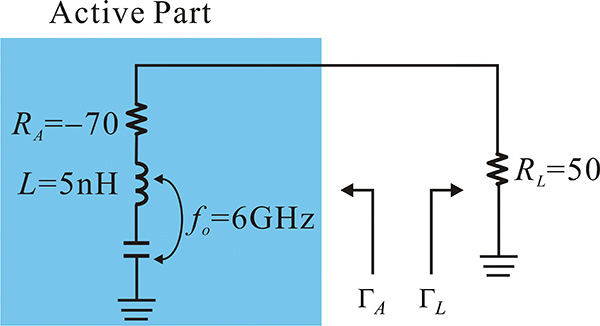

This Example considers a small-signal series oscillation circuit shown in Figure 10E.7. For the reference impedance of 100 Ω, calculate ΓAΓL and verify that this is the same as computed using OscTest whose Z is set to 100 Ω.

Solution

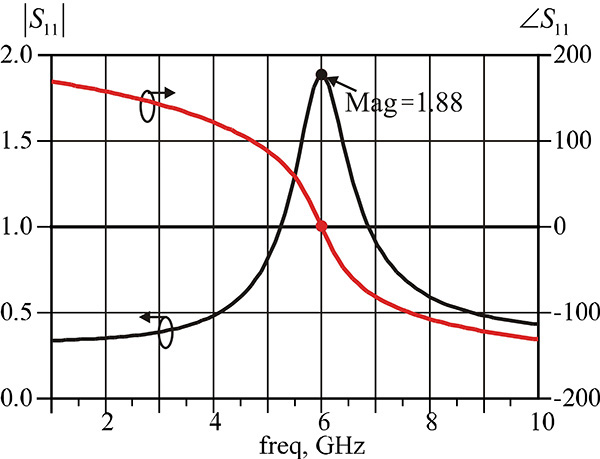

The magnitude and phase of S11 is computed using OscTest with Z = 100 Ω as shown in Figure 10E.8.

In that figure, |S11| at fo = 6 GHz is greater than 1, and the phase is 0°. In addition, the phase slope with respect to frequency can be seen to be negative. Thus, the oscillation conditions based on the reflection coefficient are satisfied.

On the other hand, calculating ΓAΓL at the oscillation frequency of 6 GHz,

which is the same as the value of mag(S11) shown in Figure 10E.8.

Notably, ΓAΓL = 0 when ZC is set at 50 Ω instead of 100 Ω, and the oscillation conditions in Equation (10.12) are not satisfied. However, this is the oscillation condition variation due to the change of ZC. The oscillator circuit in this example clearly oscillates although ΓAΓL = 0. Therefore, selecting the appropriate reference impedance makes it easy to check the oscillation condition. For more information, refer to Appendix F.

10.2.2.3 Equilibrium Based on the Reflection Coefficient

The oscillation start-up condition based on the reflection coefficient can be used to derive the large-signal equilibrium conditions. That is, irrespective of a parallel or series oscillation, the product of the reflection coefficients ΓAΓL must be 1 at equilibrium. Figure 10.14 shows the circuit measuring ΓAΓL, where the port is replaced by the large-signal port.

Figure 10.14 Computing method for a large-signal equilibrium in an oscillator. For a small signal, the oscillator circuit generates power and the port consumes the oscillation power; however, the port delivers the power to the oscillator circuit at a large-signal level. Thus, the equilibrium is formed when the dissipation power of the port is 0.

Denoting the available power from the port as Pa, the power delivered to the oscillator circuit from the port is Pa(1 – |ΓLΓA|2). Thus, when Pa is small, the delivered power becomes negative because |ΓLΓA| > 1. As a result, the port consumes the power rather than delivering it to the oscillator circuit. At equilibrium, the port is found to deliver no power to the oscillator circuit because |ΓLΓA| = 1. Therefore, the equilibrium point can be found by determining when the delivered power from the port PL becomes 0. Then, every voltage and current in the oscillator circuit at equilibrium can be obtained by calculating the currents and voltages of the oscillator circuit at the port power where delivered power from the port becomes 0.

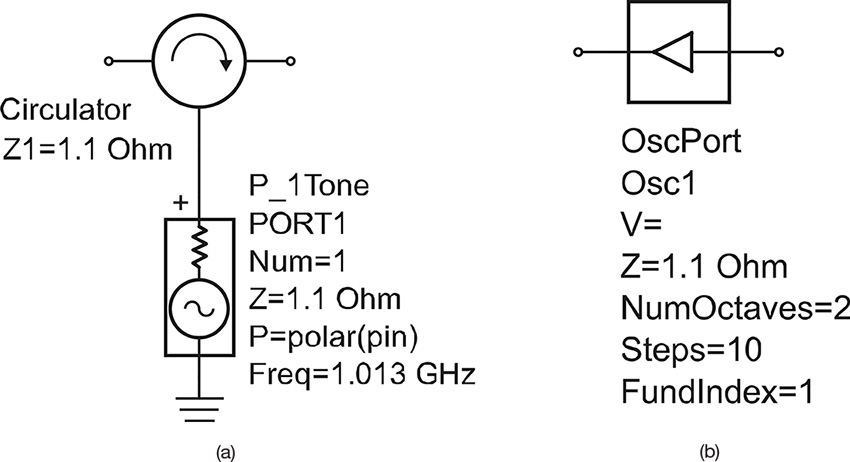

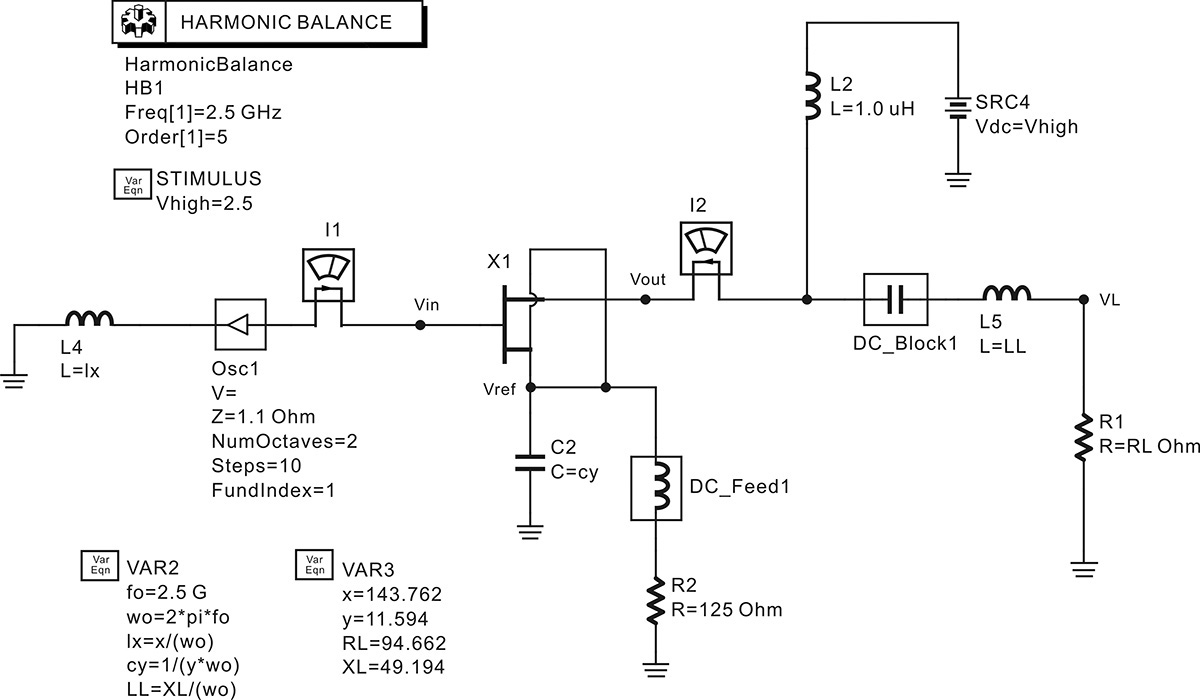

Thus, to determine the large-signal equilibrium state using the reflection coefficient, the available power and frequency of the port is altered to yield |ΓAΓL| = 1. Then, using the determined port power and the frequency at equilibrium, every current and voltage inside the oscillator circuit can be calculated; in turn, this calculation can be used to determine the waveforms of every node in the oscillator circuit at equilibrium. These operations can be performed automatically in ADS, and this is usually done using the OscPort. That is, by performing the simulation using the OscPort in conjunction with the Harmonic Balance simulator (i.e., a simulation in which the large-signal available power of the port is varied to determine the oscillation power and frequency at equilibrium), the oscillation at equilibrium can be found. The OscPort is shown in Figure 10.15(b). Figure 10.15(a) shows the concept of OscPort in ADS. The oscillation at equilibrium can be obtained by using the HB simulator together with the OscPort shown in Figure 10.15(b).

The Z of the OscPort in Figure 10.15(b) is the reference impedance of the circulator. FundIndex is the index of the estimated oscillation frequency in the HB simulator. It represents the simulation for the fundamental frequency, which in most cases is 1. Since the oscillation frequency at equilibrium differs from the estimated small-signal oscillation frequency, NumOctaves is specified to determine the frequency tuning range. When NumOctaves = 2, the oscillation frequency is sought for the frequency range that varies from 0.5 to 2 times the estimated frequency.

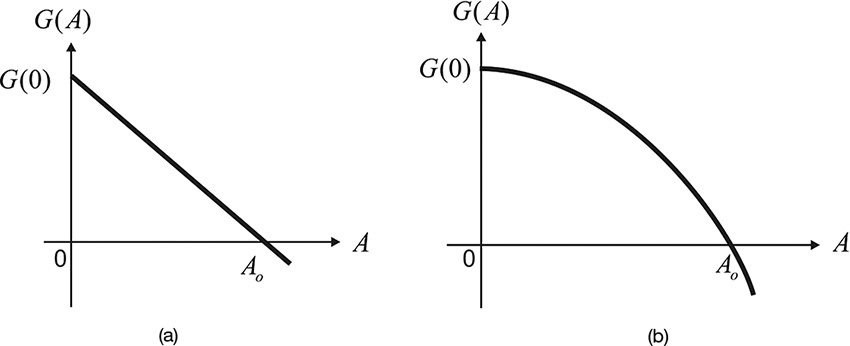

The diode admittance is denoted as YA = –G(A) + jB(A). Here, A represents the amplitude of the fundamental voltage. One diode has G(A) = g(0) – k1A and the other has G(A) = g(0) – k2A2, as shown in Figures 10E.9(a) and (b), respectively.

Figure 10E.9 G(A) with respect to voltage amplitude A: (a) linear decrease and (b) quadratic decrease

The load values giving maximum oscillation output power are known to be 1/3⋅G(0) and 1/2⋅G(0), for G(A) in Figures 10E.9(a) and (b), respectively. In Example 10.4, – G(A) = 1 – 1/4⋅A2. Thus, G(A) delivers the maximum oscillation output power to the load when the load conductance GL is equal to 0.5. Confirm this through simulation and calculate the maximum oscillation output power.

Solution

As mentioned earlier, the maximum oscillation power occurs at GL = 0.5 and since the amplitude at equilibrium must satisfy

it can be seen that A = (2)½. Thus, the maximum output power is

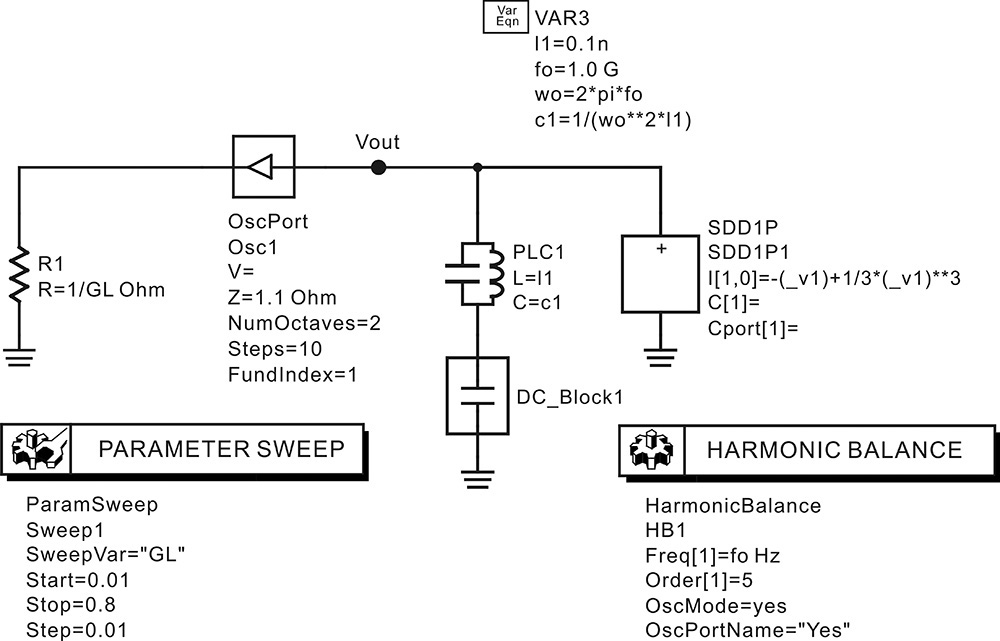

To confirm the oscillation output power for the change of GL, the harmonic balance simulation is performed using OscPort, as shown in Figure 10E.10. After simulation, the equation shown in Measurement Expression 10E.2 is entered in the display window to calculate the output power PL delivered to the load GL.

![]() PL=1/2*GL*mag(Vout[::,1])**2

PL=1/2*GL*mag(Vout[::,1])**2

Measurement Expression 10E.2 Equation for the delivered power to the load

The delivered power PL is shown in Figure 10E.11. As expected, the maximum output power is 0.5 W at GL = 0.5.

Figure 10E.11 Oscillation output power for the GL change. As expected, the maximum oscillation power 0.5 W is achieved at GL = 0.5.

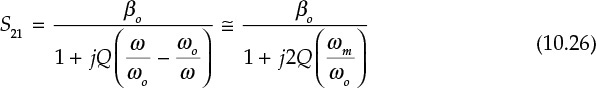

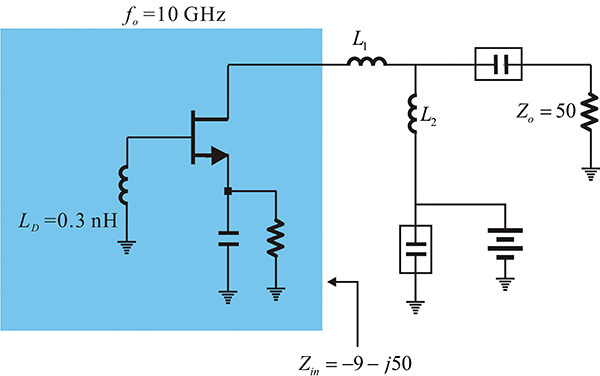

10.2.3 Start-Up and Equilibrium Conditions Based on Open-Loop Gain

The one-port oscillation condition described earlier that uses the impedance or reflection coefficient is a direct method for analyzing oscillator circuits employing diodes, but not for analyzing oscillator circuits using transistors, which can be configured as oscillators using a feedback network. In the case of oscillators that use the feedback network, the description based on the one-port oscillation conditions generally makes it difficult to understand the role of the feedback network. Instead of the reflection coefficient or the impedance used in one-port oscillation conditions, the use of an open-loop gain makes it easy to understand oscillators that employ feedback. The open-loop gain also facilitates an understanding of the maximum output power condition and phase noise of oscillators using feedback. The open-loop gain is easily obtained when the reverse gain of a transistor is small, which enables the calculation of the open-loop gain in the direction of power delivery. However, at high frequency, the reverse gain is not small and it is not easy to calculate the open-loop gain due to the bidirectional properties of transistors. Recently published papers have revisited the calculation of the open-loop gain, taking the bidirectional properties into consideration.1, 2 Thus, the open-loop gain method will be widely used in the design of oscillators employing feedback.

1. M. Randall and T. Hock, “General Oscillator Characterization Using Linear Open-Loop S-Parameters,” IEEE Transactions on Microwave Theory and Techniques 49, no. 6 (June 2001): 1094–110.

2. R. Rhea and B. Clausen, “Recent Trends in Oscillator Design,” Microwave Journal, January 28, 2004.

10.2.3.1 Start-Up and Equilibrium Conditions Based on Open-Loop Gain

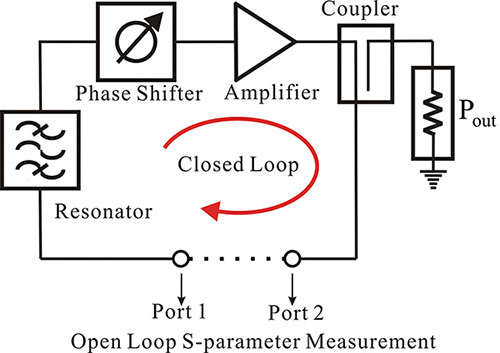

Figure 10.16 shows an oscillator configuration in which the output of the amplifier is fed back through a resonator. Here, the feedback loop is broken, which is done to obtain the open-loop gain.

Figure 10.16 Oscillator configuration with feedback network. To measure the open-loop gain, the feedback loop is broken. The test signal is applied to one port where the loop is broken and the open-loop gain is obtained by measuring the output appearing at the other port.

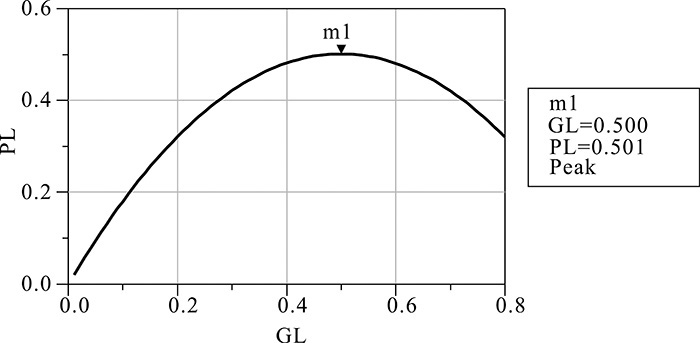

In the figure, the gain G(A,ω) of the amplifier can be considered to vary with the input signal amplitude A, and the transfer function of the resonator can generally be expressed as shown in Equation (10.13),

where βo is the transmission coefficient at the resonant frequency wo, and QL represents the loaded Q of the resonator. The open-loop gain L(A, w) is defined as Equation (10.14),

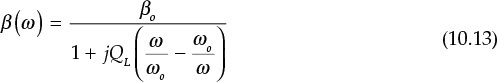

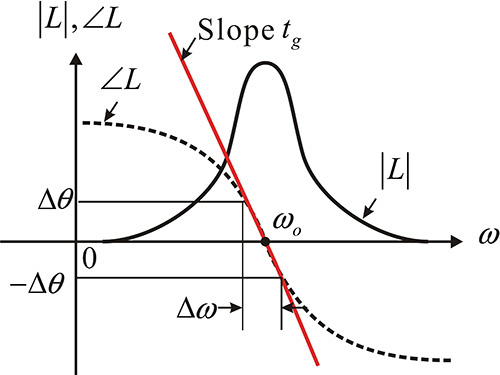

which is the output voltage per loop trip of the input signal. When a sinusoidal signal of A·cos(ωot) is applied to the input of Figure 10.16, a signal of L(A,ωo)⋅Acos(ωot) appears at the loop output. It must be noted that the output signal has the same phase as the input signal and only the amplitude varies. The output signal L(A,ωo)⋅Acos(ωot) is repeatedly applied to the input of Figure 10.16 when the loop is closed. If the loop gain |L(A,ωo)| > 1, the amplitude grows after every trip of the loop. Therefore, in order for the signal to grow as a small signal, |L(A,ωo)| > 1 at the frequency ωo with the phase 0°. Then, oscillation can be formed. This is called the Barkenhausen Criterion and can be expressed as shown in Equations (10.15a)–(10.15c).

When the conditions above are satisfied, the amplitude grows by repeated feedback and oscillation can occur. The reason Equation (10.15c) must be satisfied is that when the frequency is lower than the resonant frequency, the phase of the open loop gain in Figure 10.17 becomes positive, and thus the phase grows positively for every trip of the loop. The continuous increase in the phase represents an increase in frequency, eventually approaching the resonant frequency. In contrast, when the frequency is higher than the resonant frequency, the phase of the open loop gain in Figure 10.17 becomes negative and decreases negatively for every trip of the loop, and the continuous decrease in phase represents a decrease in frequency, and thus approaches the resonant frequency. On the other hand, when the phase response of the open-loop gain is opposite of that given by Equation (10.15c), even when there is a small phase jitter, it will be away from the resonance frequency, and oscillation will not occur. Thus, Equation (10.15c) is an important criterion in determining the occurrence of oscillation.

The typical small-signal open-loop gain L(0,ω) is shown in Figure 10.17. The frequency response characteristics shown in Figure 10.17 satisfy the conditions of Equation (10.15). Because the gain G(0,ω) is almost constant, the shape of the open-loop gain with frequency generally resembles the frequency response of the resonator given by Equation (10.13). The maximum value of the open-loop gain occurs at the resonant frequency ωo and decreases below and above the resonant frequency, as shown in Figure 10.17. Furthermore, the phase is 0° at the resonant frequency; the phase approaches 90° below the resonant frequency, while it approaches –90° above the resonance frequency.

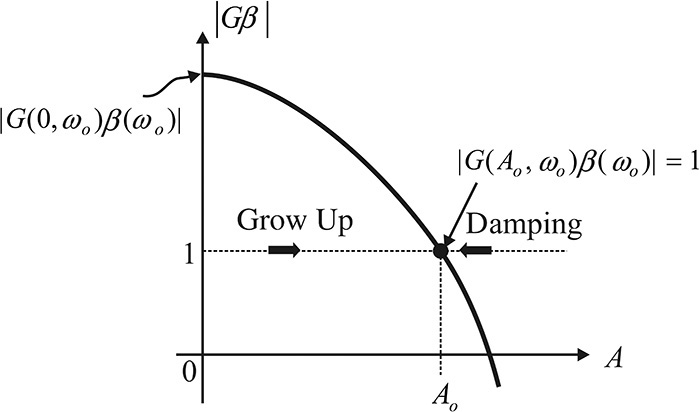

The change of the open-loop gain according to the amplitude is plotted in Figure 10.18. For small signals (A ≅ 0), as the magnitude of the open-loop gain is greater than 1, the amplitude A increases exponentially. The open-loop gain is reduced due to the increase in A. In contrast, when the amplitude is greater than the equilibrium point, the amplitude decreases because the open-loop gain is less than 1. Eventually, the amplitude A reaches Ao at the point where the open loop gain is 1. Therefore, the oscillation frequency is determined by Equation (10.16)

Figure 10.18 The open-loop gain for amplitude A. For small A, A will grow through repeated round-trips because |Gβ| > 1. In contrast, A will decrease because |Gβ| < 1 for A > Ao. Eventually, the equilibrium is formed at Ao.

and the oscillation amplitude Ao is determined by Equation (10.17).

10.2.3.2 Open-Loop Gain

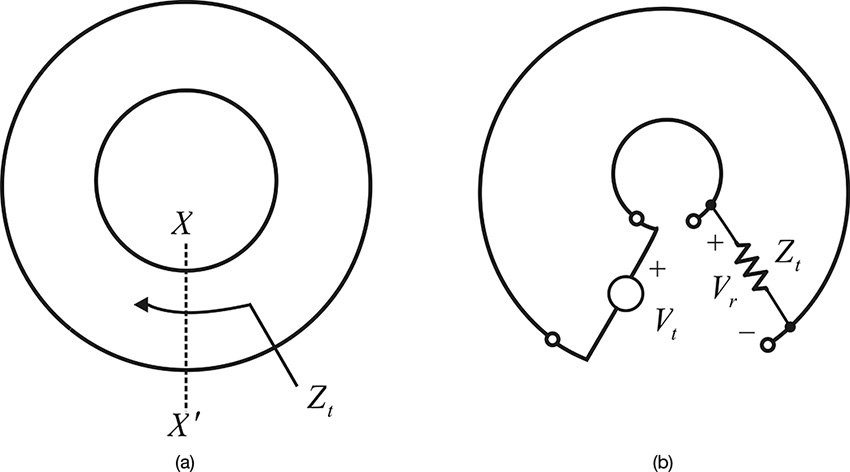

Compared to the one-port method, the open-loop gain method is obviously more intuitive and easier to apply when investigating the oscillation condition for an oscillator circuit using a feedback network. The oscillator circuit using feedback can be represented conceptually, as shown in Figure 10.19(a). In order to calculate the open-loop gain of the oscillator circuit, that circuit is cut to break the feedback, as shown in Figure 10.19(b).

Figure 10.19 (a) Conceptual feedback network and (b) the open-loop network for calculating open-loop gain. The open-loop gain is equal to Vr/Vt.

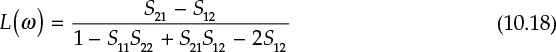

The open-loop gain can be computed by applying a test source Vt and measuring the return voltage Vr at the load with the impedance Zt, which is equal to that looking into the source side prior to breaking the loop. However, it is generally difficult to find the impedance Zt at the cut plane. To this end, the feedback is considered as an infinite number of identical open-loop networks connected end to end. When the two-port S-parameters for the two-port open-loop network in Figure 10.19(b) are defined as Sij, the open-loop gain L can be expressed as Equation (10.18).

For L(ω) to satisfy the oscillation conditions in Equation (10.15), the open-loop network can oscillate when it is closed. In that equation, S11, S22, and S12 are generally small, and L(ω) is simplified as

From Equation (10.19), the oscillation condition is determined as

The feedback-type oscillator can easily be designed using Equations (10.20a) and (10.20b). The feedback-type oscillator is usually composed of cascaded two-port circuits. For example, the oscillator circuit in Figure 10.16 can be viewed as the cascaded connection of an amplifier and a resonator. Using the S-parameters of each block, the two-port S-parameters of the open-loop network can be obtained. Also, if each block is matched, the open-loop gain is simply the product of each block’s S21, and the oscillation frequency satisfying Equations (10.20) can be easily found. Once the open-loop gain satisfying Equation (10.20) at the oscillation frequency is obtained, the oscillator can be built up simply by closing the open loop. In addition, the large-signal equilibrium conditions can be obtained from the response of the open-loop gain for amplitude change, which can be computed using OSCPort in ADS.

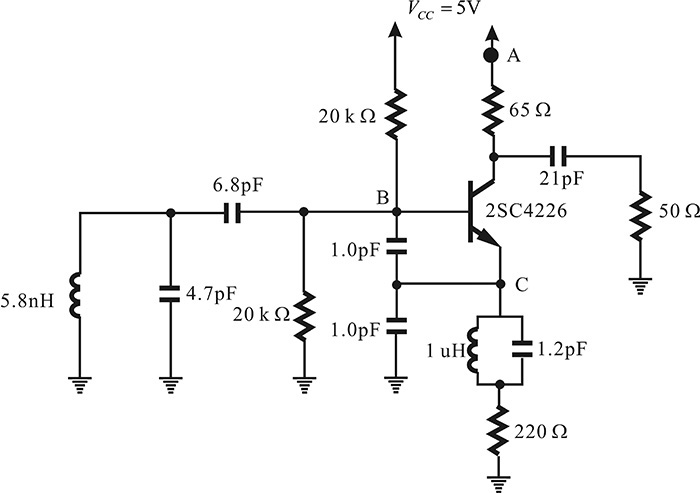

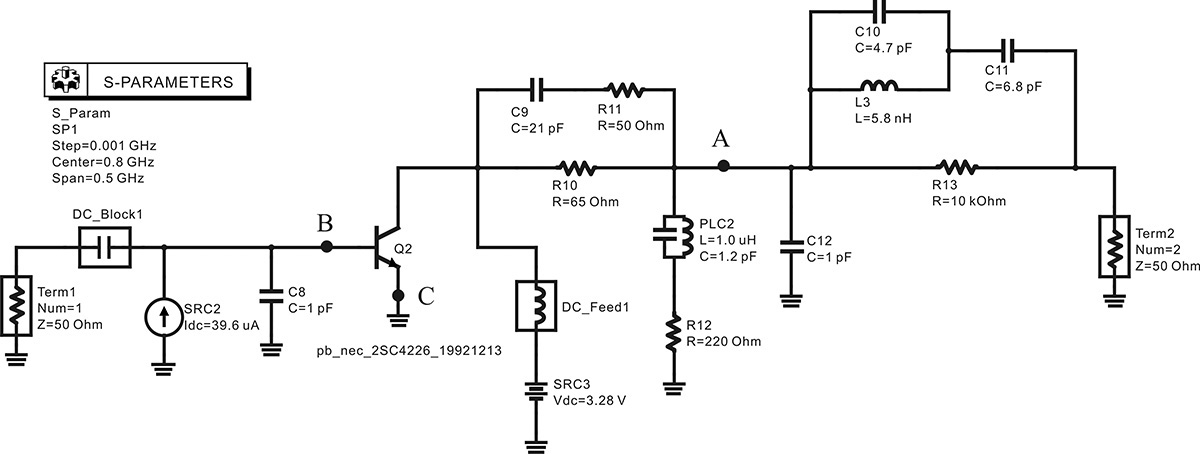

The circuit shown in Figure 10E.12 is a Colpitts oscillator. Calculate its oscillation frequency by the open-loop gain method using ADS.

In the circuit shown in Figure 10E.12, the ground point is eliminated and a new ground point C is set at the transistor’s emitter. With the changed ground point, the input of the open loop is defined by the base emitter (B–C plane) of the transistor and the open loop is formed by breaking the oscillator circuit at the B–C plane, as shown in Figure 10E.13. The collector-emitter voltage and base current are determined in advance through DC simulation for the circuit in Figure 10E.12. In order to maintain the DC operating point of the transistor, the determined collector-emitter voltage and base current are supplied by a new DC current source and a voltage source, as shown in Figure 10E.13. After setting up the circuit, the S-parameter simulation is carried out.

Figure 10E.13 Circuit for calculating the open-loop gain. First, DC analysis is carried out for the circuit shown here. Then, the computed base current and VCE are applied to bias 2SC4226, as shown in this figure. Finally, the circuit, which is cut along points B and C, is redrawn and the new ground point is set to point C.

After simulation, the equation in Measurement Expression 10E.3 is entered in the display window to compute and plot the open-loop gain.

![]() G=(S(2,1)-S(1,2))/(1-S(1,1)*S(2,2)+S(1,2)*S(2,1)-2*S(1,2))

G=(S(2,1)-S(1,2))/(1-S(1,1)*S(2,2)+S(1,2)*S(2,1)-2*S(1,2))

Measurement Expression 10E.3 Open loop gain calculation using the simulated S-parameters

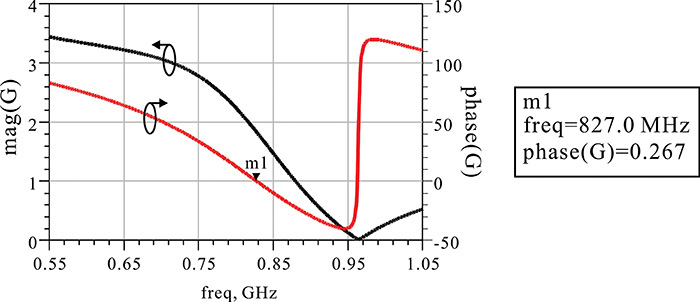

The magnitude and phase of the open-loop gain are shown in Figure 10E.14. The oscillation frequency is approximately 827 MHz. To compute the large-signal oscillation frequency, the previously described OscPort is inserted in the oscillator circuit in Figure 10E.12. The calculated oscillation frequency confirms the obtained 827 MHz shown in Figure 10E.14. Note that the ground point was moved to the transistor’s emitter for calculating the open-loop gain, which made the calculation easy. This change to the ground point is frequently used in oscillator design and is called virtual ground technique.

Figure 10E.14 Calculated open-loop gain. The phase of the open-loop gain crosses 0 at 827 MHz, at which the open-loop gain G > 1. Thus, the small-signal oscillation condition based on the open-loop gain is satisfied at 827 MHz.

10.3 Phase Noise

10.3.1 Spectrum of an Oscillation Waveform

The output waveform of an oscillator is not a pure sine wave and its amplitude and phase fluctuate with time. Thus, denoting the oscillation output power across a 1-Ω resistor as P, the waveform can be expressed in time domain as shown in Equation (10.21).

Here, we assumed the power P across the 1-Ω resistor but it does not lose generality. The a(t) represents the fluctuation of the amplitude, and ϕ(t) represents the fluctuation of the phase in the time domain. The a(t) is called the amplitude modulation (AM) noise while ϕ(t) is called the phase noise of the oscillator.

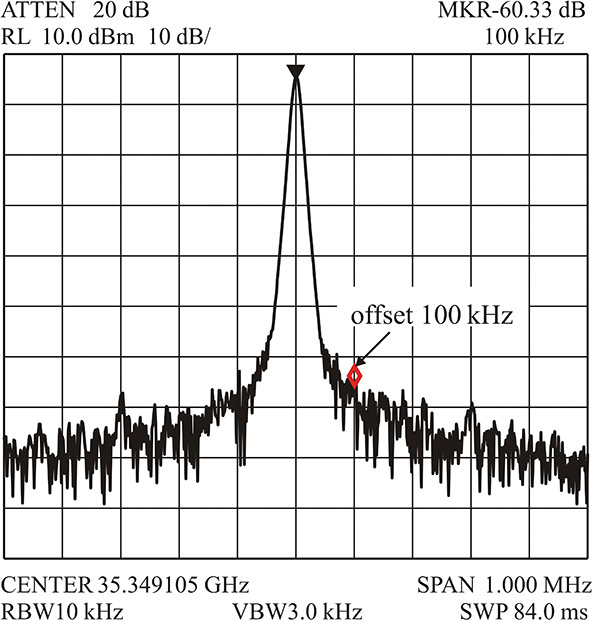

Two major issues are associated with understanding amplitude and phase noises. The first is the mathematical model or mechanism of the amplitude and phase noises and the second is how to measure these noises. We will first discuss the measurement method and then the mathematical model of the phase noise will be explained.

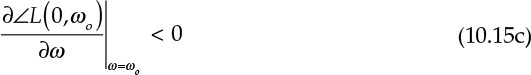

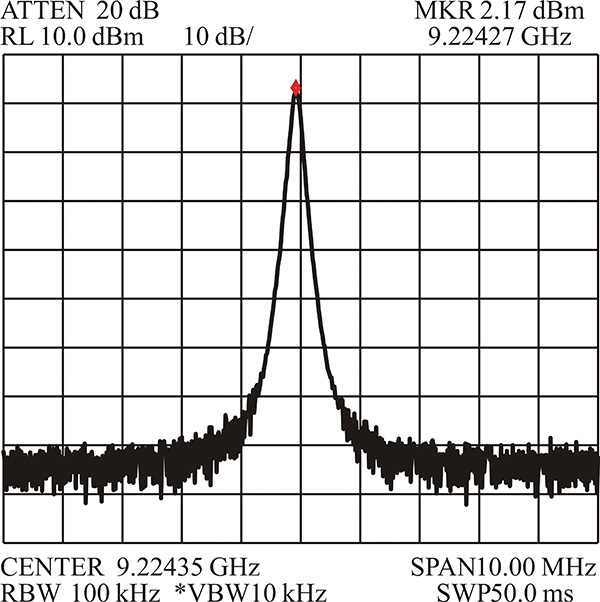

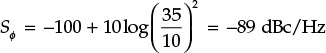

When the waveform represented by Equation (10.21) is observed on a spectrum analyzer, the spectrum is usually similar to that shown in Figure 10.20. The spectrum analyzer can be thought of simply as equipment showing the spectral power of an input signal that is the output power of a narrow-band filter. The center frequency of the narrow-band filter moves with time while maintaining the user-specified resolution bandwidth (RBW). Thus, the spectrum analyzer shows the power within the RBW on the axis of the frequency. In displaying the power with the RBW, the spectrum analyzer averages the measured power within the RBW in a given amount of time. The VBW (video bandwidth) is used as a measure of time averages. Usually, because VBW is expressed as a frequency, it is the reciprocal of the average time and so it is smaller than the RBW. The spectrum shown in Figure 10.20 is measured for a span of 1 MHz at the center frequency of 35.349 GHz. Also, RBW = 10 kHz and VBW = 3 kHz. Thus, the spectrum in Figure 10.20 represents average power in the 10-kHz bandwidth over 1/3 msec.

Furthermore, when Equation (10.21) is expanded, it can be considered as the superposition of the sinusoidal component of frequency ωo, whose power is P and a noise power. The sine wave power appears as the power of the center frequency component and the noise power has a distribution that is spread around the center frequency. Since the spectrum of the sinusoidal wave of frequency fo has the spectrum of Pδ(f – fo), a power P appears when fo is within the RBW, otherwise P = 0. In addition, the value of the sinusoidal power P does not change even when the RBW is changed; that is, whether the RBW is lowered or increased, the same power appears. However, it should be noted that noise density (noise power per bandwidth) is constant in the case of the noise. Thus, by lowering the RBW, the noise power measured within the RBW is lowered, whereas the noise power measured within the RBW is raised when the RBW increases.

In Figure 10.20, the ratio of the center frequency power (or the carrier power) to the noise power at a frequency offset of 100 kHz from the center frequency is measured to be about –60.33 dBc. Calculate the carrier to noise power ratio measured at a 100-kHz offset when the RBW is changed to 1 Hz. Also calculate the power when the RBW is changed to 1 kHz.

Solution

As the power of the center frequency is the sine wave power, it does not change even if the RBW is changed. However, the power at the 100-kHz offset is a noise power and thus changes when the RBW is changed. Since the power is –60.33 dB when the RBW = 10 kHz, then –60.33 dB/10 kHz = –100.33 dB/Hz. In addition, when the RBW is changed to 1 kHz, the power at the marker can be measured by the same method to be –70.33 dB.

The spectrum in Figure 10.20 represents the contribution of a sine wave’s output and noise. The noise power also comes from the combined effect of fluctuations in the amplitude and phase. However, for most oscillators, because the fluctuation effect coming from the amplitude is low compared to that coming from the phase, the spectrum noted above is generally known to occur due to phase fluctuation.

The following conceptual experiment can be thought of as the proof for the claim above of the phase noise dominance in the measured spectrum. That is, in order to eliminate the AM noise due to the amplitude fluctuation, the oscillator output is passed through a limiter and then the output is passed through a narrow bandwidth bandpass filter to remove harmonics. The resulting spectrum reflects only the phase fluctuation. However, in most cases, almost the same spectrum is obtained as a result of this experiment, which leads to the conclusion that the spectrum in Figure 10.20 is mostly due to the phase noise. In addition, because the AM noise can always be removed using the limiter and filter, the spectrum noted above is considered to represent the phase noise.

10.3.2 Relationship between Phase Noise Spectrum and Phase Jitter

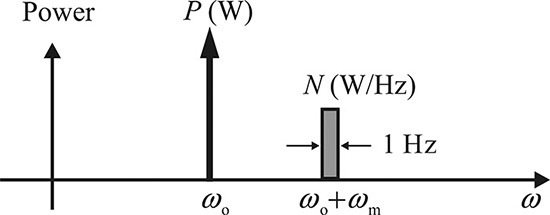

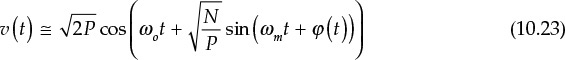

To see the relationship between the spectrum shown in Figure 10.20 and the phase fluctuation, consider a part of the noise spectrum at a frequency offset of ωm from the center frequency and the sine wave output shown in Figure 10.21. The waveforms in the time domain can be expressed as

Expanding Equation (10.22) using the additive theorem of trigonometric functions and assuming that P >> N, v(t) can be written as

Thus, the carrier is found to be phase-modulated by the noise signal and its power is almost equal to the carrier power. Since the maximum phase deviation is (N/P)½, then the peak phase jitter becomes (N/P)½. Alternatively, the phase jitter can be determined using a phasor diagram. The carrier becomes the phasor that rotates counter-clockwise and the noise phasor is placed at the end of the carrier phasor, which becomes a rotating phasor with angular velocity ωm, as shown in Figure 10.22. Therefore, the maximum phase error for P >> N is obtained with Equation (10.24).

Figure 10.22 Phasor diagram of Equation (10.22). The carrier can be represented by the phasor that rotates counterclockwise with an angular velocity of ωo, while the noise signal in Equation (10.22) can be represented by the phasor at the end of the carrier phasor rotating counterclockwise with an angular velocity of ωm.

Thus, the phase fluctuation is a function of the offset frequency and the maximum phase jitter at the offset frequency of ωm is expressed in Equation (10.25).

Calculate the peak phase jitter when the carrier to noise power at a 100-kHz offset is –100 dBc/Hz.

Solution

Thus, the phase jitter = 10–5 rad.

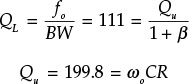

10.3.3 Leeson’s Phase Noise Model

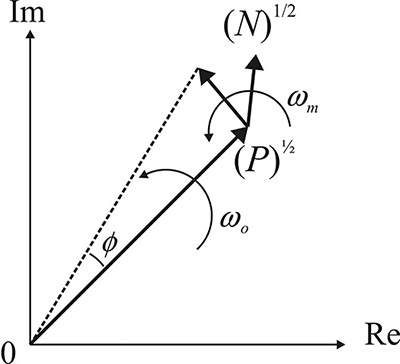

The phase noise of an oscillator can be qualitatively explained using a simple oscillator model shown in Figure 10.23. In general, an oscillator can be represented as a circuit composed of an amplifier and a feedback network, as shown in Figure 10.23. Here, the frequency dependence of the amplifier gain is imposed on the feedback network and the amplifier is assumed to have a constant gain. In addition, the transfer characteristic of the feedback network can generally be expressed as shown in Equation (10.26),

Figure 10.23 A simplified oscillator structure. The phase at the amplifier input is denoted by θ, while that of the amplifier output is denoted by ϕ.

where ωo represents the oscillation frequency and ωm = ω - ωo represents the offset frequency. Generally, the magnitude of the frequency response in Equation (10.26) is approximately constant, while the phase is approximated as a straight line that decreases linearly within the 3-dB angular bandwidth of BW = ωo/Q.

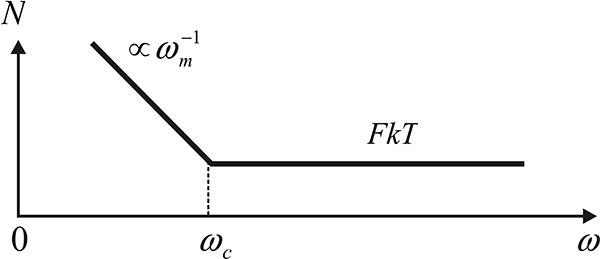

In the oscillator structure shown in Figure 10.23, the equivalent noise source N can be placed at the amplifier input; its frequency characteristic is shown in Figure 10.24. The F in Figure 10.24 represents the noise factor, which will be added to the oscillator signal.

Figure 10.24 Noise at the amplifier input. The noise power at the amplifier input can be represented by FkT, which is explained in Chapter 4. At low frequency, the noise increases from FkT. The frequency ωc = 2πfc is called the corner frequency or flicker frequency.

Suppose that the oscillation signal is frequency-modulated by the noise signal shown in Figure 10.24 due to the nonlinearity of the amplifier. The frequency-modulated signal then appears at the output of the amplifier, which is the oscillator output signal. The peak frequency deviation of the frequency-modulated signal by the noise is denoted as Δω. Note that Δω is proportional to N shown in Figure 10.24. Then, the frequency-modulated signal is applied to the input of the feedback network, and the output of feedback network appears again at the input of the amplifier. When the oscillator output, which is frequency-modulated by the noise, is applied to the input of the feedback network, the frequency-modulated signal is transformed into a phase-modulated signal by the feedback network. The peak phase deviation Δθ of the phase-modulated signal is related to the peak frequency deviation as expressed in Equation (10.27).

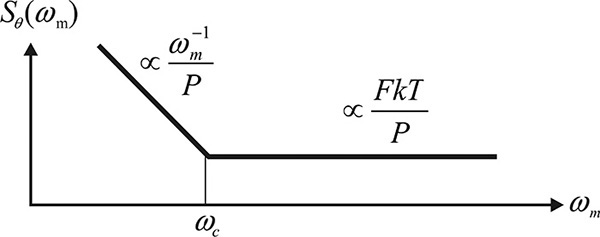

Thus, the phase-modulated signal with the peak phase deviation given by Equation (10.27) will appear at the input of the amplifier. Note that both Δω and Δθ are proportional to (N)½, shown in Figure 10.24. Since the peak phase deviation Δθ is proportional to (N)½, the single-sideband phase noise at the input of the amplifier can be plotted, as shown in Figure 10.25. Here, the carrier power at the amplifier input is denoted as P.

Figure 10.25 The phase noise at the amplifier input computed using the noise power shown in Figure 10.24

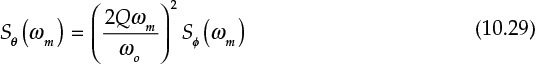

The phase noise of the amplifier input in Figure 10.25 can be written as Equation (10.28).

In addition, at the oscillator output, the peak frequency deviation Δω is related to the peak phase deviation Δϕ by Δω = ωmΔϕ. Using Equation (10.27), the relationship between the phase noise appearing at the amplifier input and the phase noise appearing at the oscillator output is expressed in Equation (10.29).

Also, outside the resonator bandwidth BW there is no such relationship, which is shown in Equation (10.30).

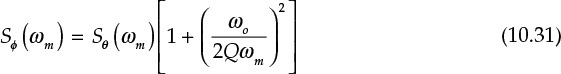

Therefore, combining Equations (10.29) and (10.30), the combined can be written as Equation (10.31).

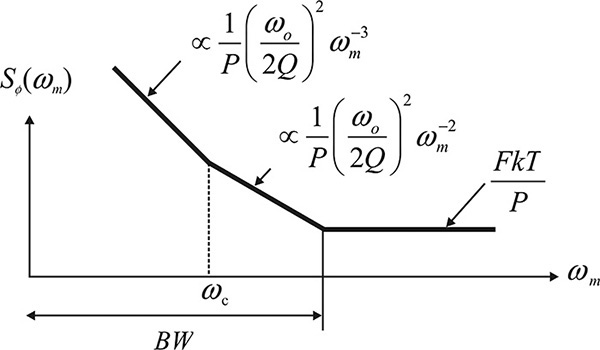

This is shown in Figure 10.26; that is, near the oscillation frequency, the phase noise decreases by ω–3 (30 dB/decade) and, after the 1/f noise disappears, the phase noise decreases by ω–2 (20 dB/decade). Then, outside the resonator’s bandwidth, it is proportional to the noise figure and shows a constant phase noise. It should also be noted that the higher the Q of the feedback network, the lower the phase noise.

Figure 10.26 Phase noise of the oscillator. BW is the bandwidth of the feedback network. Outside the BW, the phase noise due to the white noise is given by FkT/P and it is increasing in proportion to ωm–2 inside BW. The phase noise further increases due to the flicker noise in proportion to ωm–3.

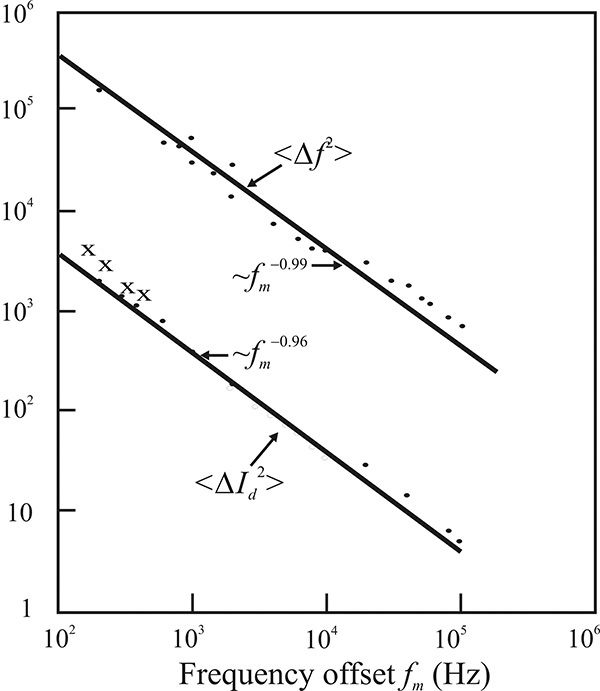

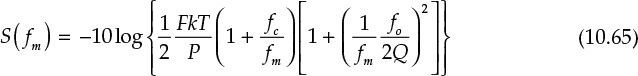

In conclusion, the phase noise S(fm) based on Leeson’s phase noise model can be expressed as

The Leeson’s phase noise model expressed in Equation (10.32) is an approximate description of phase noise. Note that the phase noise generation in an oscillator is basically a nonlinear phenomenon. However, the phase noise asymptotically approaches the Leeson’s phase noise model for higher fm. In addition, it should be noted that noise factor F of the amplifier in Equation (10.32) is seldom equal to the measured amplifier noise factor; for more information, see reference 3 at the end of this chapter. Noise factor F around the oscillation frequency is thought to be caused by the thermal noise and the DC bias-dependent shot noise. However, the DC bias-dependent shot noise generally becomes a function of the oscillating signal. As a result, it is modulated by the oscillating signal. Thus, it acts as a cyclostationary noise source in the oscillator, which makes F in Equation (10.32) differ from the measured amplifier noise figure. In addition, the flicker noise is also DC bias dependent and the flicker frequency fc in Equation (10.32) may also differ from the measured flicker frequency due to flicker-noise conversion dynamics. Recently, significant published research has focused on cyclostationary noises. However, a design for a low-phase noise oscillator to meet a given phase noise specification is still only a theory despite recent research on oscillator phase noises and the emergence of modern CAD simulators. We will present the experimental method to meet the design objective of the phase noise in the design of a DRO (dielectric resonator oscillator) in section 10.7.

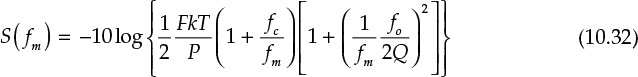

The Leeson model is based on deduction and should be proven experimentally.3 The basic assumption is the frequency modulation by the noise at the amplifier input, namely the peak frequency deviation, is proportional to the noise frequency characteristic. This assumption has been experimentally verified by Pucel and Curtis, who measured the 1/f noise of the drain current of a GaAs FET under a given DC voltage. The fluctuation of the drain current ΔId2 observed with a spectrum analyzer is shown in Figure 10.27. Using the drain current fluctuation, the peak frequency deviation Δf2 of the oscillation output can be calculated. This peak frequency deviation is usually referred to as FM noise. In this case, the frequency dependence of the FM noise must be the same as that of the drain current noise since the FM noise is assumed to be proportional to the drain current noise. The measured and computed FM noises shown in Figure 10.27 are found to have the same frequency dependence as that of the drain current noise.

3. D. B. Leeson, “A Simple Model of Feedback Oscillator Noise Spectrum,” Proceedings of the IEEE 54, no. 2 (February 1966): 329–330.

Figure 10.27 The Pucel experimental results of a GaAs FET 10-GHz oscillator phase noise.4 Baseband noise ΔId2 represents the measured drain current fluctuation in unit (nA2/Hz), while FM noise is measured in the unit (Hz2/Hz). Since the FM noise is directly proportional to the baseband noise as expressed in Equation (10.27), the FM noise should show the same dependence as in the baseband noise, and this clearly appears in the plot.

4. R. A. Pucel and J. Curtis, “Near-Carrier Noise in FET Oscillators,” IEEE MTT-S International Microwave Symposium Digest, (May 31–June 3, 1983): 282–284.

10.3.4 Comparison of Oscillator Phase Noises

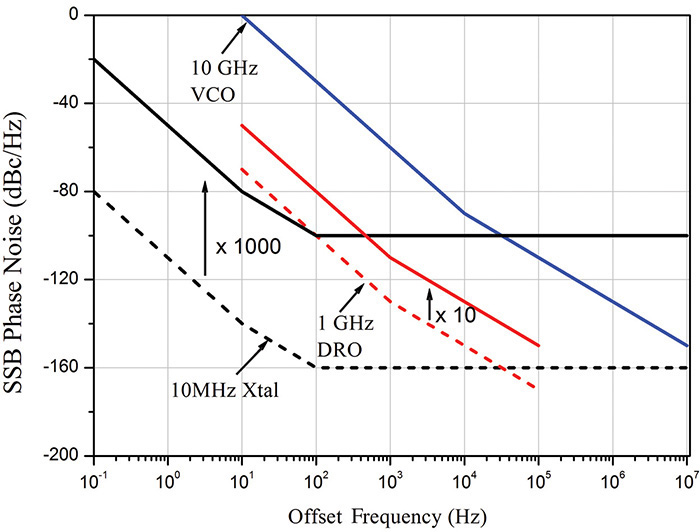

It is often necessary to compare the performance of oscillators in terms of phase noise even though the oscillators generally have different oscillation frequencies. To compare the phase noises of two oscillators with different oscillation frequencies, the frequency of one oscillator must first be made equal to that of the other using frequency division or multiplication. First, we will examine the changes in phase noise resulting from frequency multiplication or division.

Suppose that the time-domain waveform of an oscillator is given by Equation (10.33).

Then, after the frequency multiplication by n, the resulting output waveform can be expressed with Equation (10.34).

Thus, the phase noise of the multiplied waveform can be expressed as Equation (10.35),

which represents a degradation of the phase noise by n2. As an example, the frequency of a 10-MHz crystal oscillator is multiplied by n = 1000 to give the frequency of 10 GHz. Since n = 1000, the phase noise increases by 60 dB.

In this way, the phase noises of various oscillators can be compared, as shown in Figure 10.28, where a crystal oscillator, a DRO (dielectric resonator oscillator), and a microstrip VCO (voltage-controlled oscillator) are graphed. Their oscillation frequencies are 10 MHz for the crystal oscillator, 1 GHz for the DRO, and 10 GHz for the microstrip VCO. The frequencies of the oscillators are first set to 10 GHz. Thus, the frequencies of the crystal oscillator and the DRO are multiplied by factors n = 1000 and 10, respectively. After the frequency multiplication, the phase noises are compared, as shown in Figure 10.28. From this figure, although the noise floor of the crystal oscillator is higher (as a result of multiplying the frequency by a factor of 1000), the phase noise at low frequency can be found to be the lowest compared to the other oscillators. This is followed by the DRO, and then the microstrip VCO, which has the poorest phase noise.

Figure 10.28 Comparison of the phase noises of various oscillators: a 10-MHz crystal oscillator, a 1-GHz DRO, and a 10-GHz VCO. All the frequencies are converted to the 10-GHz frequency.

At a 100-kHz frequency offset, a VCO with a center frequency of 10 GHz has a phase noise of -100 dBc/Hz, while another VCO with a center frequency of 35 GHz has a phase noise of -96 dBc/Hz. Compare the phase noises of the two oscillators.

Solution

To set the frequency of the 10-GHz VCO to 35 GHz, the required frequency multiplication factor is

The phase noise of the 10-GHz VCO after its frequency multiplication by n equals

Thus, the phase noise of the 10-GHz VCO is poorer than that of the 35-GHz VCO by 7 dB.

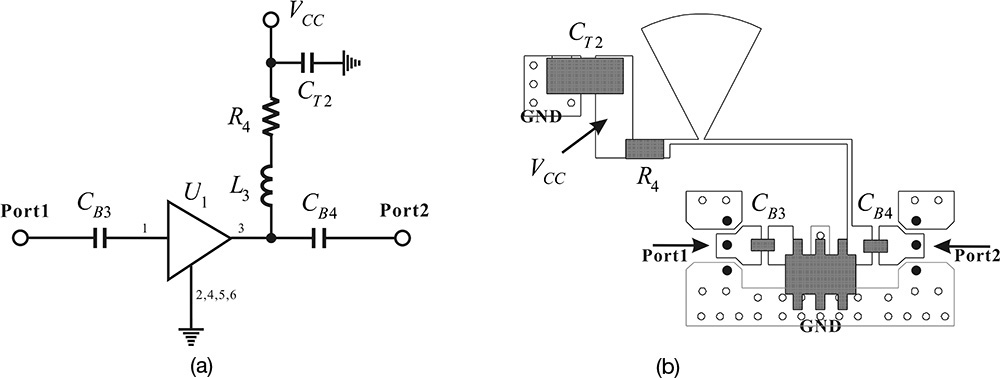

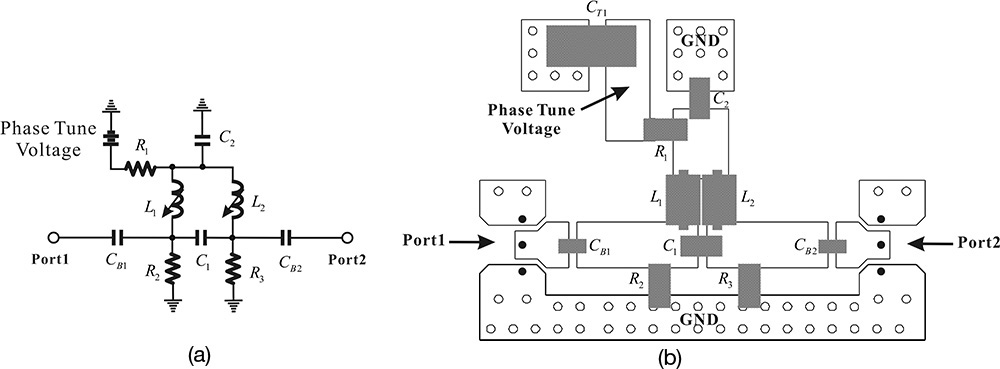

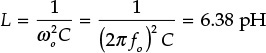

10.4 Basic Oscillator Circuits

10.4.1 Basic Oscillator Circuits

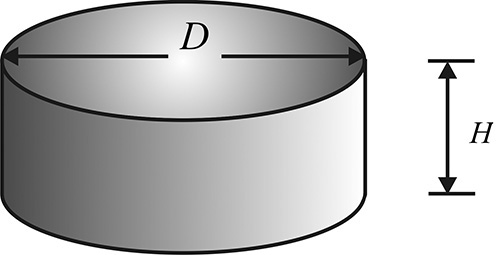

The possibility of oscillation for a given oscillator circuit was investigated in section 10.2. Now we will present the design of oscillator circuits that oscillate at a specified frequency. The design of an oscillator circuit can be carried out using basic oscillator circuits.

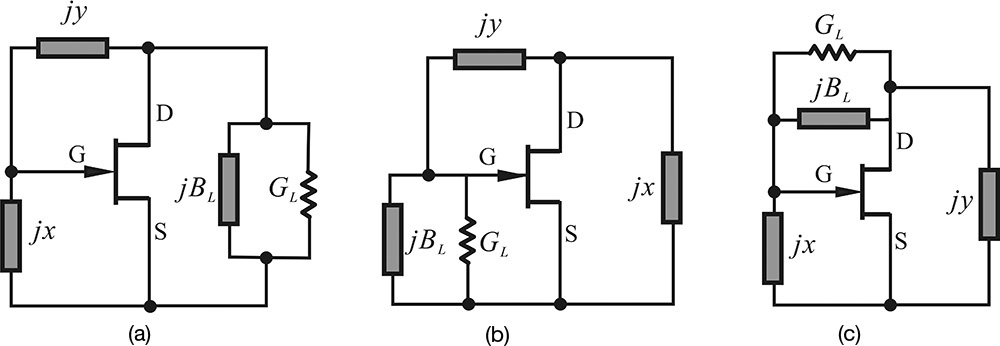

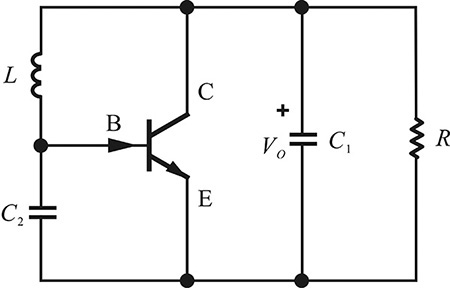

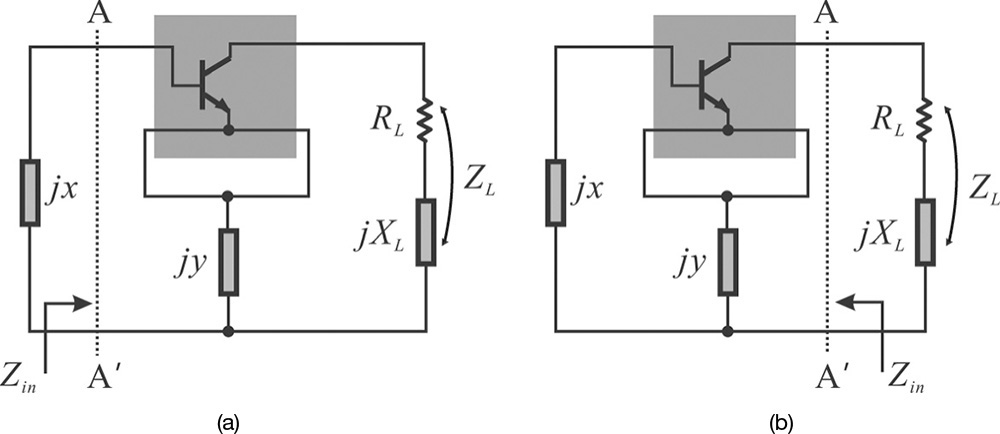

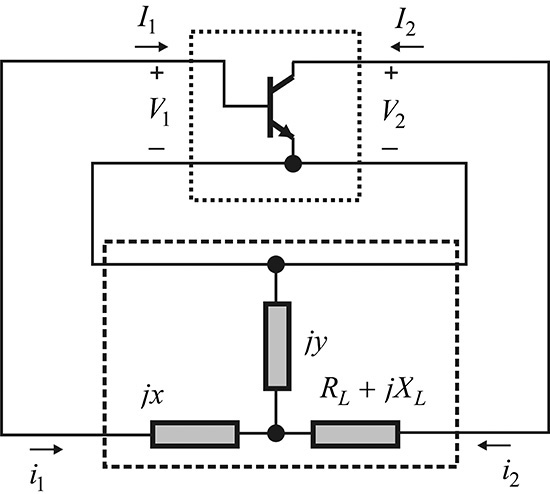

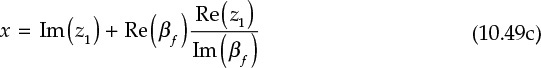

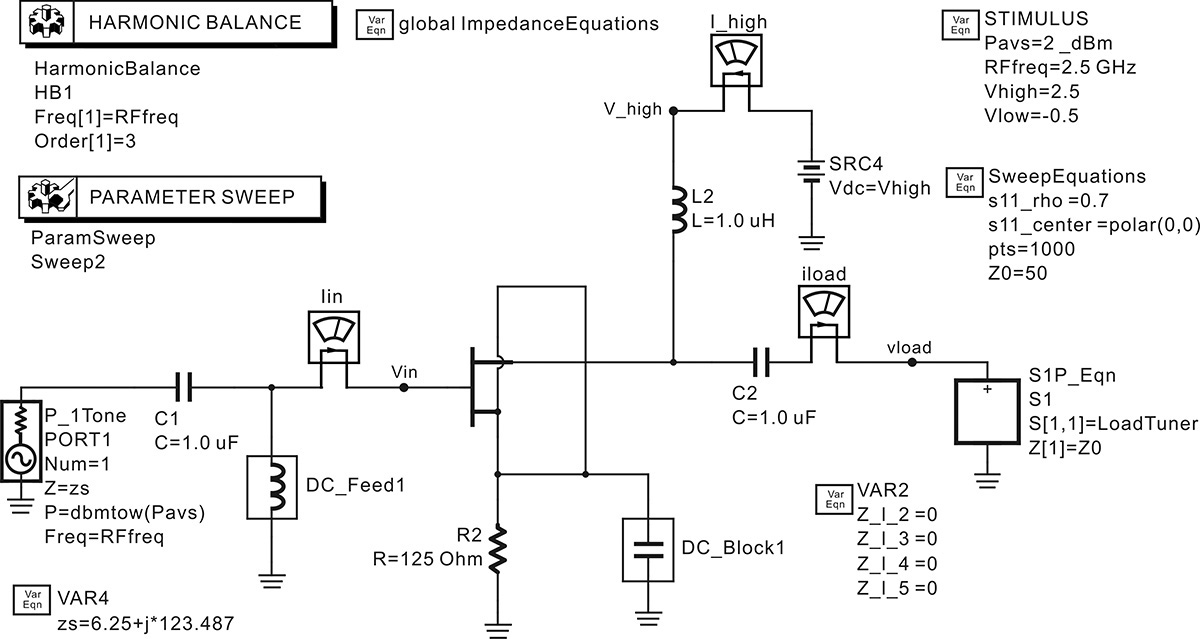

First, after removing the DC bias circuits and all the elements that have no effects at the RF in a given oscillator circuit, most oscillator circuits can be categorized into two configurations: series feedback oscillators, as shown in Figure 10.29, or parallel feedback oscillators, as shown in Figure 10.30. In Figure 10.29, the series feedback is achieved by jy, which delivers the transistor DS output to the GS input. In contrast, the parallel feedback shown in Figure 10.30 is achieved by jy, which delivers the DS output to the GS input. Three types of series feedback oscillator configurations and three types of parallel feedback oscillator configurations are shown in Figures 10.29 and 10.30, respectively.

Figure 10.29 Three series feedback oscillators. (a) The load is connected to the drain, (b) to the source, and (c) to the gate terminals.

Figure 10.30 Three parallel feedback oscillators. (a) The load is connected to the drain, (b) to the gate terminals, and (c) to the feedback path.

The classifications for the three types of configurations in Figures 10.29 and 10.30 are based on where the loads are connected, whereas the feedback type can be found to be essentially the same for all three types. In addition, jx and jy in the figures represent the reactance of a capacitor or inductor in the series feedback configurations, while they represent the susceptance of a capacitor or inductor in the parallel feedback configurations.

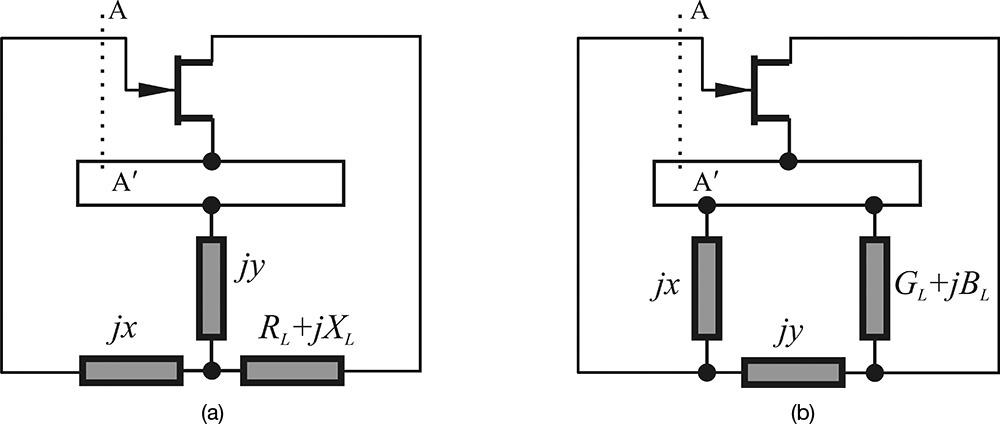

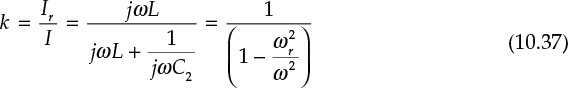

The basic forms of the oscillator circuits in Figures 10.29 and 10.30 can be represented by an amplifier and a feedback network. The basic form of the series oscillator shown in Figure 10.29 can be converted into the T-type feedback network in Figure 10.31(a), and the basic form of the parallel feedback oscillator can be converted into the π-type feedback network in Figure 10.31(b).

Figure 10.31 The conversion of the oscillator circuit into a feedback form. (a) T-type feedback network converted from the basic oscillator circuit in Figure 10.29(a) and (b) π-type feedback network converted from the parallel feedback oscillator in Figure 10.30(a)

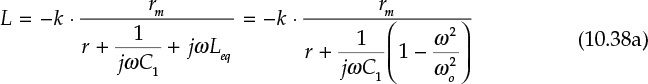

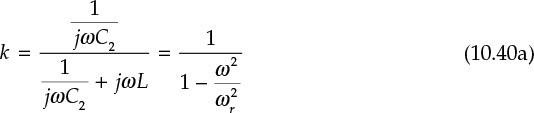

The oscillation mechanism of the series or parallel configuration can be qualitatively understood by analyzing the feedback structure. First, for the series configuration of Figure 10.29(a), the reactance jx is replaced by capacitor C2, the feedback reactance jy is replaced by inductor L, and the load is replaced by a capacitor C1 and resistor r in series. In addition, since the input impedance of the transistor at high frequencies is generally low, by approximating it as short, the equivalent circuit of the transistor can be represented by a current-controlled voltage source, as shown in the shaded rectangle of Figure 10.32. The open-loop circuit can be obtained by cutting the FET input (the A–A’ reference plane in Figure 10.31) and reconfiguring the circuit. As the input impedance of the transistor is approximated as short, a shorted load can be connected where the cut occurs. To obtain the open-loop gain, a unit current source is applied to the transistor input of the open-loop circuit, which is shown in Figure 10.32. The open-loop gain is then the –Ir of Figure 10.32.

Figure 10.32 Open-loop circuit of the circuit in Figure 10.31(a). The gate-source plane is cut and the unit test current is applied.

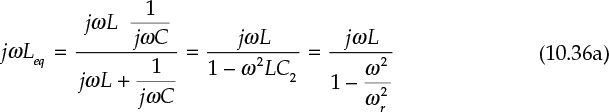

Here, Equations (10.36a) and (10.36b) express the parallel impedance of L and C2.

Thus, at frequencies lower than ωr, L and C2 in parallel are equivalently treated as an inductor Leq. In addition, since the current transfer function Ir/I becomes

at frequencies lower than ωr, the phase of k becomes 180° and a phase inversion occurs, as expressed in Equation (10.37). In contrast, at frequencies higher than ωr, the phase becomes 0° and results in the disappearance of the phase inversion. It also is worth noting that k is a real number. In addition, the open-loop gain L is now expressed by Equations (10.38a) and (10.38b).

Since ωo < ωr, the open-loop gain is positive real at ω = ωo and therefore the phase of the open-loop gain is 0. The open-loop gain is

When the gain given by Equation (10.39) is greater than 1, oscillation can form. In the circuit, note that phase inversion occurs due to L||C2 and the oscillation frequency occurs at the resonant frequency of L||(C1 + C2). This is shown in Figure 10.33.

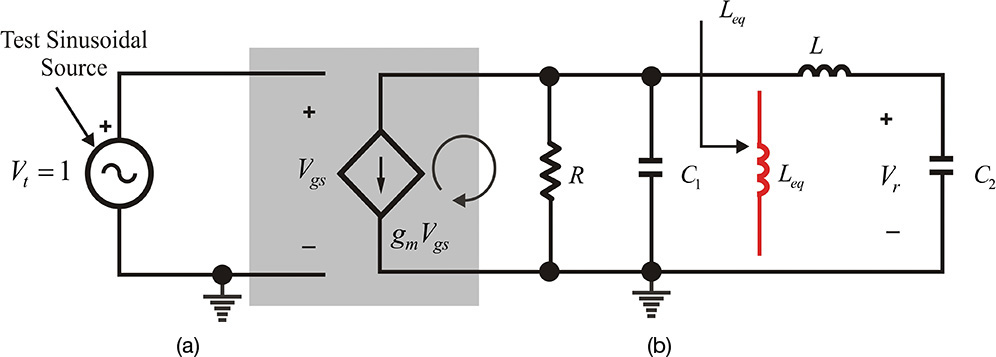

Figure 10.33 (a) Phase of k and (b) open-loop gain of the series feedback oscillator for the frequency

In the case of the parallel feedback oscillator in Figure 10.30(a), the oscillator circuit can be similarly implemented by replacing the reactance jx with a capacitor C2, the feedback reactance jy is replaced with an inductor L, and the load is replaced with a capacitor C1 and resistor R in parallel. Furthermore, the input impedance of the transistor at low frequencies is generally high; the equivalent circuit of the transistor can be approximately represented by a voltage-controlled current source, as shown in the shaded area of Figure 10.34. Similar to the previously discussed series-feedback-type oscillator, to obtain the open-loop gain, the circuit is cut at the transistor input and the open-loop circuit is drawn as shown in Figure 10.34, where a unit voltage source is applied to the input, and the open-loop gain is obtained by calculating the voltage Vr returning from the output to the input.

Figure 10.34 Circuit for calculating the open-loop gain of a parallel feedback oscillator circuit. The gate source in Figure 10.31(b) is cut and the test voltage is applied to calculate the open-loop gain.

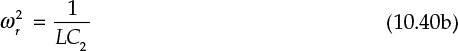

From that figure, the voltage transfer function computed as k = Vr/Vo is given by Equations (10.40a) and (10.40b).

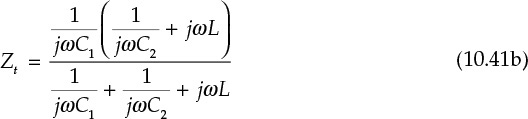

Thus, phase inversion appears for frequencies higher than ωr and disappears for frequencies lower than ωr. In addition, as in the case of series feedback, k is a real number. In addition, the open-loop gain is shown in Equations (10.41a) and (10.41b).

Thus, the open-loop gain is given by Equation (10.42).

Since the imaginary part of the denominator of the expression above must be 0 for oscillation to occur, the oscillation frequency

It can also be seen that ωo > ωr from Equations (10.40b) and (10.43). Substituting Equation (10.42) into the open-loop gain equation, the following condition must be satisfied for oscillation to occur:

Thus, no oscillation occurs when the open-loop gain given by Equation (10.44) is less than 1. From that equation, the oscillation frequency is the resonant frequency of the overall LC resonant circuit seen from the output. Furthermore, since ωo > ωr, the value of k is found to be negative. That is, the oscillation frequency must always be higher than the frequency that causes the phase inversion. Because the amplifier is an inverting amplifier that has its own phase inversion of 180o, the k network should provide the phase inversion of 180o to restore the overall phase of the open-loop gain to 0º. This is shown in Figure 10.35.

Figure 10.35 (a) Phase of k and (b) open-loop gain of the parallel feedback oscillator for the frequency

10.4.2 Conversion to Basic Forms

The actual oscillator circuit is realized by applying DC voltage to the basic-form oscillator circuit that represents the equivalent circuit at the RF frequency. The actual oscillator circuit sometimes looks slightly different from the basic forms. However, most oscillators when simplified can be converted to the previously mentioned basic forms of the oscillator. Thus, for a given oscillator circuit, the design tasks first require the conversion of the oscillator circuit to one of the basic forms and then DC voltage must be applied to the selected basic form of the oscillator circuit. In this section, we will examine these tasks through some examples.

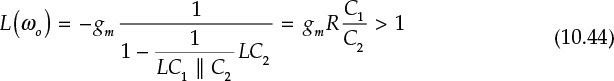

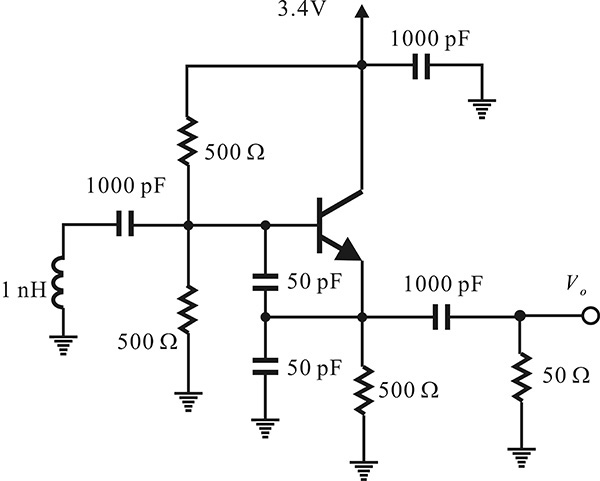

Figure 10E.15 represents a microstrip oscillator circuit. Simplify this circuit and convert it into the oscillator circuit’s basic form.

Solution

Removing the DC bias circuit portion of Figure 10E.15 results in the bottom-right circuit in Figure 10E.16.

The circuit connected to the drain terminal can be seen as an RC series circuit at the oscillation frequency. Also, assuming the length of transmission line is short, the transmission line connected to the source can be seen as an inductor. In addition, the two transmission lines connected to the gate terminal can be considered as a capacitor and, by removing the ground, the microstrip oscillator circuit can be equivalently redrawn as the basic form of the series feedback oscillator in Figure 10.29(a).

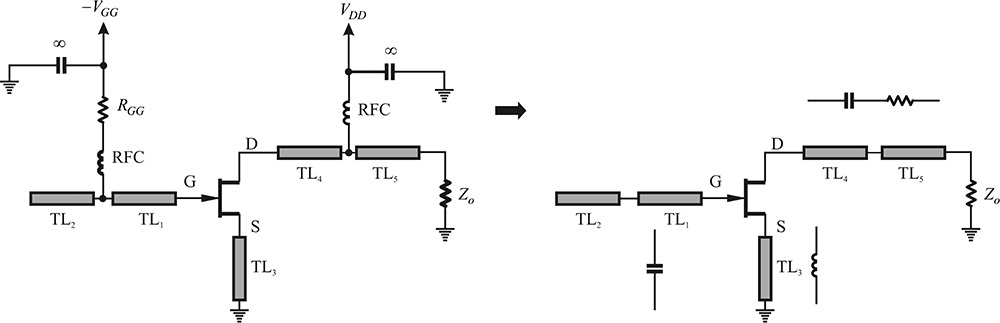

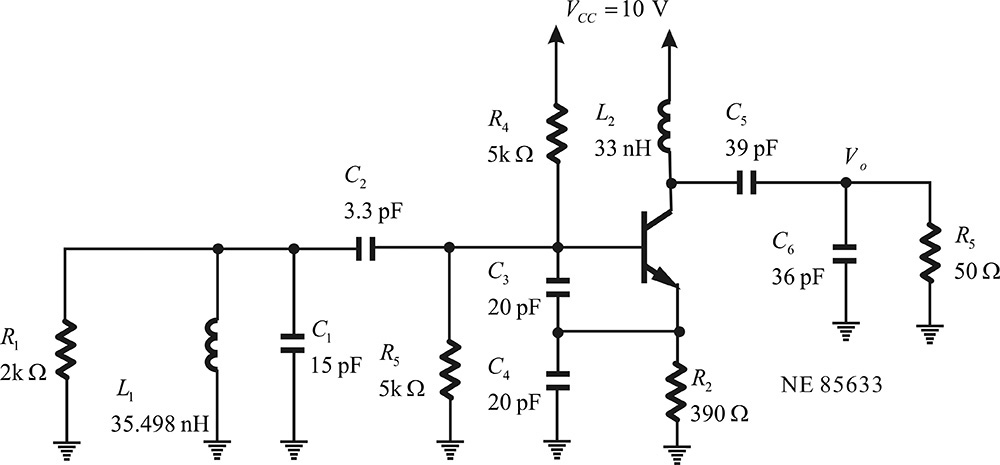

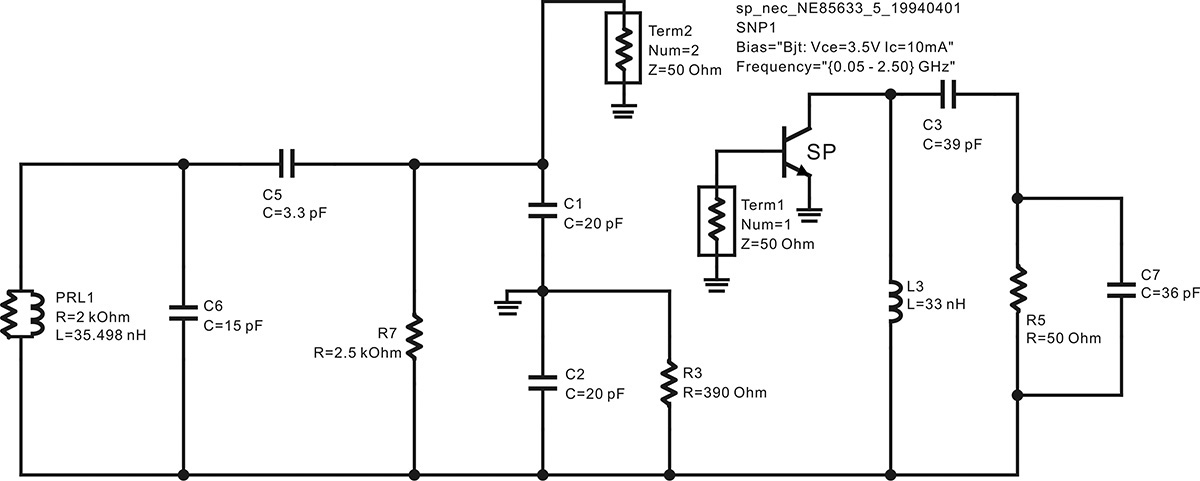

The circuit shown in Figure 10E.17 is a 200-MHz-band Colpitts oscillator.5 The S-parameters of transistor NE85633 at Vce = 3.5 V and Ic = 10 mA are used. Show that the circuit oscillates at 200 MHz using the open-loop gain. Then, using ADS, convert the circuit into a basic parallel feedback oscillator and calculate the values of the resulting admittance jx, jy and the load admittance GL + jBL at 200 MHz.

5. M. Randall and T. Hock, “General Oscillator Characterization Using Linear Open-Loop S-Parameters,” IEEE Transactions on Microwave Theory and Techniques 49, no. 6 (June 2001): 1094–1100.

Solution

After removing the ground point in Figure 10E.17 and moving the new ground to the transistor’s emitter, the S-parameter of NE85633 is inserted and simulated in ADS, as shown in Figure 10E.18, to confirm the open-loop gain at 200 MHz. To compute the open-loop gain, the oscillator feedback is cut at the base-emitter plane. Two ports are connected where the feedback loop is cut, as shown in Figure 10E.18.

Figure 10E.18 Circuit for calculating the open-loop gain. The ground point is moved to the emitter and the oscillator is cut along the base emitter. After the breaking the loop, the oscillator circuit is redrawn. Note that the S-parameter data component for NE85633 is used.

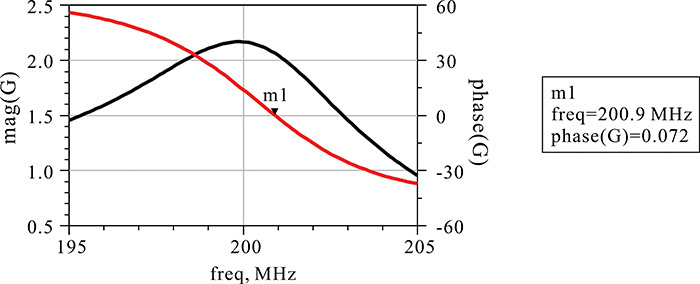

After the S-parameter simulation, the equation in Measurement Expression 10E.3 is similarly entered in the display window to compute the open-loop gain G using the simulated S-parameters. The simulated open-loop gain G is shown in Figure 10E.19. From the phase of G, the oscillation condition is found to be satisfied at a frequency of approximately 200.9 MHz.

Figure 10E.19 Open-loop gain calculation result. The phase of the open-loop gain crosses 0 at about 200.9 MHz, at which |G| > 1 and the oscillation is possible.

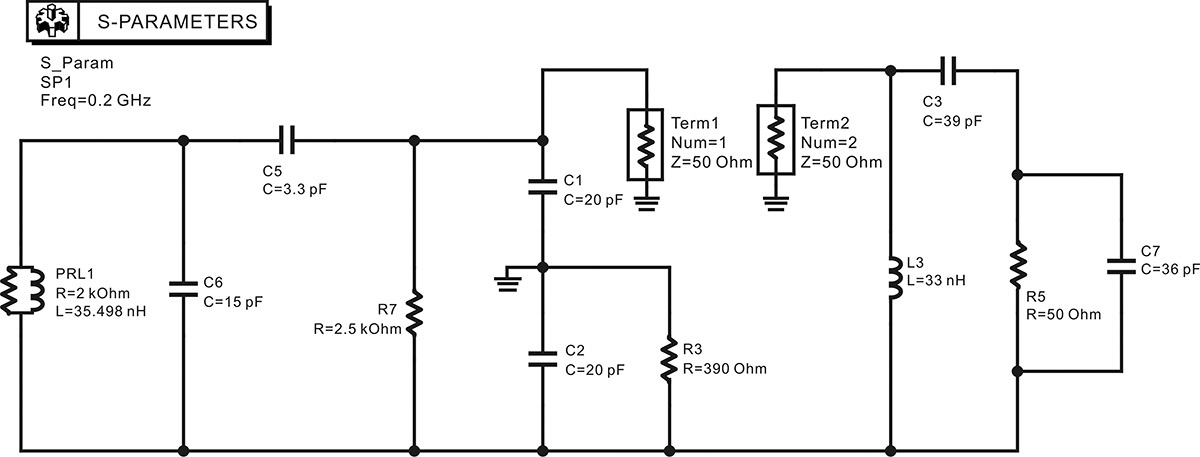

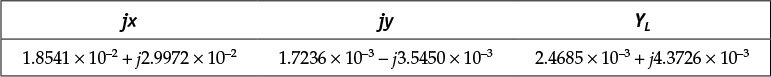

The two-port parameter values of the oscillator circuit’s feedback network can be obtained by removing the transistor, as shown in Figure 10E.20. The two-port Y-parameters of the circuit shown in that figure can now be obtained. These parameters can be represented by the p-type circuit shown in Figure 10.31(b). Since it is a passive network, y11 + y12 corresponds to the admittance jx, and y22 + y12 corresponds to YL = GL + jBL, while jy corresponds to -y12 in the basic form of the parallel feedback oscillator. Therefore, the following equations shown in Measurement Expression 10E.4 are entered in the display window and the values of the admittances in Table 10E.1 are displayed in a list.

Figure 10E.20 Calculation of the two-port circuit parameters external to the oscillator. To obtain the Y-parameters of the feedback network, the BJT is removed and the Y-parameters are computed for the remaining network.

![]() jx=Y(1,1)+Y(1,2)

jx=Y(1,1)+Y(1,2)

![]() jy=-Y(1,2)

jy=-Y(1,2)

![]() YL=Y(2,2)+Y(1,2)

YL=Y(2,2)+Y(1,2)

Measurement Expression 10E.4 Equations for the feedback parameters x, y, and YL

In these equations, jy is an inductor and YL and jx are capacitors. However, note that jx and jy are not pure imaginary numbers because the collector terminal of the transistor in Figure 10E.18 is not connected to a ground but, instead, to a 33-nH inductor. Also note that the real part of jx is the largest and the load is connected to the base rather than the collector terminal.

For the basic parallel-type oscillator shown in Figure 10E.21, put the ground point at the collector and then implement the oscillator circuit by adding a DC bias.

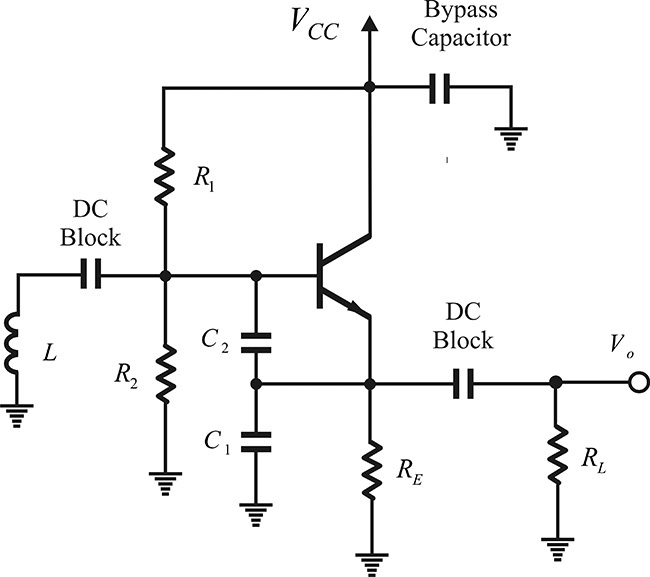

The oscillator circuit with the collector as a ground is called a Colpitts oscillator and it can be implemented as shown in Figure 10E.22.

The collector DC voltage is supplied through the bypass capacitor and the oscillation output is obtained from the emitter terminal. The DC voltage to the base is supplied using the bias resistors R1 and R2. Furthermore, a DC block capacitor is inserted between the inductor and base to prevent the base from being grounded. The emitter current of the BJT can then be set by the resistor RE. In addition, the DC block capacitor is necessary to prevent the appearance of DC voltage at the output. The inserted resistors should provide higher impedances than those of the components around them at the oscillation frequency so as not to affect the RF signal at that oscillation frequency. The common collector implementation is easy and is thus widely used. The Colpitts oscillator circuits of Figures 10E.12 and 10E.17 are a type of common-collector oscillator circuit. In particular, in order to reduce the impact of the emitter bias resistor, the RFC may be used, as shown in Figure 10E.12. It should be noted that because the DC block capacitors and the RFCs inserted for the DC bias can be made to satisfy the oscillation conditions at other undesired frequencies, the appropriate values of the capacitors and the RFCs should be chosen so as not to satisfy the oscillation conditions at undesired frequencies. Instead of the common collector, the ground can be set as the emitter or the base. However, these kinds of configurations are not widely used due to the complexity of their implementations.

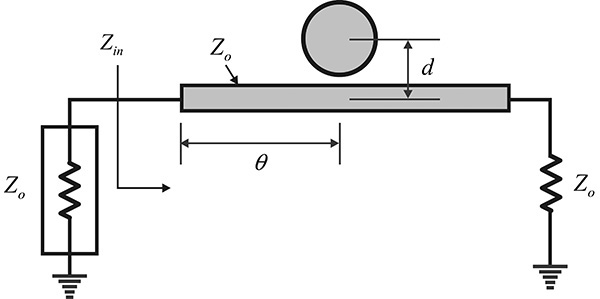

10.4.3 Design Method

Oscillator design from the impedance point of view is relatively simple; that is, the reference plane is set at the active part, which could be either Gunn or IMPATT diodes, and a series resonant load at the oscillation frequency is formed by adding a matching circuit to the 50-Ω load. The matching circuit must be designed such that the resistance looking into the load from the active part is smaller than the negative resistance of the active part. Alternatively, from the admittance point of view, a parallel resonant load is formed by adding a matching circuit to the 50-Ω load and the matching circuit must be designed such that the value of the parallel load is greater than the negative resistance of the active part.

The design concept from the impedance or admittance point of view can be similarly applied to the design of the series- or parallel-feedback-type oscillators. In the case of the series feedback type, the reference plane is set at the terminating reactance jx, as shown in Figure 10.36(a), and the active part is designed to satisfy the oscillation condition. For the purpose of simple design, the load ZL = RL + jXL is set as XL = 0, ZL = Zo, and the series feedback reactance jy that gives the appropriate negative resistance value can be found by varying jy. Now, denoting the impedance looking into the active part from the reference plane as Zin, the oscillation condition can be satisfied by setting the value of jx as x = –Im(Zin). Next, adding the DC bias circuits for the transistor completes the oscillator design. This design method is simple; however, when the gain of the transistor is not high, the negative resistance is not induced at the reference plane, which causes problems in oscillator design. In that case, the design can be accomplished by trial-and-error adjustment of the load impedance value ZL.

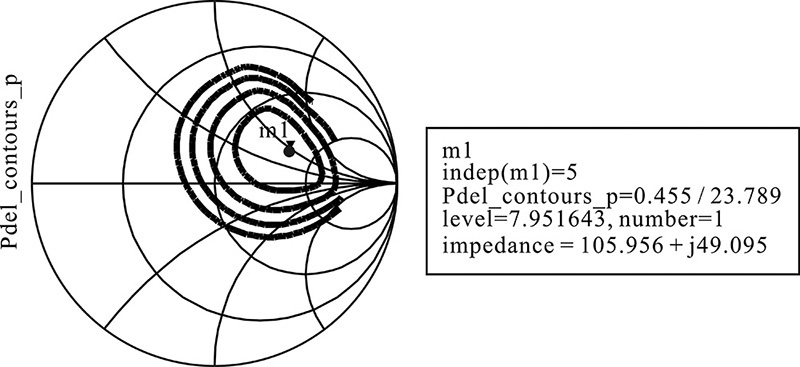

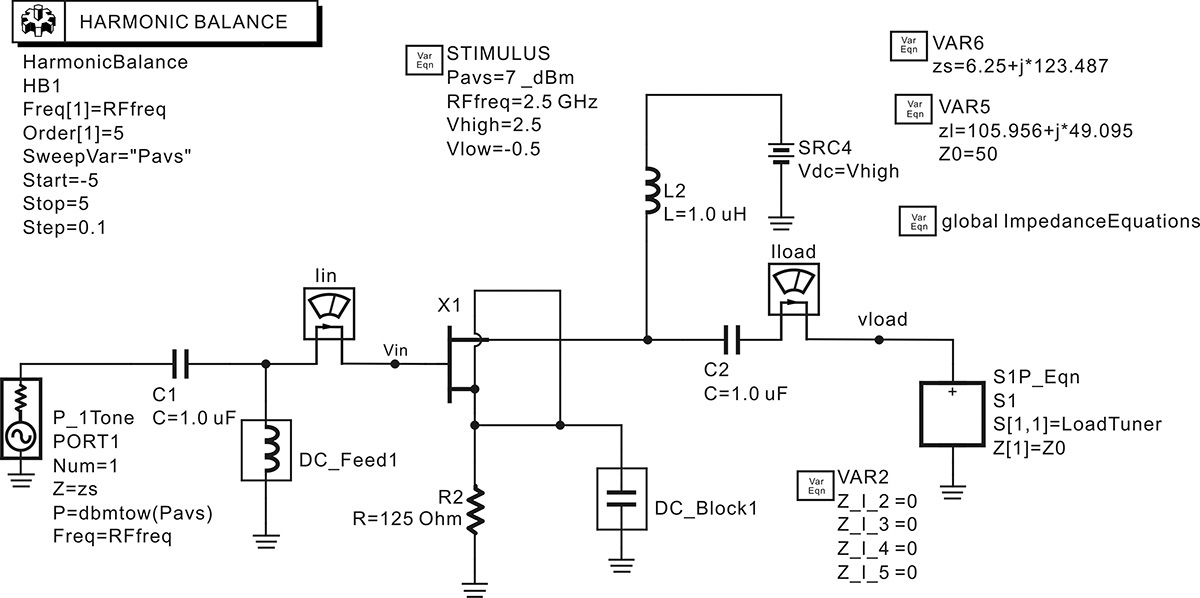

Figure 10.36 Design of a feedback-type oscillator: (a) jx reference plane and (b) load reference plane

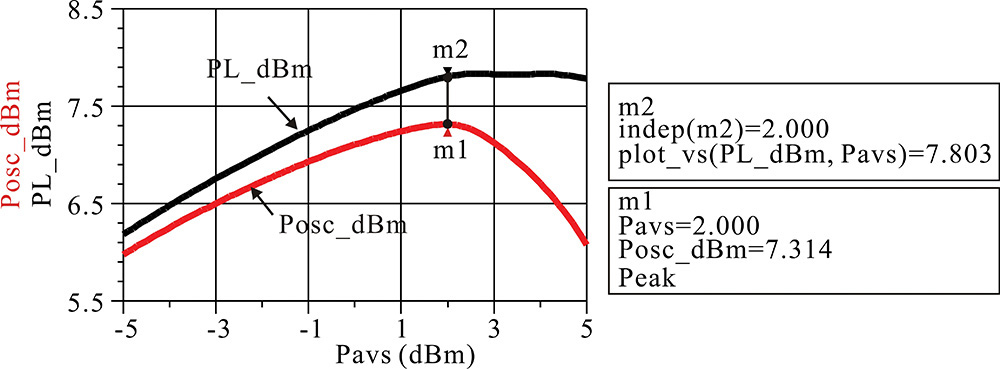

Alternatively, the reference plane is set at the load, as shown in Figure 10.36(b).6 In addition, the reactance pair jx and jy are set to make the real part of the impedance Zin seen from the load ZL negative. The selection of jx and jy is possible when the contour of the real part of Zin is plotted in the (x, y) plane. The method of plotting these contours can be found in Appendix E and, by using this method, the (x, y) values giving negative resistance can be selected. Thus, for the selected (x, y) values, the impedance Zin seen from the load ZL can be calculated. The suitable load ZL for this Zin can then be synthesized using a matching network to satisfy the oscillation conditions. The real part of the load ZL must be less than the negative resistance of Zin, and ZL + Zin must be also designed to be series resonant at the oscillation frequency. The basic form of the parallel oscillator can be designed using both the admittance condition and a method similar to the design of the series oscillator’s basic form. This approach will be presented in the following section that deals with design examples. The mobile communication VCO will be designed following this approach.

6. M. Maeda, K. Kimura, and H. Kodera, “Design and Performance of X-Band Oscillators with GaAs Schottky-Gate Field-Effect Transistors,” IEEE Transactions on Microwave Theory and Techniques 23, no. 8 (August, 1975): 661–667.

The oscillator design based on the previously explained one-port method can easily determine oscillation frequency, but the determination of the oscillation frequency alone is not enough in designing an oscillator with two-port devices such as a transistor. For example, it will be impossible to know whether the transistor in the oscillator is set to give maximum gain or is set to give maximum output power. The oscillator design based on the two-port method can provide an improved design even though it is more complex than the one-port method.7

7. M. Q. Lee, S. J. Yi, S. Nam, Y. K. Kwon, and K. W. Yeom, “High-Efficiency Harmonic Loaded Oscillator with Low Bias Using a Nonlinear Design Approach,” IEEE Transactions on Microwave Theory and Techniques, 47, no. 9 (September 1999): 1670–1679.

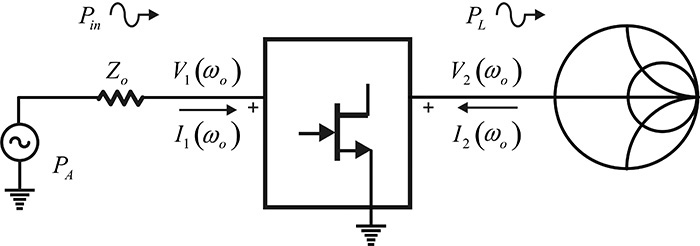

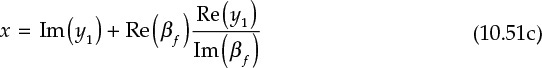

First, consider the transistor shown in Figure 10.37 in an amplifier. For a given input power, the load impedance can be determined by the load-pull previously described in the power amplifier design in Chapter 9. The load impedance can be determined for maximum efficiency or for maximum output power. Then, the input voltage and current V1 and I1, and the output voltage and current V2 and I2 can also be determined. Using voltages and currents V1, V2 and I1, I2, the feedback network that yields V1 and I1 from the voltage and current V2 and I2 can be designed. The designed feedback network with the amplifier will form an oscillator that yields the designed frequency and output power of Posc = PL - Pin. Since a part of the output power PL is fed back to supply input power Pin in the oscillator circuit, Posc becomes PL – Pin.

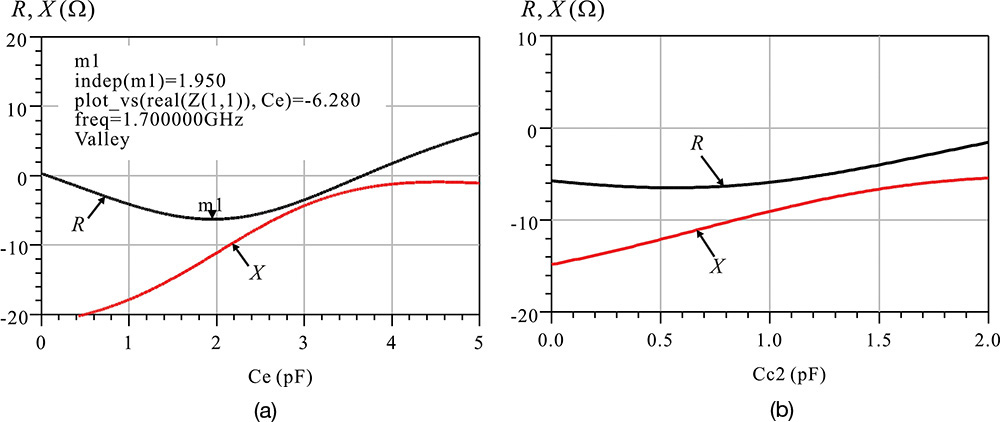

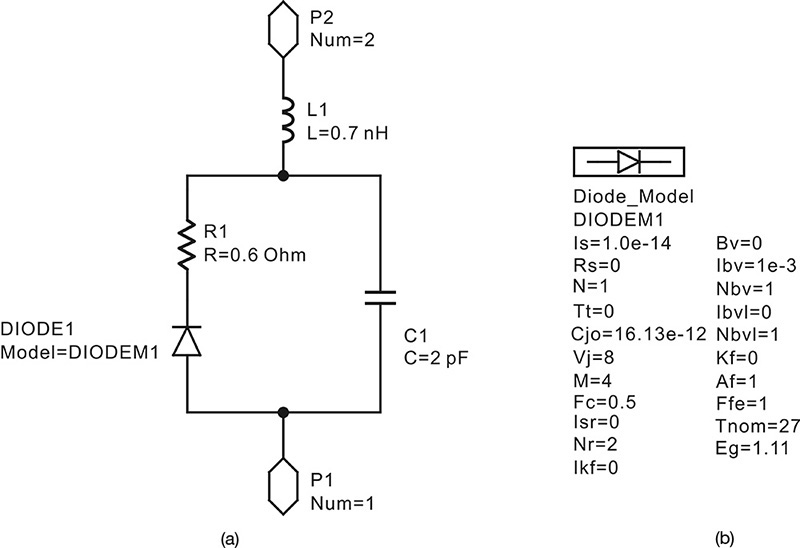

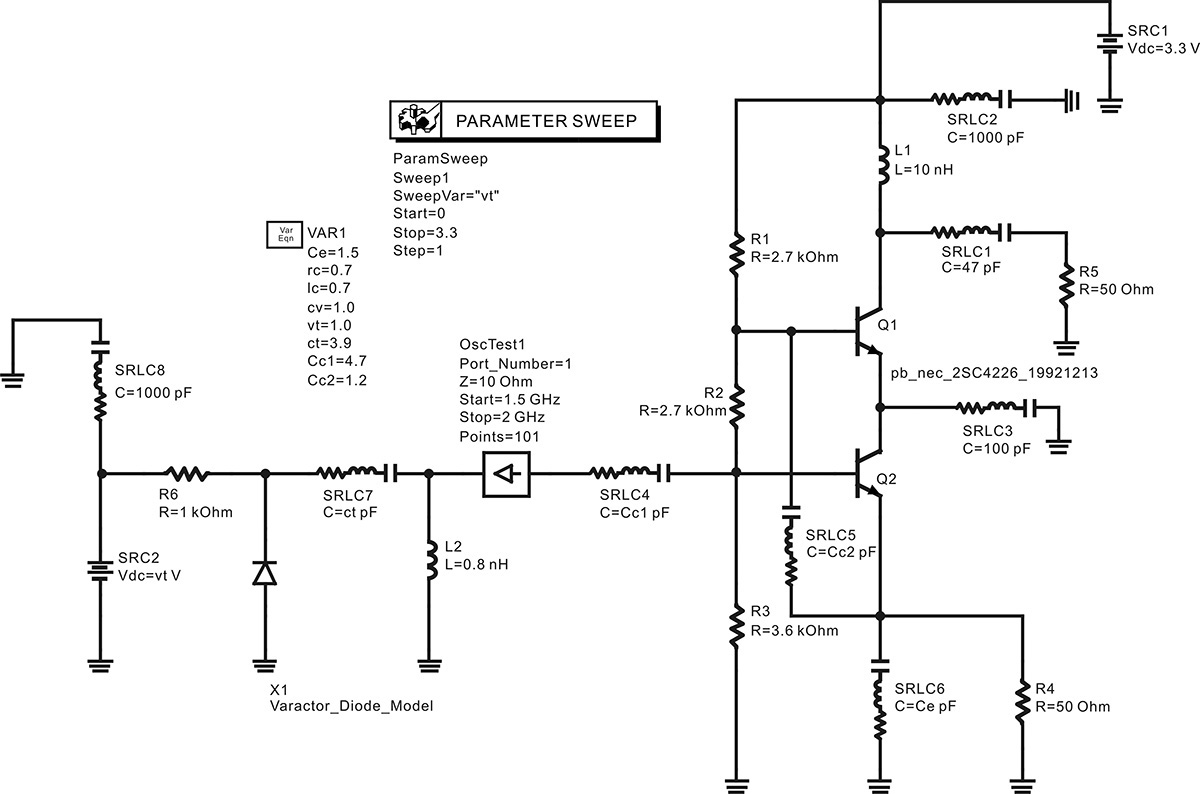

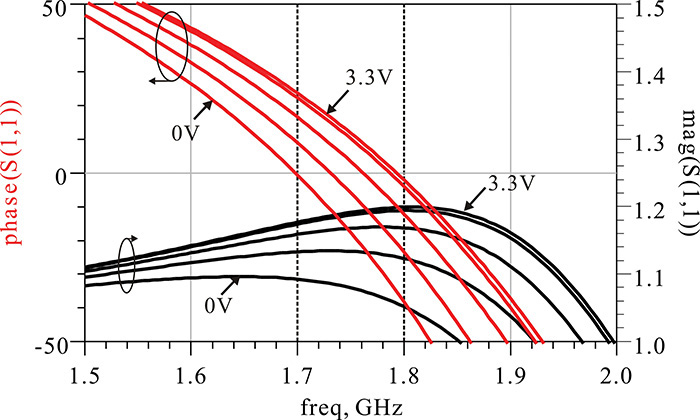

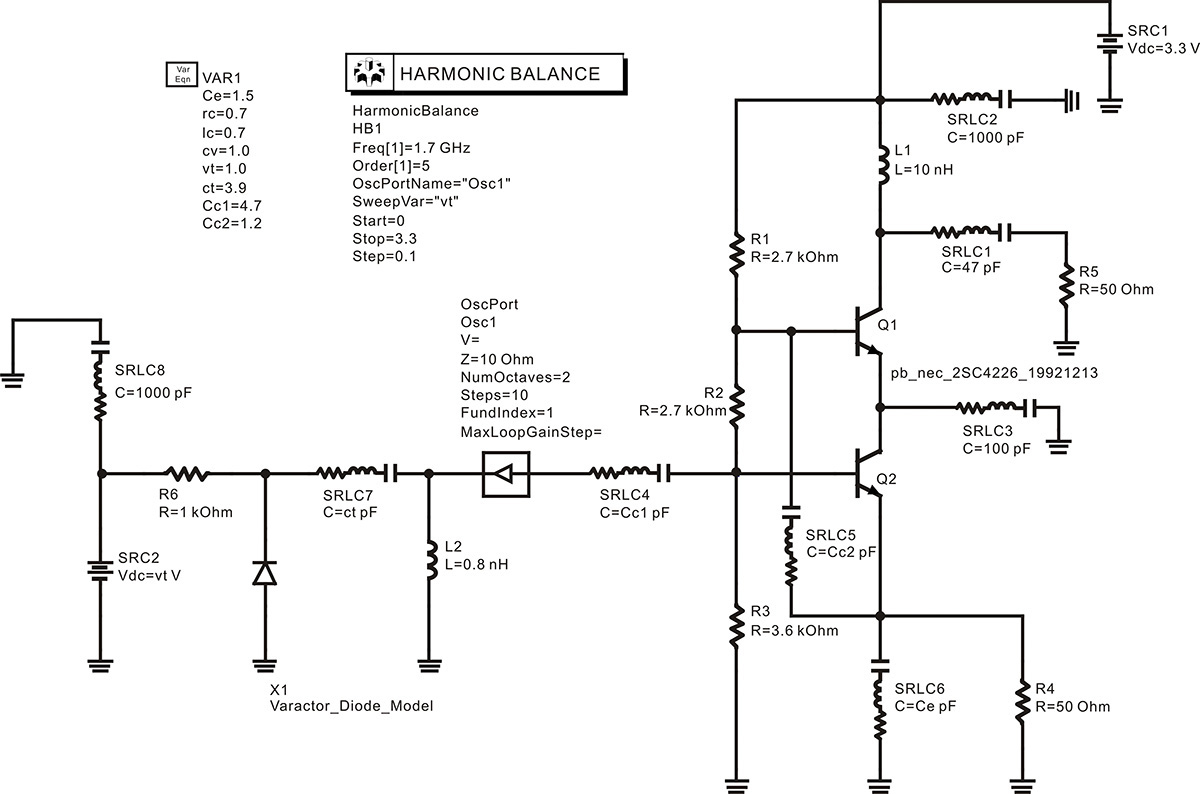

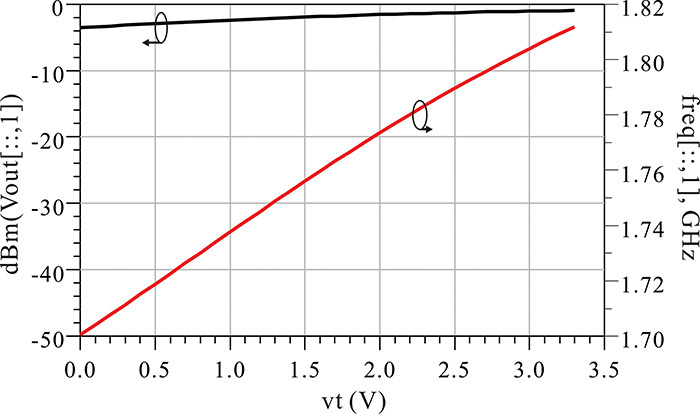

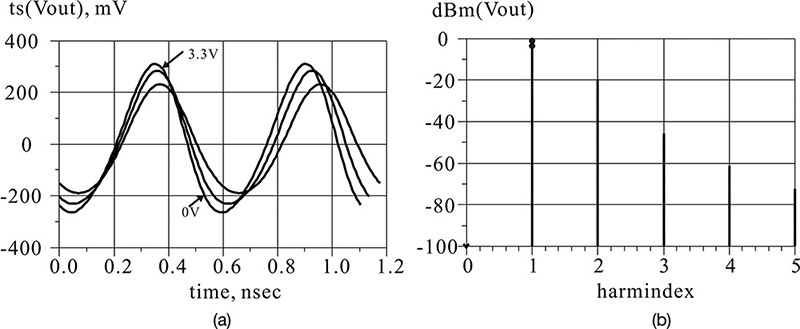

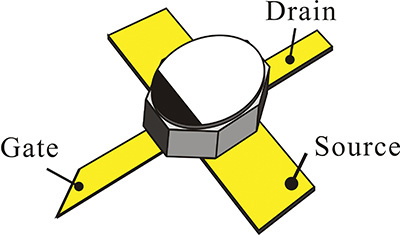

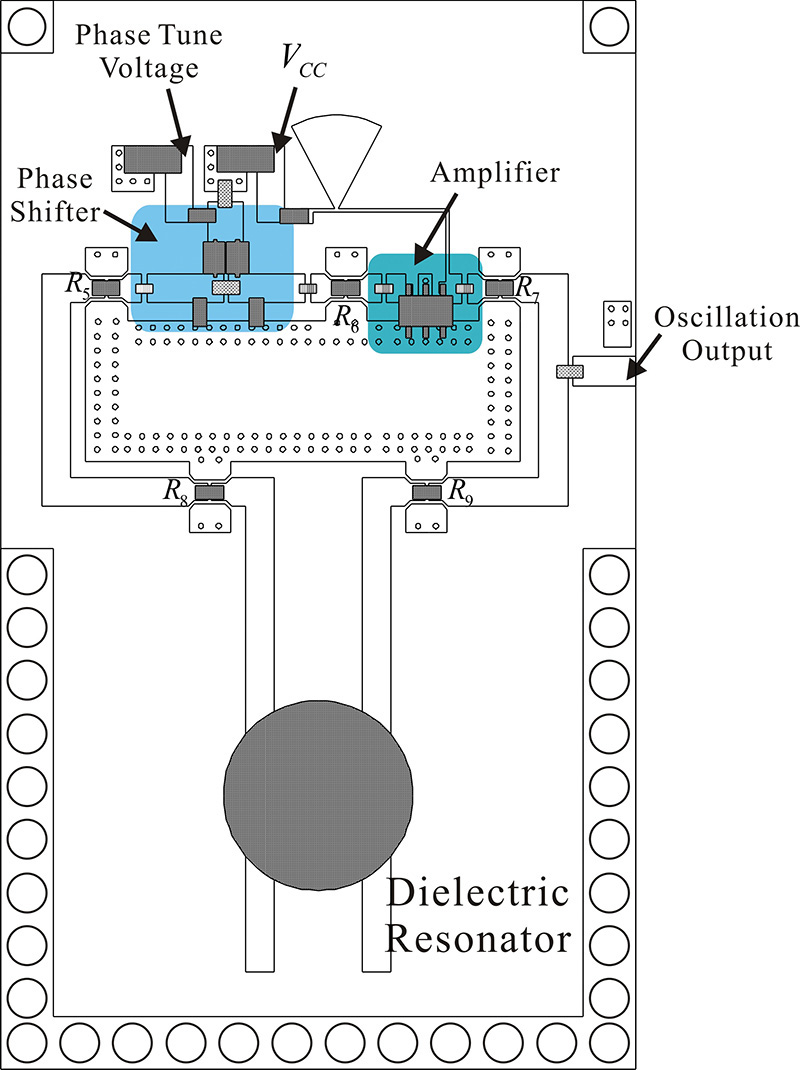

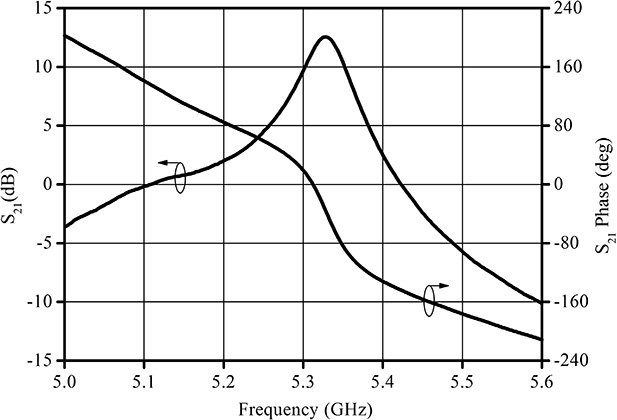

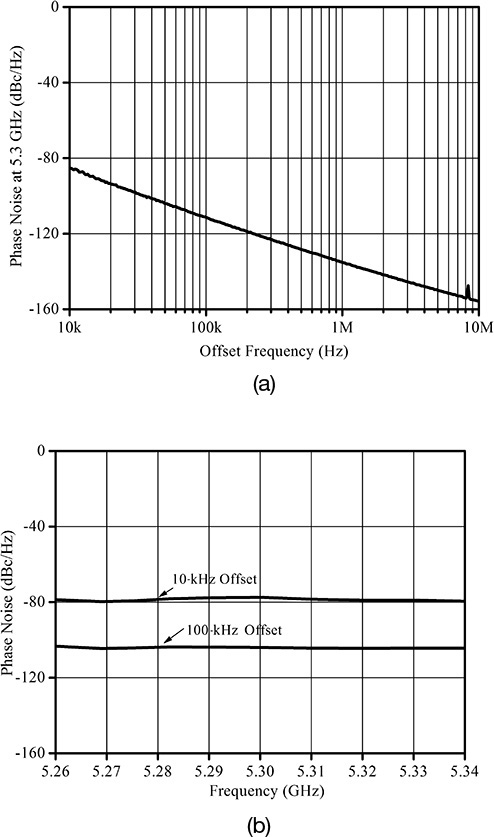

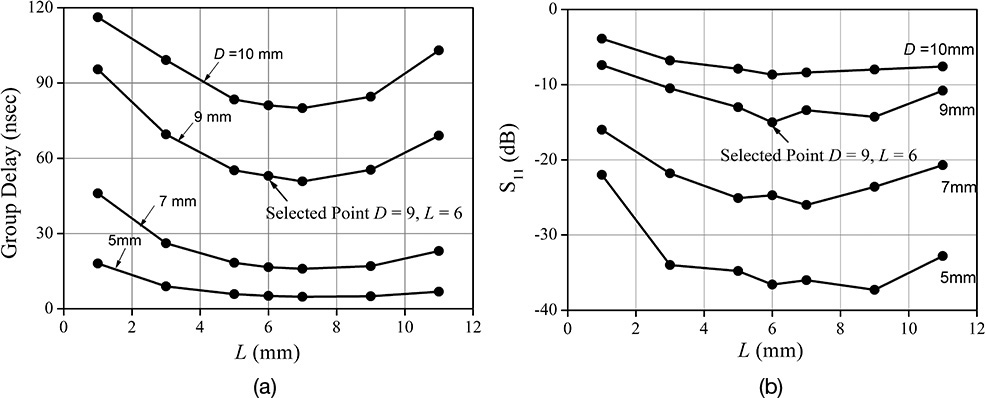

Figure 10.37 Determination of the input and output voltages and currents through the load-pull simulation