Chapter 9. Power Amplifiers

9.1 Introduction

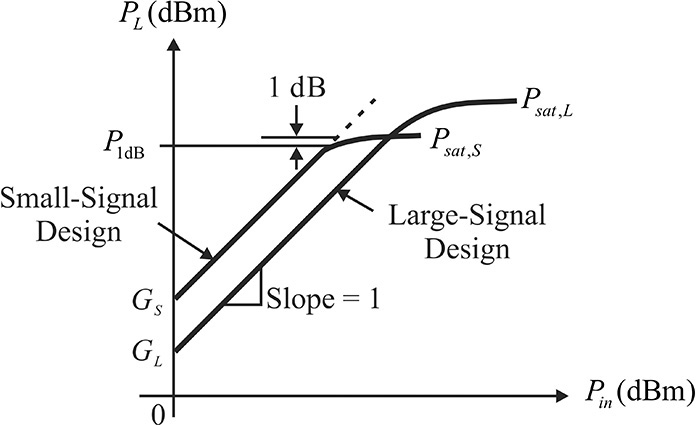

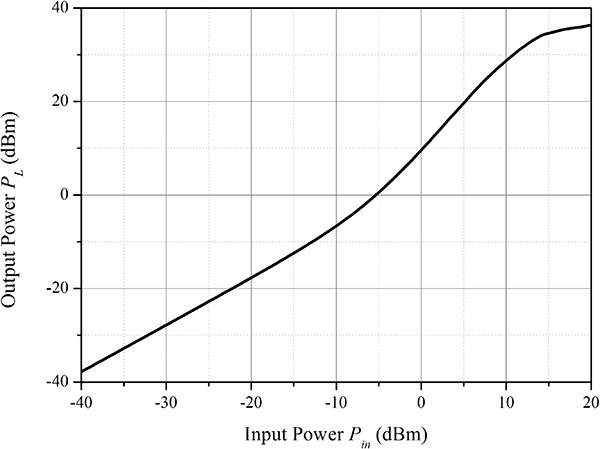

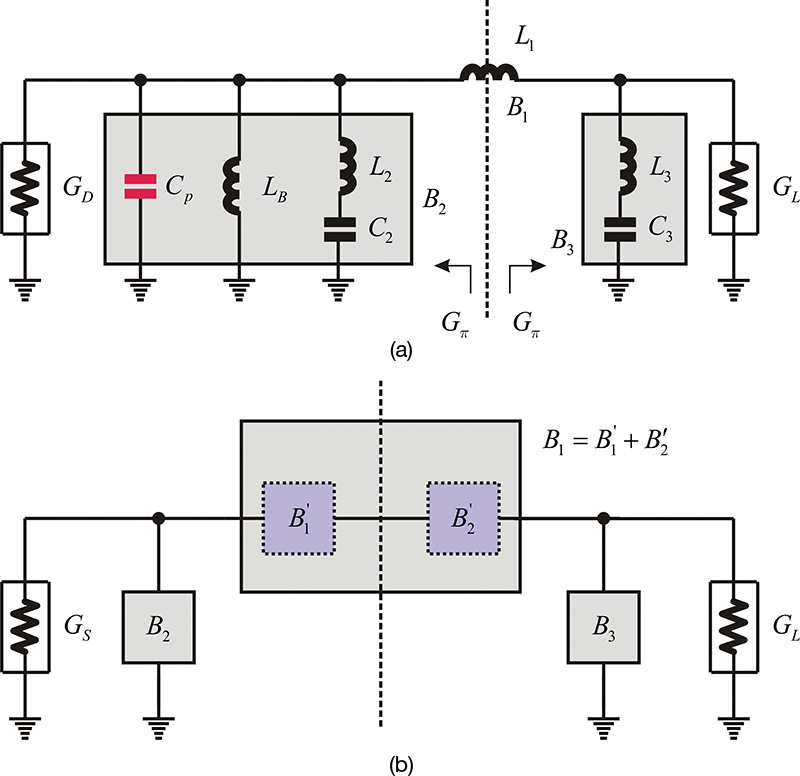

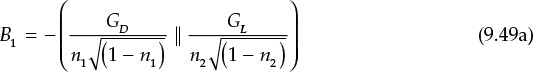

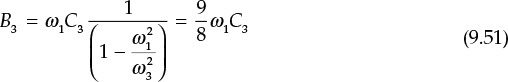

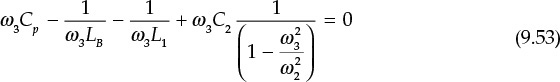

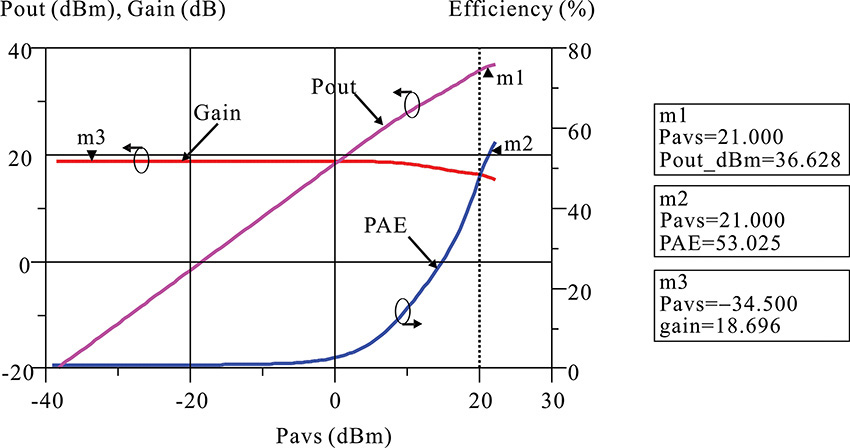

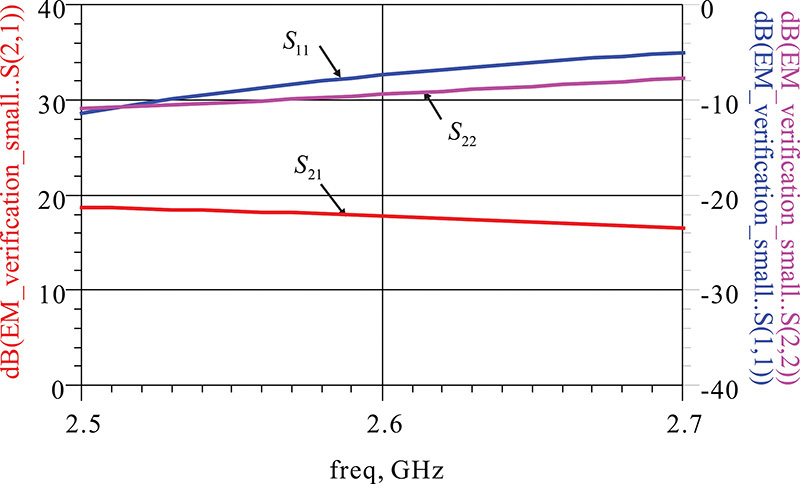

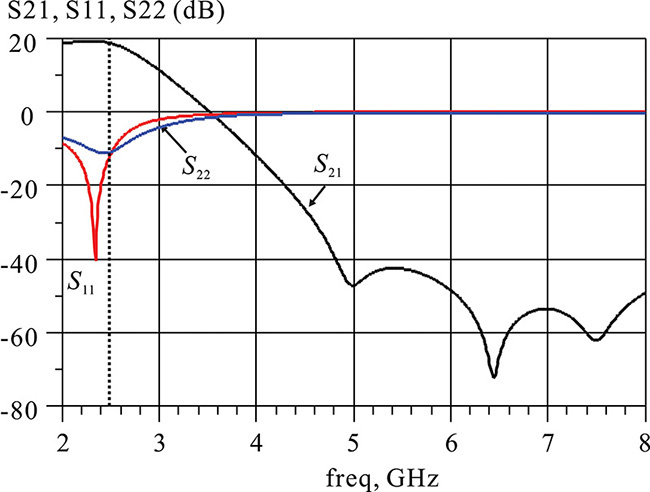

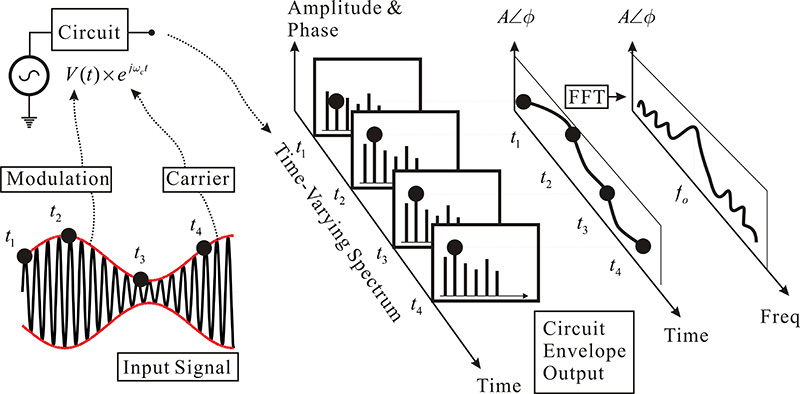

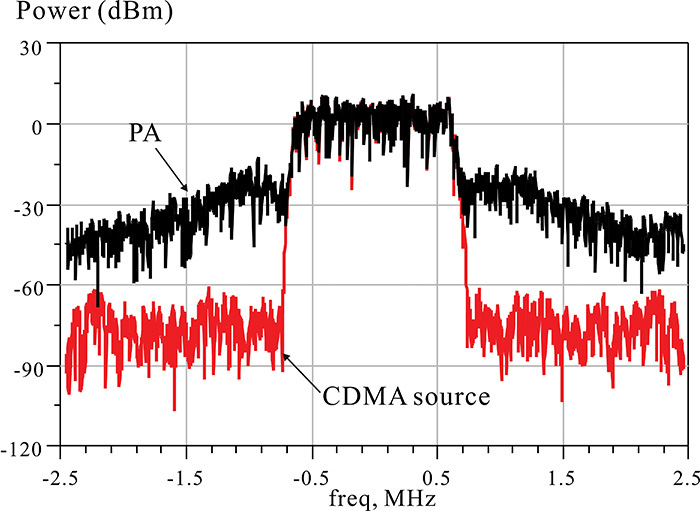

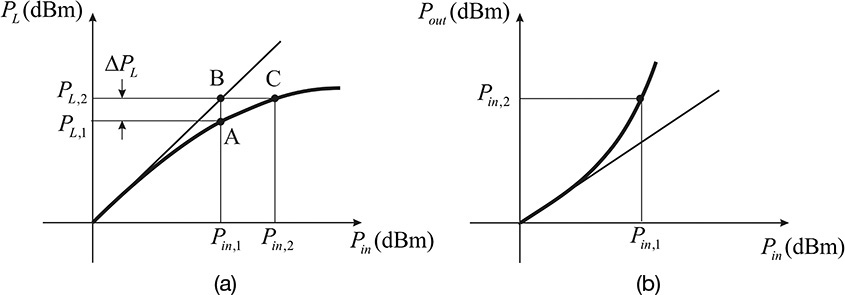

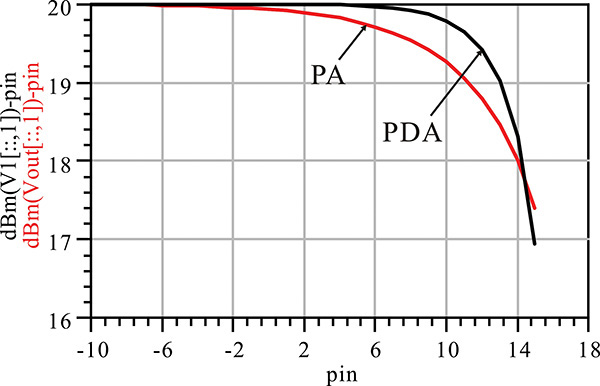

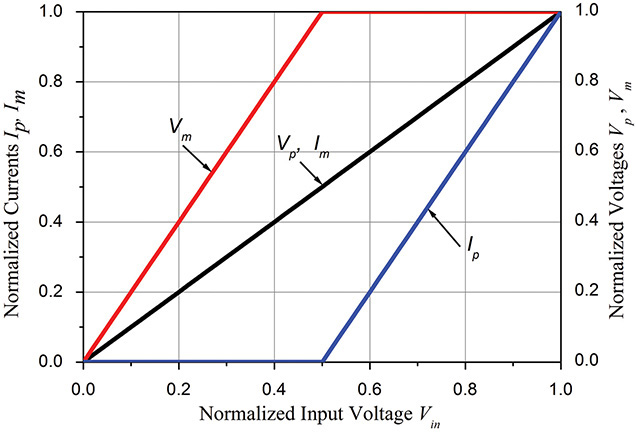

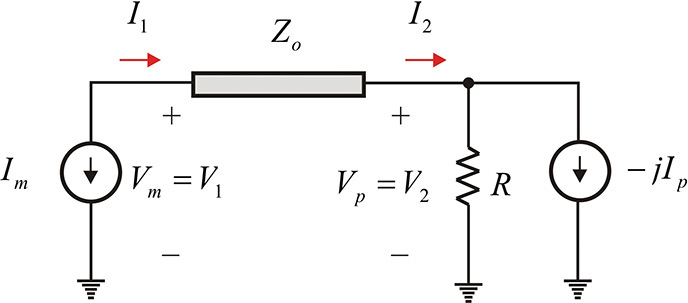

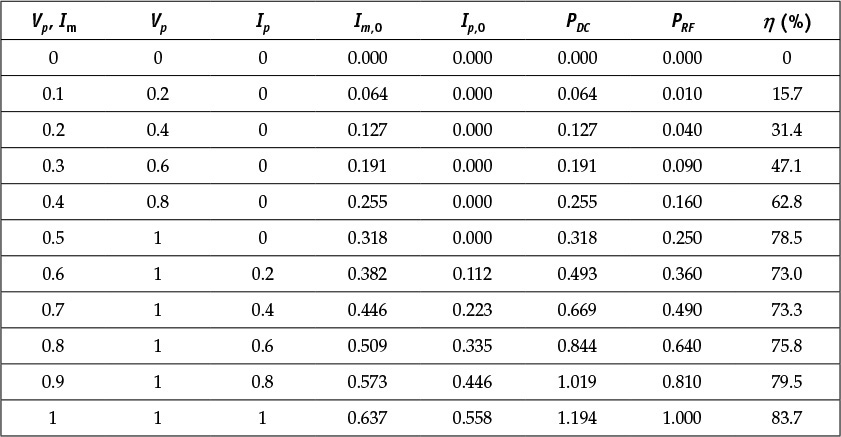

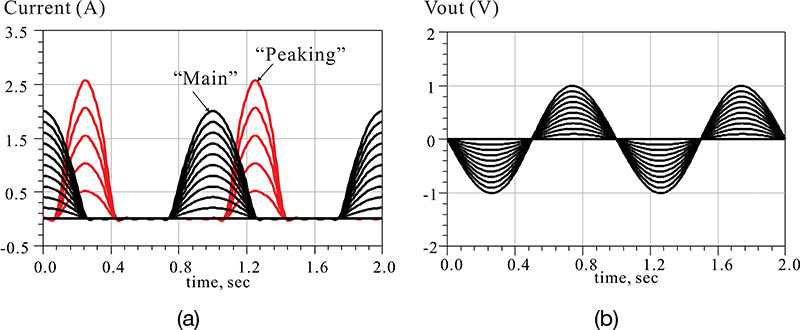

A power amplifier is generally located just before the antenna, and determines the transmitting power level of a communication system. The design of a power amplifier is significantly different from that of the low-noise amplifier presented in Chapter 8. To demonstrate the difference, suppose that two amplifiers are designed with the same active device; one is based on the small-signal design presented in Chapter 8 and has the maximum small-signal gain; the other produces the maximum output power based on the large-signal design that will be presented in this chapter. Figure 9.1 shows a plot of the delivered power PL of the two amplifiers versus the input power Pin.

Figure 9.1 Comparison of PL – Pin characteristics of low-noise and power amplifiers. The small-signal design has a higher gain GS than the gain GL of the large-signal design; however, the small-signal design saturates early at a lower input power than does the large-signal design.

As shown in Figure 9.1, at a low input power Pin, the output power PL increases in proportion to the input power. However, at a high input power, the output power shows a marginal increase. A further increase in the input power drives the output power of the amplifier into saturation. A point with a 1-dB deviation from the linear output power is referred to as the 1-dB compression point of an amplifier and the output power level at saturation is called the saturated power of an amplifier. As discussed in Chapter 8, an amplifier with maximum small-signal gain can be designed by selecting appropriate source and load impedances computed from the measured small-signal S-parameters at a given DC bias. The designed maximum small-signal gain amplifier generally gives a high gain but also has a lower 1-dB compression point and saturated power compared to an amplifier designed to give maximum output power as shown in Figure 9.1. This is not a special case but a general fact.

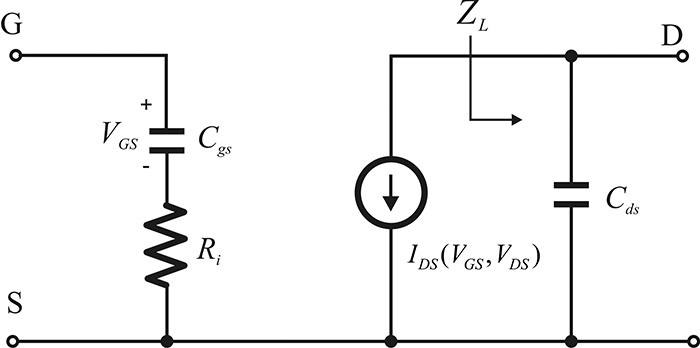

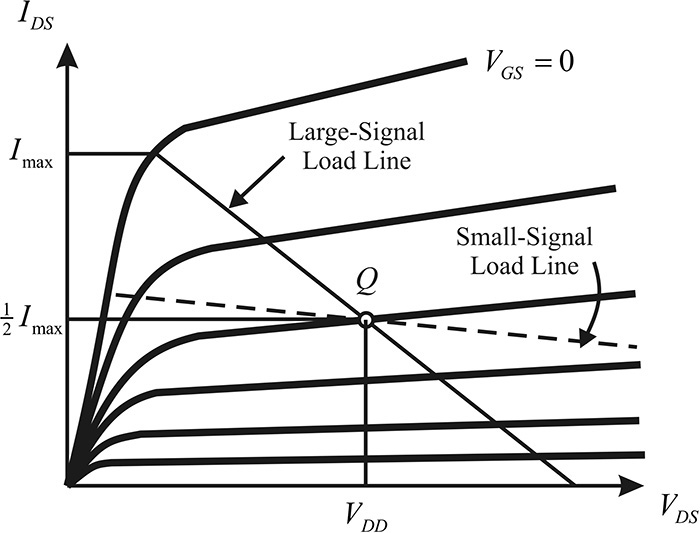

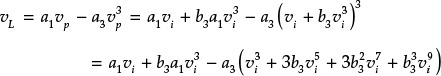

To explain this qualitatively, a simplified large-signal FET equivalent circuit is shown in Figure 9.2. Here, the current source IDS, which depends on the gate-source and drain-source voltages, has the characteristics shown in Figure 9.3. In addition, excluding the current source IDS, all the other elements in the equivalent circuit of Figure 9.2 are assumed to be linear elements since they typically have low nonlinearity.

Figure 9.2 Simplified large-signal FET equivalent circuit. Here, the current source IDS represents the DC IDS–VDS characteristics of an FET.

The maximum small-signal gain at the operating point Q can be achieved when the load is conjugate matched to the output impedance. Thus, the impedance ZL of Figure 9.2 must satisfy ZL = rDS = (∂IDS/∂VDS)–1. This causes the load line to have a slope of (rDS)–1, as shown in Figure 9.3. However, the load line that gives maximum output power is obviously the load line represented by the solid line in Figure 9.3. Since the gain is approximately proportional to gmRL, the gain of the amplifier based on the small-signal design is clearly higher than that based on the large-signal design. Yet the amplifier based on the small-signal design has a low saturated power and it generally reaches saturation early as shown in Figure 9.1. The small-signal design clearly does not exploit the maximum output power capability that the active device can supply.

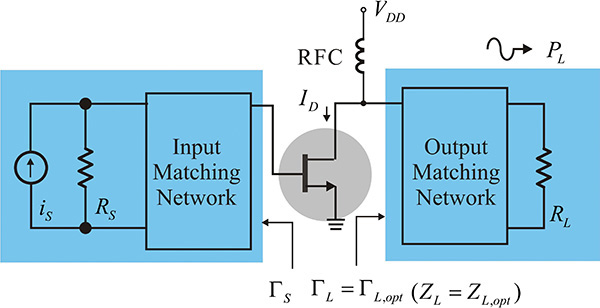

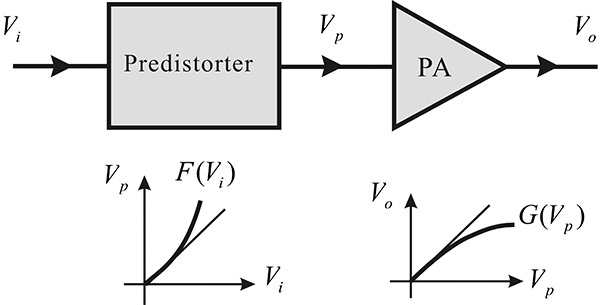

Figure 9.4 shows a power amplifier configuration. The power amplifier can be represented by a block diagram that is similar to a low-noise amplifier. Therefore, the source and load reflection coefficients ΓS and ΓL,opt must be determined by experimental or theoretical means in order to design the power amplifier. When ΓS and ΓL,opt have been determined, the matching circuit can be constructed similar to that of the low-noise amplifier design. The slight difference between the power amplifier and the low-noise amplifier designs is that the input matching circuit losses must be minimized in the case of the low-noise amplifier design, whereas in the power amplifier design, it is the output matching circuit losses that must be minimized. The input matching circuit losses in the low-noise amplifier are directly associated with noise-figure degradation. By denoting the loss at the input matching circuit as L(dB) and the noise figure of the active device as F(dB), then the noise figure of the low-noise amplifier as explained in Chapter 4 is approximately given by L + F(dB). Thus, for a minimum noise figure, the input matching circuit must be constructed so as to have minimum losses. On the other hand, because the loss in the output matching circuit is directly related to the loss in the output power, the loss in a given output matching circuit must be minimized in the case of the power amplifier.

Figure 9.4 Power amplifier block diagram and its design concept. ΓL,opt is chosen for optimum output power and then ΓS is determined for the chosen ΓL,opt for conjugate matching at the input.

The impedance ZL,opt in Figure 9.4 that gives maximum output power can easily be inferred from the DC characteristics in Figure 9.3 at low frequency; however, at high frequency, due to the complexity of the equivalent circuit of the active device and the parasitic elements of its package, it is not easy to derive ZL,opt analytically. In a case where the large-signal equivalent circuit is known, the optimum impedance ZL,opt can be obtained at the reference plane of the current source IDS in Figure 9.2. Using ZL,opt, the optimum impedance at the output terminals of the package can also be obtained by taking the external parasitic elements into consideration. However, unlike at low frequency, the reference plane of the current source IDS in the large-signal equivalent circuit is generally not obvious at high frequency. Thus, ZL,opt is usually determined experimentally through a load-pull measurement or with simulation; that is, load-pull simulation using software when the large-signal model is available. We will cover the determination of ZL,opt using load-pull measurement and simulation in this chapter.

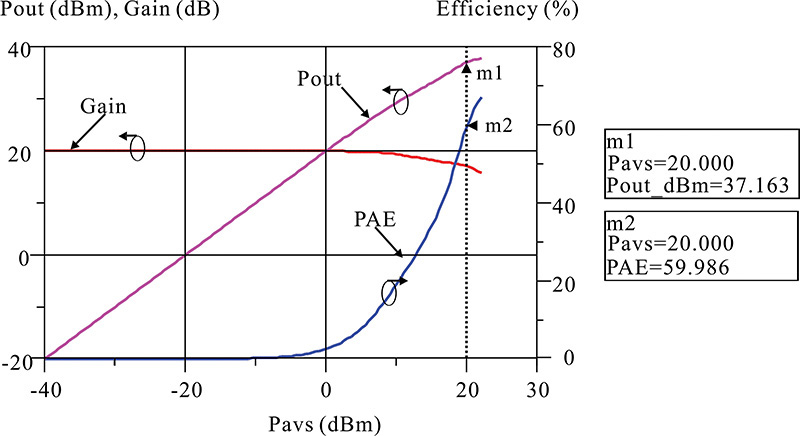

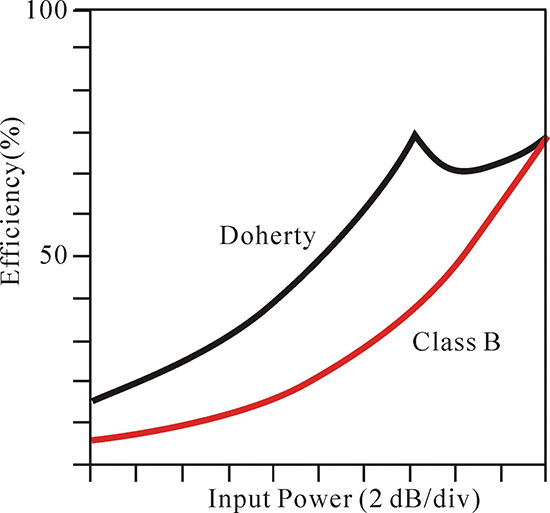

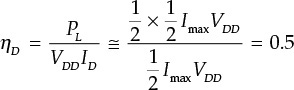

The next important issue in the implementation of a power amplifier is efficiency, which can be expressed in terms of RF output power for a given supplied DC power, and two definitions are widely used. The first is the collector or drain efficiency. Denoting the DC power consumed in the output terminal as PDC and the RF output delivered to the load as PL, the drain efficiency ηD is defined as shown in Equation (9.1).

Here, VDD represents the DC supply voltage and ID is the DC supply current when the delivered power to the load at RF is PL. To some extent, the drain efficiency may be a good measure for representing the efficiency of an amplifier when the amplifier gain is sufficiently high; however, the gain is usually not high enough at a high frequency. Consequently, the input power Pin must be considered in the definition of the efficiency. In general, PAE (power-added efficiency) is used in the definition of efficiency at a high frequency and it is defined in Equation (9.2).

This definition of PAE can be interpreted as the ratio of the output power added by the active device to the DC power supplied to the active device.

Given that VDD = 5.8 V, ID = 400 mA, Pin = 23 dBm, and Pout = 33 dBm, determine the drain efficiency and the PAE.

Solution

Since 33 dBm corresponds to 2 W, the drain efficiency is

An input power of 23 dBm corresponds to 0.2 W; therefore the PAE is

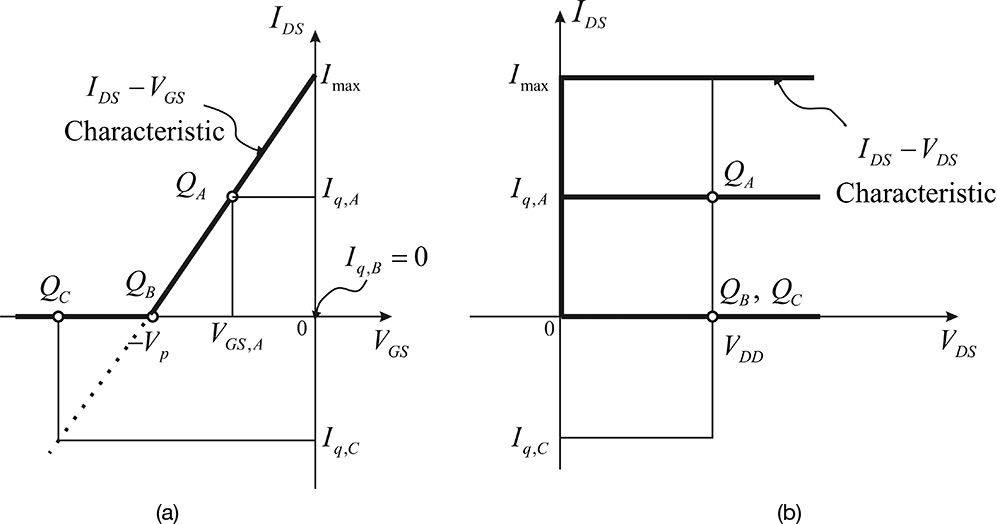

The DC biased amplifier shown in Figure 9.3 is usually classified as a class-A amplifier; the problem with this type of amplifier is that its maximum efficiency does not exceed 50%; that is, for the maximum output as shown in Figure 9.3, the approximate drain efficiency can be seen to be

In order to understand the efficiency problem in a class-A amplifier, consider an example of this amplifier with a 20 W RF output power. Even if its efficiency is given as the maximum value of 50%, out of the total 40 W power supplied, 20 W is consumed while 20 W is delivered to the load. This will be more problematic in the absence of any RF input power. The total supplied DC power of 40 W to the active device would be consumed by that device in the absence of the RF input power, and all the supplied DC power would be converted into heat. Therefore, power consumption of the class-A amplifier is most problematic in the case where there is no RF input power. This problem can be solved by changing the active device’s operation and there are various operation techniques for improving efficiency, which we will discuss in the next sections. However, designing the amplifier to improve its efficiency generally gives rise to the problem of distortion. Therefore, for a communication system that employs both amplitude- and phase-modulated signals, it is necessary to reduce the distortion to improve the amplifier’s linearity. The methods for improving linearity will also be explained in this chapter.

9.2 Active Devices for Power Amplifiers

Microwave active devices have already been discussed in Chapter 5. Of these, pHEMTs and HBTs were noted as having excellent high-frequency characteristics. To employ these devices in power amplifiers, their structures must be expanded to handle a large output power. They can be used as power devices by expanding the gate width in the case of a pHEMT or the emitter area in the case of an HBT. This will increase their output power capability, but their breakdown voltage is basically low, which limits their application as high-power devices. In addition to these devices, there are other types of high-power active devices that are widely used today. Among these, GaN (gallium nitride) HEMTs and LDMOSFETs (laterally diffused MOSFETs), simply referred to as LDMOS, have attracted a lot of attention as active devices for power amplifiers, and they will also be introduced in this chapter.

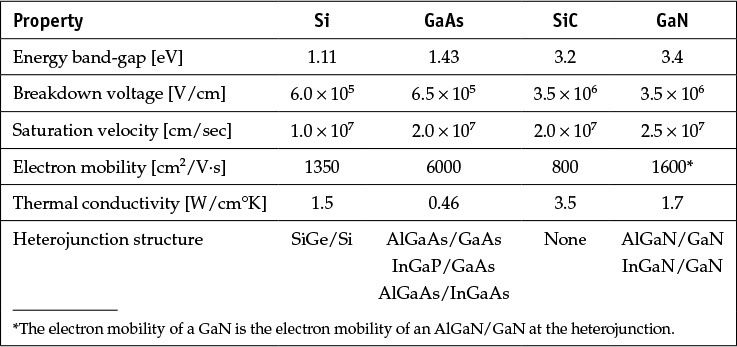

9.2.1 GaN HEMT

The important parameters of semiconductor properties for a high-power active device are electron mobility, energy band-gap (band-gap), and thermal conductivity. Among these parameters, electron mobility can be used as a criterion to estimate the high-frequency applicability of an active device fabricated using a given semiconductor process. In other words, for two active devices fabricated using the same processing method but on different semiconductors, the active device using the semiconductor with a higher electron mobility generally yields a higher gain and it can be used in applications up to higher frequencies in contrast to a semiconductor with a lower electron mobility. Thermal conductivity is an important parameter of semiconductor properties for power amplifier application. The higher the thermal conductivity, the greater the advantage is in heat dissipation. A device fabricated with a higher thermal conductivity will have a higher power consumption capability. The energy band-gap, which is simply referred to as the band-gap parameter, is closely related to the breakdown voltage of an active device. The larger the band-gap is, the higher the breakdown voltage will be. Thus, the higher band-gap semiconductor is advantageous in the fabrication of power devices.

The energy band-gap is defined as the difference in energy between the conduction band and the valence band. Thus, a higher-energy band-gap means the valence-band electrons can seldom move into the conduction band because those electrons require energy sufficiently higher than the energy band-gap to move into the conduction band. On the other hand, when the energy band-gap is low, the valence-band electrons can easily move into the conduction band as they can readily attain the required energy. The energy band-gap is thus an important measure for estimating the breakdown voltage of an active device for a given semiconductor material. The breakdown voltage refers to drain or collector voltages where the drain or collector current increases very rapidly. Therefore, the useful range of an active device’s drain voltage is usually limited by the breakdown voltage.

The phenomenon of breakdown can be explained using electron collisions. The electrons accelerated by an applied drain voltage collide with atoms at the drain, thereby generating electrons. When a drain voltage higher than the breakdown voltage is applied, the generated electrons thus attain sufficient energy to move into the conduction band and contribute to the drain current. As a result, the drain current increases rapidly due to the contribution of electrons generated by the collision. However, when the energy band-gap is high, the electrons generated by the collision with the accelerated electrons cannot attain sufficient energy to move into the conduction band. Thus, a high-energy band-gap semiconductor is typically associated with a high breakdown voltage. Due to this fact, when an active device is fabricated with a high-energy band-gap semiconductor, the active device shows a high breakdown voltage; a high DC bias voltage can then be applied and a large output power will be obtained. Therefore, a high-energy band-gap semiconductor is suitable for use as a high-power active device.

Thermal conductivity represents a material’s ability to conduct heat. A higher thermal conductivity means the heat generated in an active device due to power consumption is easily dissipated. As we have seen previously, no matter how well a power amplifier is designed, a portion of the supplied power is consumed as heat. The heat generated increases the temperature of the active device, which can damage the device if the heat exceeds the absolute maximum temperature for the device. A well-designed heat-dissipation structure such as a heat sink may help an active device endure a certain temperature increase, but the amount of heat dissipated will be fundamentally limited by the thermal conductivity of a given semiconductor. Therefore, thermal conductivity is an important parameter for the semiconductor materials used in power amplifiers.

The physical properties of various semiconductors are shown in Table 9.1. In that table, SiC and GaN have an excellent thermal conductivity compared with Si. Because the thermal conductivity of Si is comparable to that of a metal, SiC and GaN semiconductors are known to have a fairly good thermal conductivity. In contrast, GaAs has a lower thermal conductivity than Si by a factor of about one third. Thus, in terms of thermal conductivity, Si, GaN, and SiC semiconductors are suitable for the fabrication of active devices for a power amplifier. Next, in terms of an energy band-gap, SiC and GaN have a higher energy band-gap than Si by a factor of about 3. As a result, the fabricated active devices that use SiC and GaN show a breakdown voltage 3 times higher than that of Si. As a direct measure of breakdown voltage, the breakdown voltage in Table 9.1 is directly related to the breakdown voltage that is approximately 6 times larger in SiC and GaN compared to Si. Thus, a high DC supply voltage is possible with SiC and GaN, which leads to an increase in output power capability.

Therefore, it can be seen that SiC and GaN are suitable semiconductors for a power amplifier’s active devices, considering their thermal conductivity and energy band-gap. However, the electron mobility of SiC is lower compared to that of Si, and thus SiC active devices are inferior to Si active devices in high-frequency applications. Fortunately, the electron mobility in GaN depends on the condition of the heterojunction formation and this mobility can be made to exceed that in Si by using the heterojunction. An active device suitable for a high-frequency power amplifier can therefore be fabricated using a GaN process. Despite the GaN advantages, the late emergence of GaN devices is due to the lack of a suitable substrate for GaN growth. Recently, the technology for epitaxial-layer growth of GaN on SiC has seen significant advances, and the study of GaN-active devices continues to attract great interest.

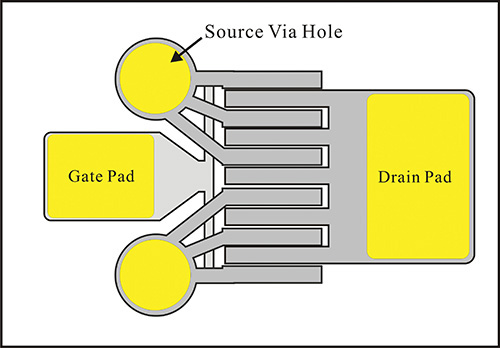

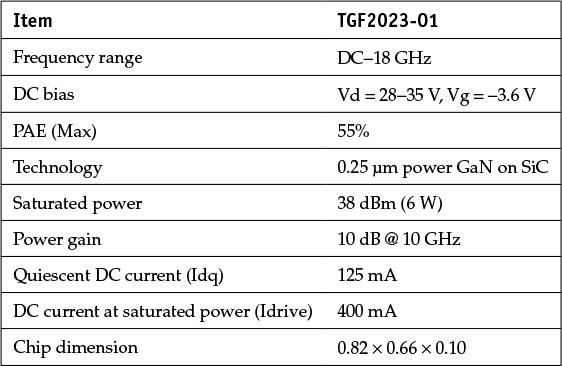

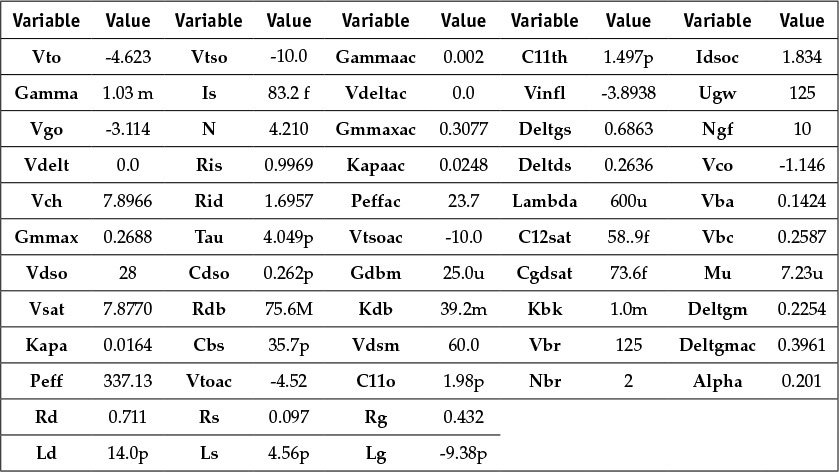

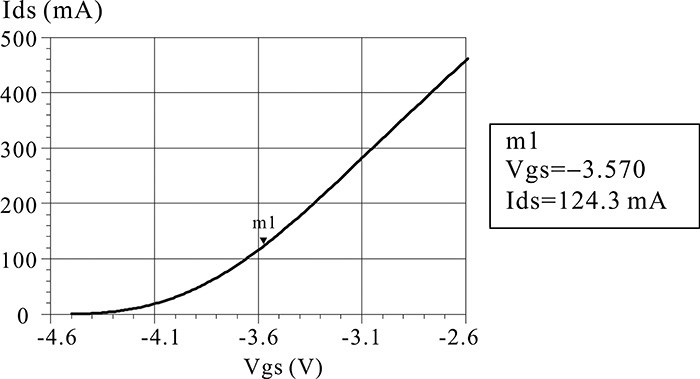

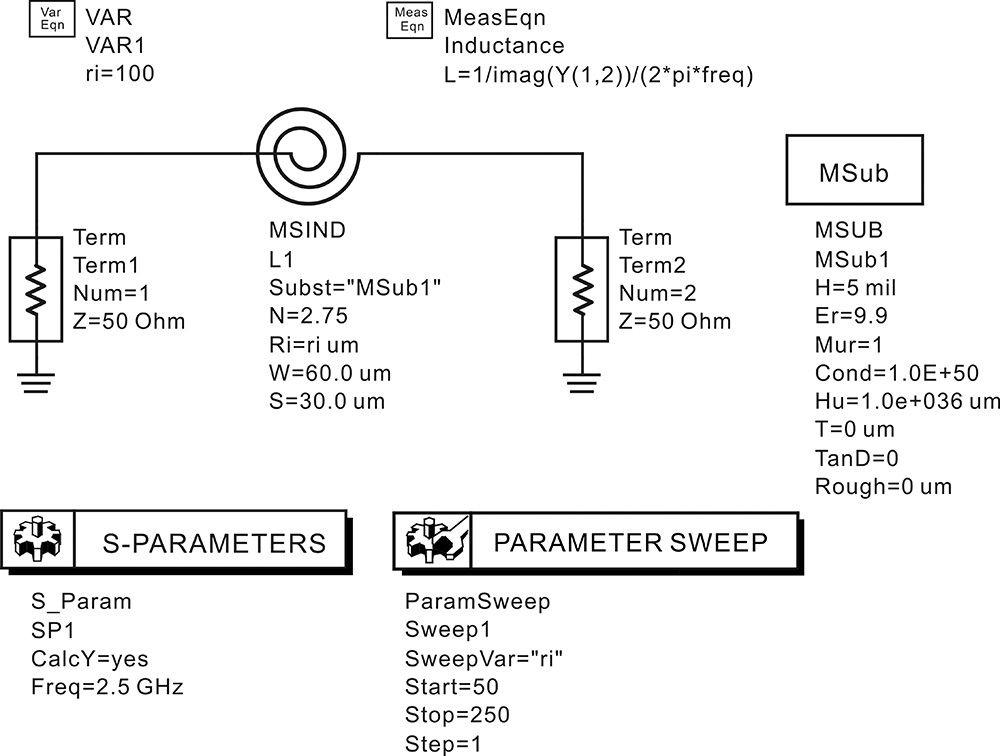

Figure 9.5 shows the structure of a GaN HEMT formed on SiC. The reason for selecting an HEMT structure is primarily related to the electron mobility of GaN. As this mobility is not much superior to that of Si, its maximum exploitation is required. By employing an HEMT structure, maximum electron mobility can be obtained because that mobility in the channel can be achieved in the absence of impurities, as discussed in Chapter 5. The frequency characteristics of GaN active devices can therefore be improved although the electron mobility of GaN is not greatly superior to that of Si.

Figure 9.5 Structure of a GaN HEMT. To reduce the gate metallization resistance and gate length, a T-shaped gate metallization is used. An AlGaN/GaN heterojunction is formed for the maximum exploitation of the electron mobility of GaN.

In Figure 9.5, an intrinsic GaN epitaxial layer is grown on SiC, on top of which an n–type AlGaN layer is formed for the heterojunction. The electron well created by the heterojunction is formed in the epitaxial layer of the intrinsic GaN, and the doped electrons in the AlGaN are collected in the electron well and thus move through a channel free from impurity atoms. Therefore, great improvement in the frequency characteristics is possible. The T-shaped gate terminal on the n–AlGaN layer in Figure 9.5 minimizes the resistance of the gate terminal and decreases the gate length, and thus improves the frequency characteristics. Note that the drain and source terminals are formed on the n+ GaN layer for ohmic contact.

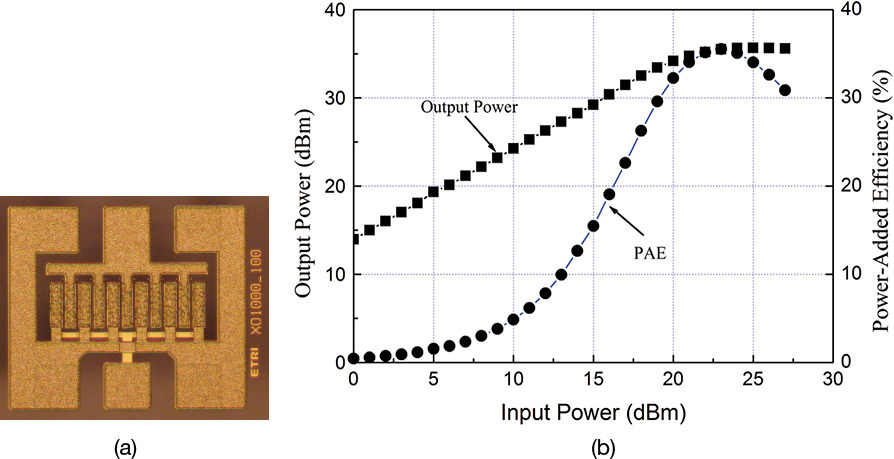

Figure 9.6(a) is a photograph of a GaN HEMT. The breakdown drain voltage VDS is reported to be 142 V. This is an advantage that results from the physical properties of a GaN semiconductor. Figure 9.6(b) shows the measured output characteristics of the GaN HEMT at a frequency of 9.3 GHz. The device shows a gain of about 14 dB, and a saturated power of about 35.7 dBm. The PAE is found to be about 40% at 35.7 dBm. The output power per unit gate width is estimated to be 3.7 W/mm.

Figure 9.6 (a) Photograph of a GaN HEMT XO1000_100. The gate length and width are 0.25 μm and 1000 μm, respectively. The back side is polished to a thickness of 100 μm. (b) Output power characteristics are at 9.3 GHz. Source: (private communication): ETRI IT Convergence and Component Technology Research Section, 218 Gajeongro Yuseonggu, Daejeon, 305-700, Korea, www.etri.re.kr/kor/main/main.etri.

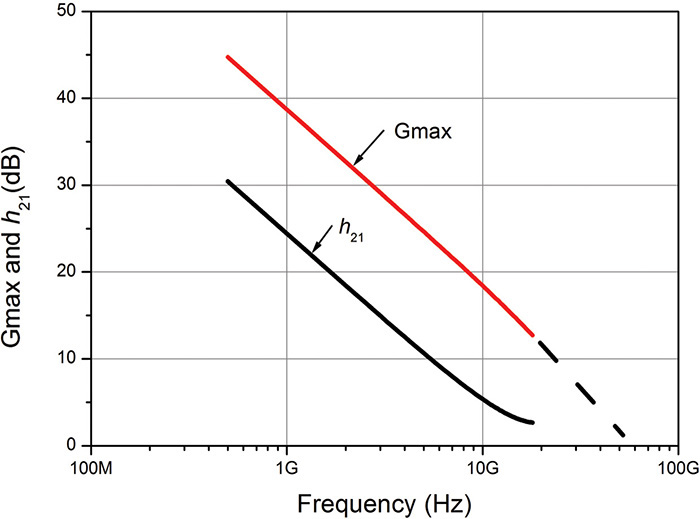

The frequency characteristics of a 0.25-μm GaN HEMT from Cree, Inc., are shown in Figure 9.7. In that figure, the frequency fmax is approximately 50 GHz where the maximum power gain U in Chapter 8 is 1. The frequency fT is near 20 GHz where the short-circuit current gain h21 is 1. The fmax and fT are comparable to the frequency characteristics of a GaAs MESFET. Considering the performances given in Figures 9.6 and 9.7, which were obtained from the initial stages of the GaN process, significant improvements are expected in the future.

Figure 9.7 GaN HEMT frequency characteristics (refer to the datasheet).1

1. Cree, Inc., datasheet, CGHV1J006D (the S-parameters are at VDS = 40 V, IDS = 60 mA); available at www.cree.com/RF/Products/General-Purpose-Broadband-40-V/Discrete-Bare-Die/CGHV1J006.

9.2.2 LDMOSFET

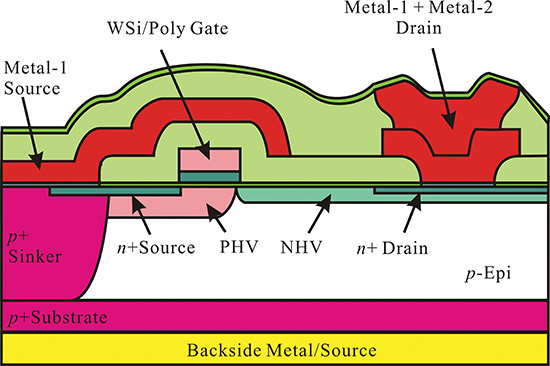

An LDMOSFET (laterally diffused MOSFET) is an active power device fabricated using Si process technology and it has a structure designed to improve the breakdown voltage of an MOSFET. As explained earlier, the channel electrons attain sufficient energy at a high drain voltage VDS and they collide with the atoms in the drain region with high impurity doping for ohmic contact. Numerous electrons are generated due to the collision and these electrons gain the energy sufficient to move into the conduction band taking the relatively small Si band-gap energy into consideration. Thus, there is a sudden increase in the drain current and, as a result, the lower breakdown voltage appears. This lower breakdown voltage can be improved by adjusting a doping profile in the drain region.

Figure 9.8 shows a cross-section of the LDMOSFET. In that figure, the drain region is laterally divided into a lightly doped region (NHV) and highly doped region (n + Drain) for the ohmic contact. In addition, the drain terminal is located at a considerable distance from the channel, which causes the accelerated electrons in the channel to primarily collide in the drain region with a low impurity concentration; as a consequence, the electrons lose energy when they reach the n+ drain region. Thus, this leads to a higher breakdown voltage compared with the case in which the electrons collide directly in the highly doped drain region.

Figure 9.8 Cross-section of an LDMOSFET.2 PHV is a high-voltage p-region; NHV is a high-voltage n-region with a low n-type doping concentration (drawn per the literature identified in the footnote).

2. Motorola, Semiconductor Technologies for RF Power F701, 2002.9.24.

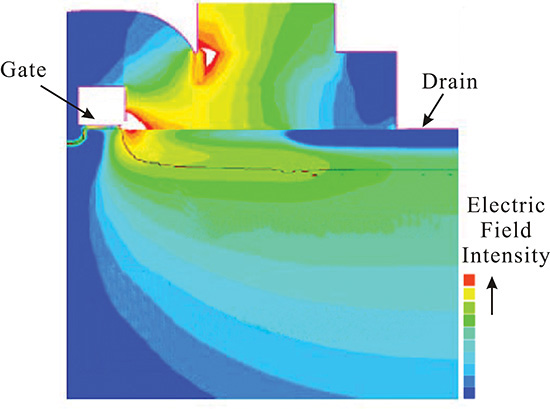

The next thing to note is that the source terminal is attached to the bottom of the device, which means that wire bonding is not required to connect the source terminal to the ground. A simple die attachment on the metal carrier is sufficient for the connection of the source terminal to the ground. Thus, the inductance that would otherwise arise from the wire bonding during packaging assembly is eliminated, which is an advantage during assembly. Figure 9.9 shows the electric-field simulation around the drain terminal that has a strong electric field across the NHV region, while the n+ drain region can be seen to have a weak electric field. As a result, the generation of electrons by collision occurs primarily in the lightly doped NHV region, where the number of those electrons is relatively smaller. This leads to a higher breakdown voltage than in the case of direct collision.

Figure 9.9 Electric-field simulation at the drain terminal of the LDMOSFET shown in Figure 9.8 (drawn per the literature.3) Note that the simulated electric-field intensity at the drain terminal becomes weak.

3. Ibid.

The manufacturing technology for LDMOSFETs is well-established. An LDMOSFET device that can supply up to several hundred W of RF power has been reported in the literature. However, the physical properties of Si limit its operation below the 4-GHz frequency region as the gain becomes low.

9.3 Optimum Load Impedances

In designing the power amplifier, the first problem is determining optimum load impedance. The reason for naming the optimum impedance, rather than the maximum output power impedance, is that the design goal can be set for maximum efficiency or other parameters, depending on the design conditions, and the optimum load impedance does not necessarily give the maximum output power.

In designing a low-noise amplifier, the optimum source and load impedances can be calculated directly from the measured small-signal S-parameters at a given DC bias. However, because the power amplifier basically operates in the large-signal region, the optimum load impedance cannot be determined using the small-signal S-parameters. Therefore, the optimum load impedance is determined either from direct experimental measurement or computed from the large-signal model prior to creating the power amplifier design. In this section, we will describe the method of obtaining the optimum load impedance by the experimental method as well as by a computational method that uses software.

9.3.1 Experimental Load-Pull Method

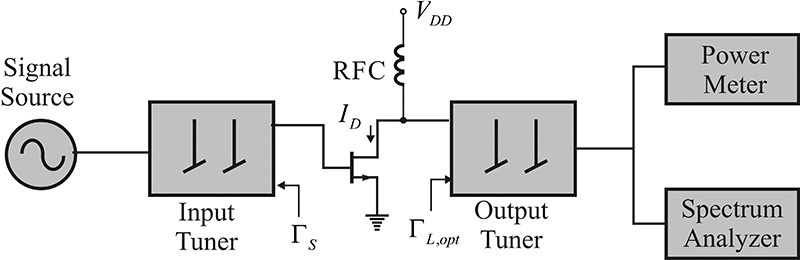

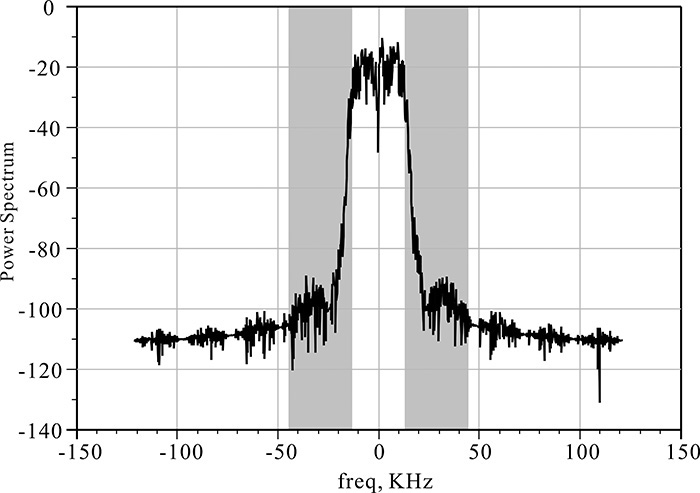

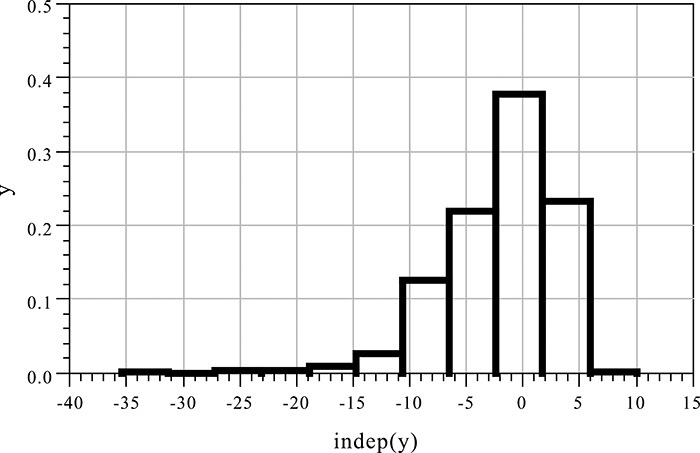

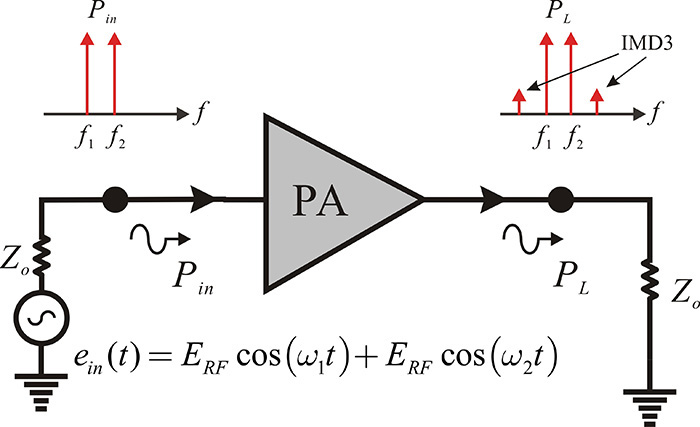

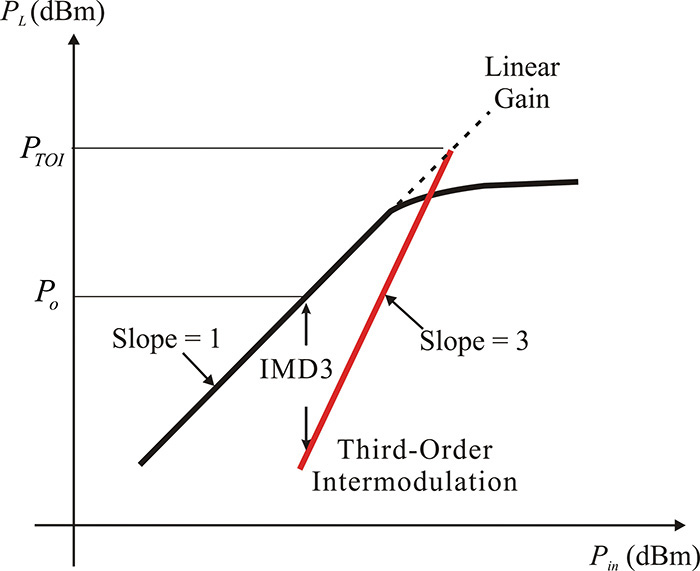

Load-pull measurement refers to measuring an active device’s efficiency or output power by varying the load impedance. An impedance tuner is generally used to vary the load impedance. As mentioned earlier, the optimum load impedance of a power amplifier cannot be obtained from the measured small-signal parameters. Thus, the load impedance connected to the active device’s output is tuned using an impedance tuner, and the optimum load impedance is obtained. This is referred to as a load-pull measurement. Figure 9.10 shows two impedance tuners that are inserted before and after the active device, and the source and load impedances are tuned under a given input power to obtain the optimum output power. In this method, the input tuner is first adjusted to deliver maximum power from the signal source to the input of the active device, after which the output tuner is adjusted to deliver maximum output power to the load. Once the adjustments are completed, the impedance tuners are disassembled and the desired load and source reflection coefficients ΓS and ΓL,opt are obtained by measuring the impedances of the impedance tuners. The spectrum analyzer and power meter connected to the output impedance tuner in Figure 9.10 make it possible to measure the exact value of the output power while simultaneously observing the output spectrum in the spectrum analyzer. The power meter can accurately measure the output power but it cannot detect the presence of spurious signals, which necessitates the use of the auxiliary spectrum analyzer. Nonharmonic spurious signals often occur at the output of the power amplifier but the power meter cannot distinguish whether or not the nonharmonic spurious signals occur, which is why the spectrum analyzer is required. Thus, the spectrum analyzer is included for observing the spurious signals.

Figure 9.10 Load-pull setup. The output power is accurately measured by the power meter and the spectrum analyzer checks for the occurrence of spurious signals in the output signal.

In the case of low harmonics, the optimum load impedances can easily be obtained from the previous load-pull measurement. However, a problem does occur when the harmonic impedances must be considered. In general, the maximum output power is determined from the load impedance of the fundamental frequency, but the efficiency varies according to the harmonic load impedances. Recently, an impedance tuner that can independently tune the harmonic load impedances in order to resolve the harmonic tuning problem has been reported in the literature. A photograph of a harmonic impedance tuner is shown in Figure 9.11. Most recent impedance tuners can also be controlled by a PC, and their impedances can be read without disassembling them from the load-pull setup for the impedance measurement. The PC-controlled impedance tuners also provide utilities that draw a contour plot of the impedance, yielding the same output power or efficiency from measured data. Measuring the optimum source and load impedances using the load-pull method assists in the convenient and reliable design of power amplifiers.

Figure 9.11 Photograph of an impedance tuner with three carriages. The three harmonic impedances can be separately controlled using this impedance tuner. Source: Focus Microwaves Inc., Three Carriage Three Harmonic Tuner, January 2012.

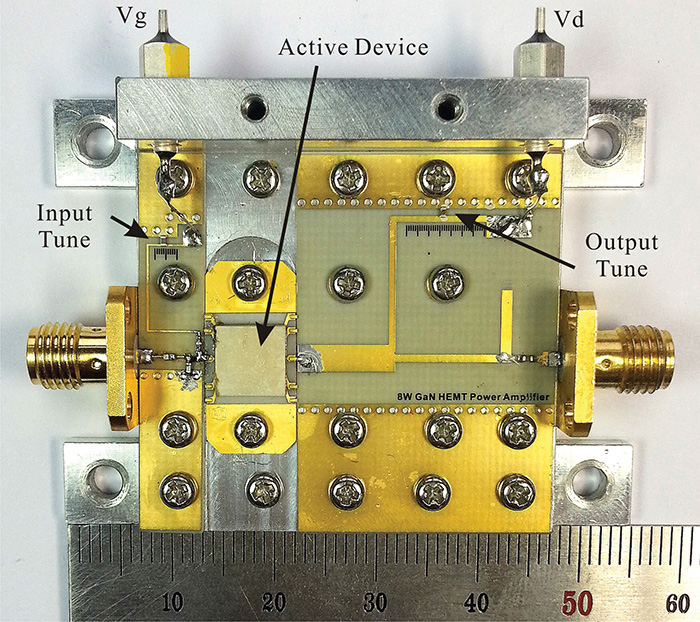

There is another method for designing and fabricating power amplifiers experimentally without relying on load-pull measurements. An example of this method is shown in Figure 9.12. Using this method, a power amplifier’s design allows for adjustable input and output matching circuits that use the optimum impedances in the datasheet, and the power amplifier is designed by adjusting the input and output matching circuits with a given RF input power and DC bias. Once the required specifications such as output power, efficiency, harmonic characteristics, and intermodulation are met, then the adjusted power amplifier can be used as a power amplifier if there are no other problems in size and mass production. However, the size of the power amplifier may be too large for some applications and further miniaturization may be required for those applications. Unlike the power amplifier shown in Figure 9.12, a power amplifier without tuning points may also be necessary for mass production. In those cases, the power amplifier shown in Figure 9.12 is disassembled and the source and load impedances are measured with a network analyzer as in a load-pull measurement. A miniaturized power amplifier can then be redesigned using the measured impedances.

Figure 9.12 Experimental design of an adjustable power amplifier. The location and value of the chip component can be varied for the input and output matchings.

In Figure 9.12, the chip capacitor in the input matching circuit is for input tuning and its position and value can be moved by soldering. Thus, the input matching circuit can be adjusted by trial and error until the optimum input impedance is obtained. The output matching circuit can be similarly adjusted. Thus, the output matching can be achieved through these adjustments.

The advantage of the adjustable circuit impedances is that the power amplifier can be designed without the cumbersome task of modeling the active devices, so the characteristics of the fabricated power amplifier can be determined experimentally, which otherwise would be difficult to predict accurately with the large-signal equivalent circuit. The disadvantage is that because the adjustable range of the input and output matching circuit impedances is limited compared to that in the prescribed load-pull measurement, the input and output matching circuits must be designed to provide the desired input and output matching impedances. Otherwise, the designated goal cannot be achieved. In addition, when changes occur in the DC operating point or input power for a new power amplifier, the obtained input and output matching impedances are not generally optimal for those changed conditions. Therefore, to obtain the optimum input and output impedances when those conditions change, the adjustable power amplifier in Figure 9.12 should be retested using the method discussed above that includes adjusting component values and positions. In the case of mass production, tolerance analysis may also be necessary; however, this method can present difficulties in terms of predicting the effects of parameter changes in an active device or in power amplifier’s matching circuits.

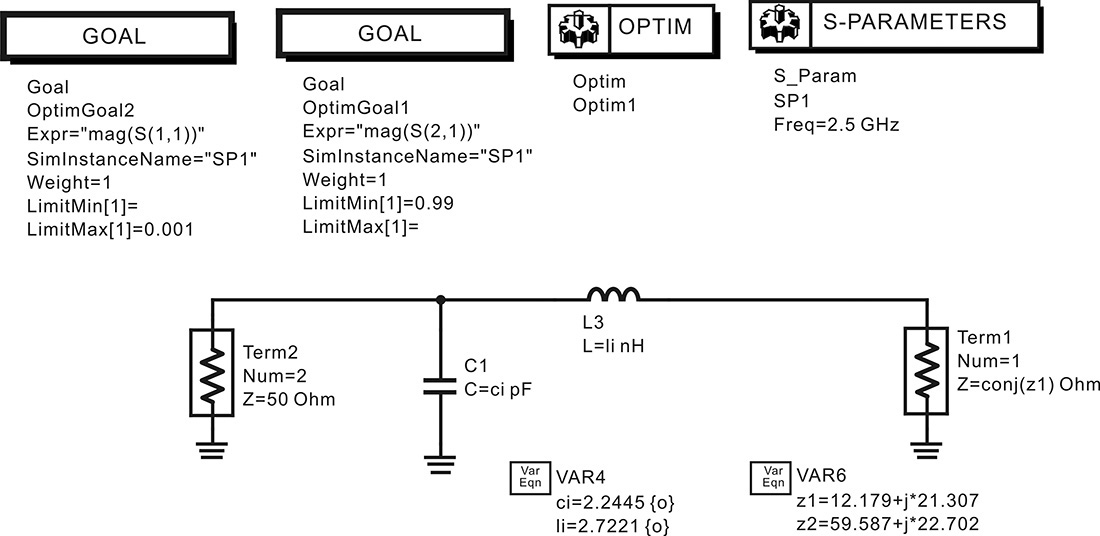

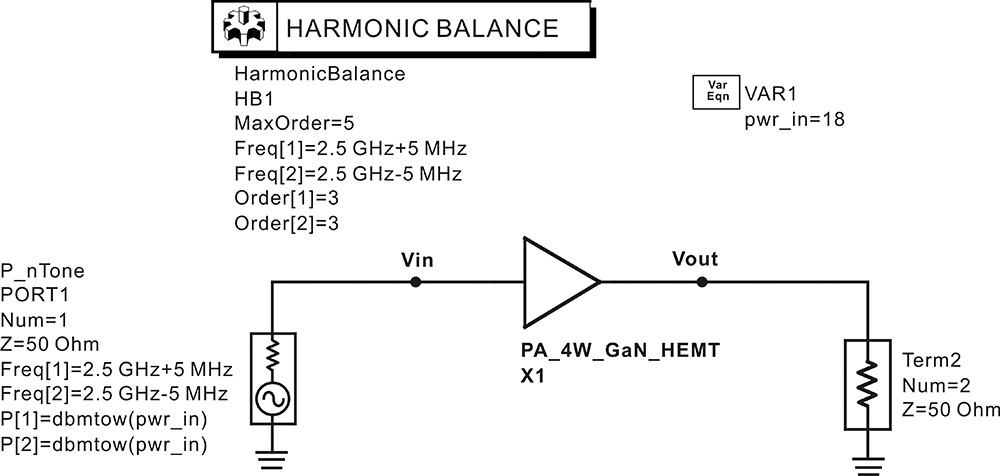

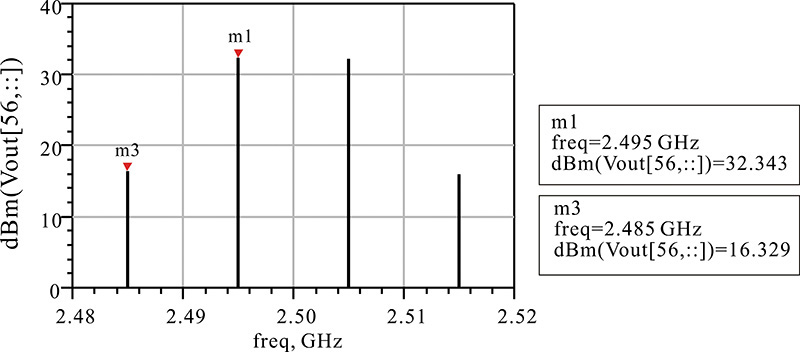

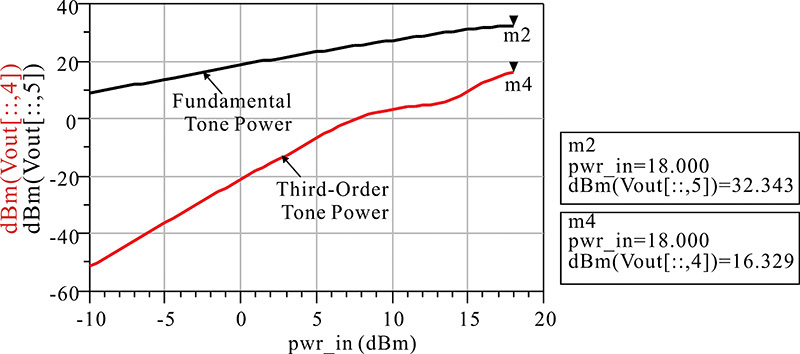

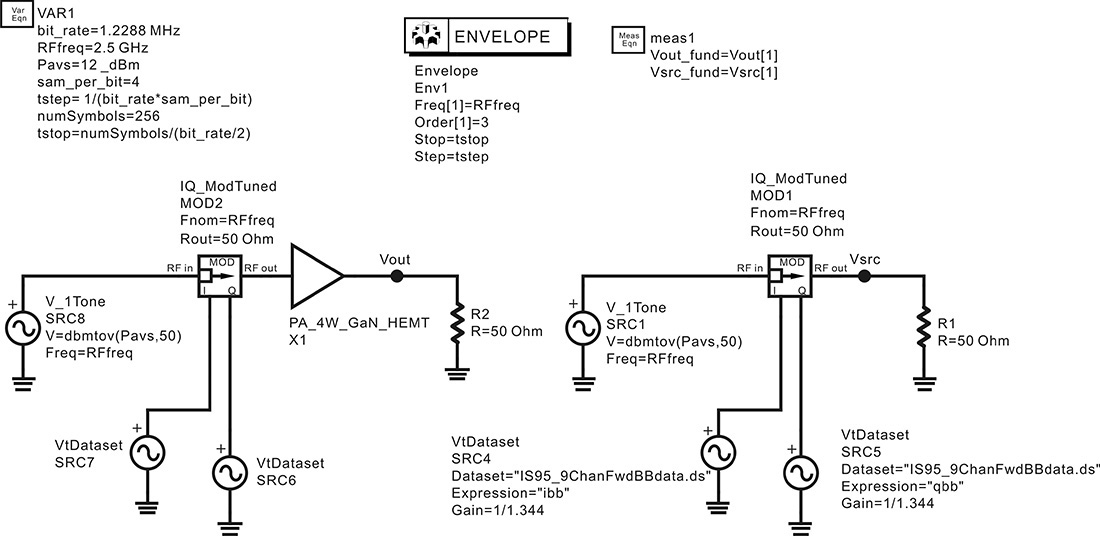

9.3.2 Load-Pull Simulation

An alternative method for obtaining the optimum source and load impedances is the load-pull simulation based on the large-signal model of an active device.

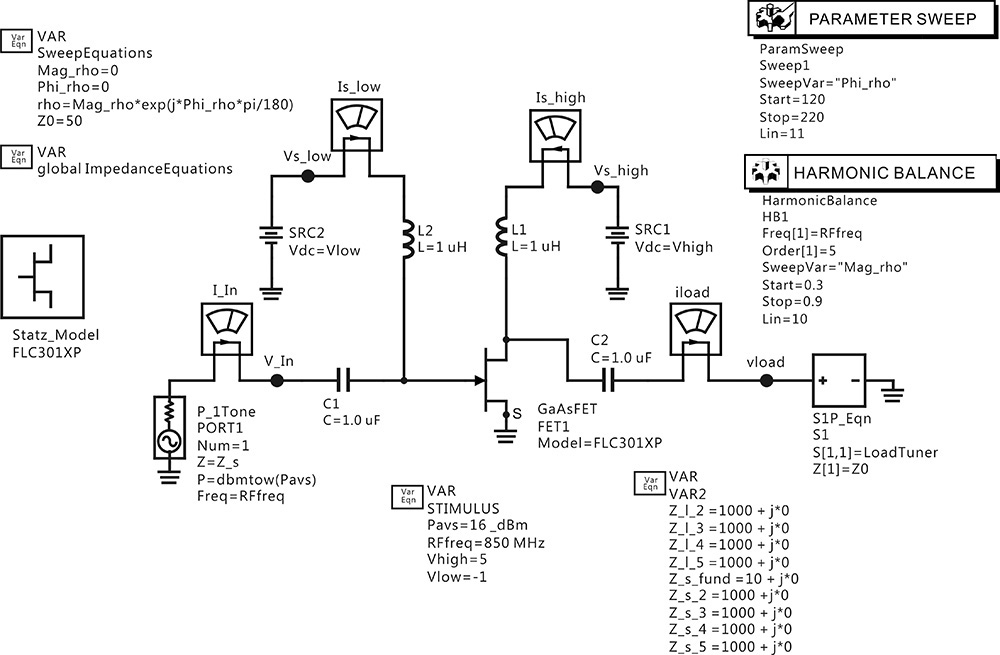

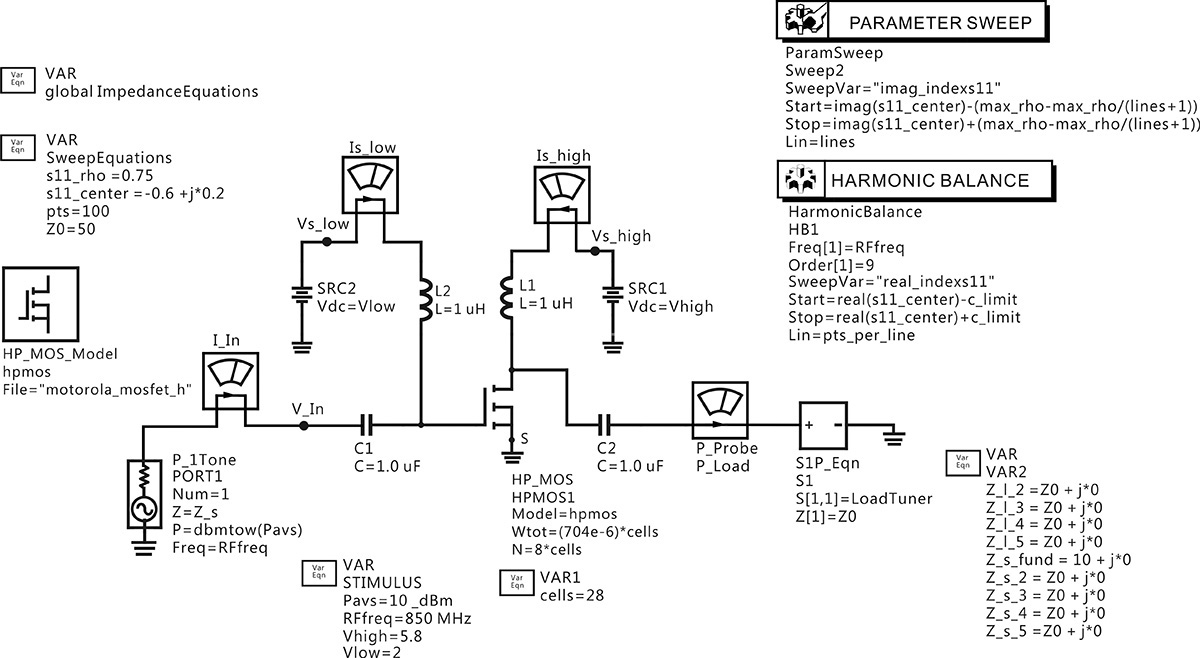

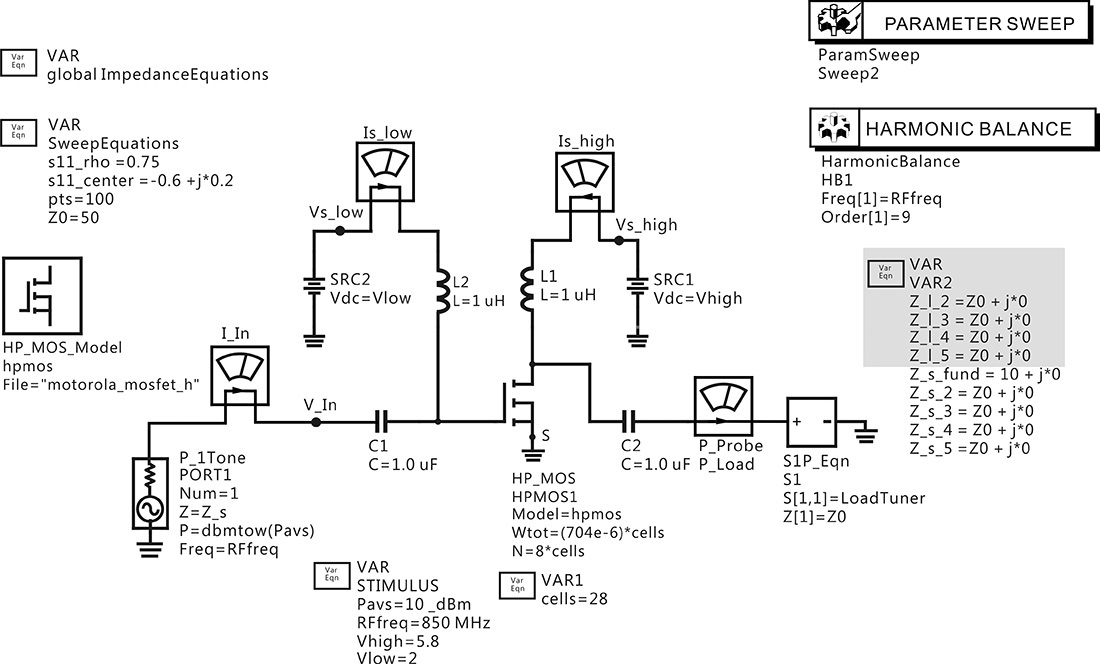

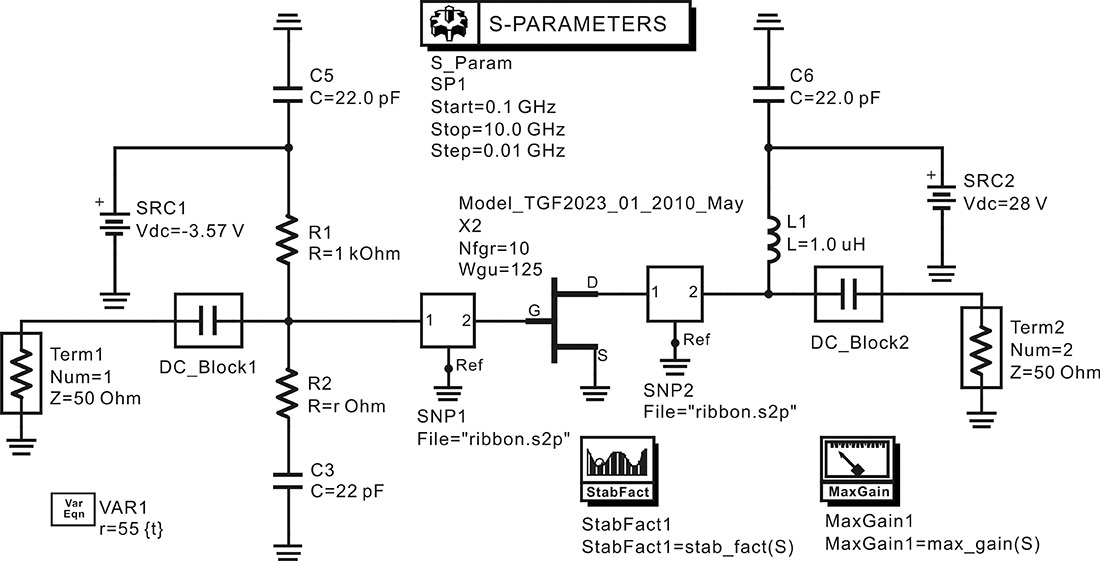

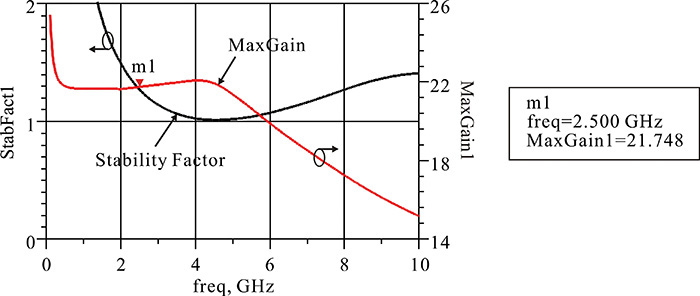

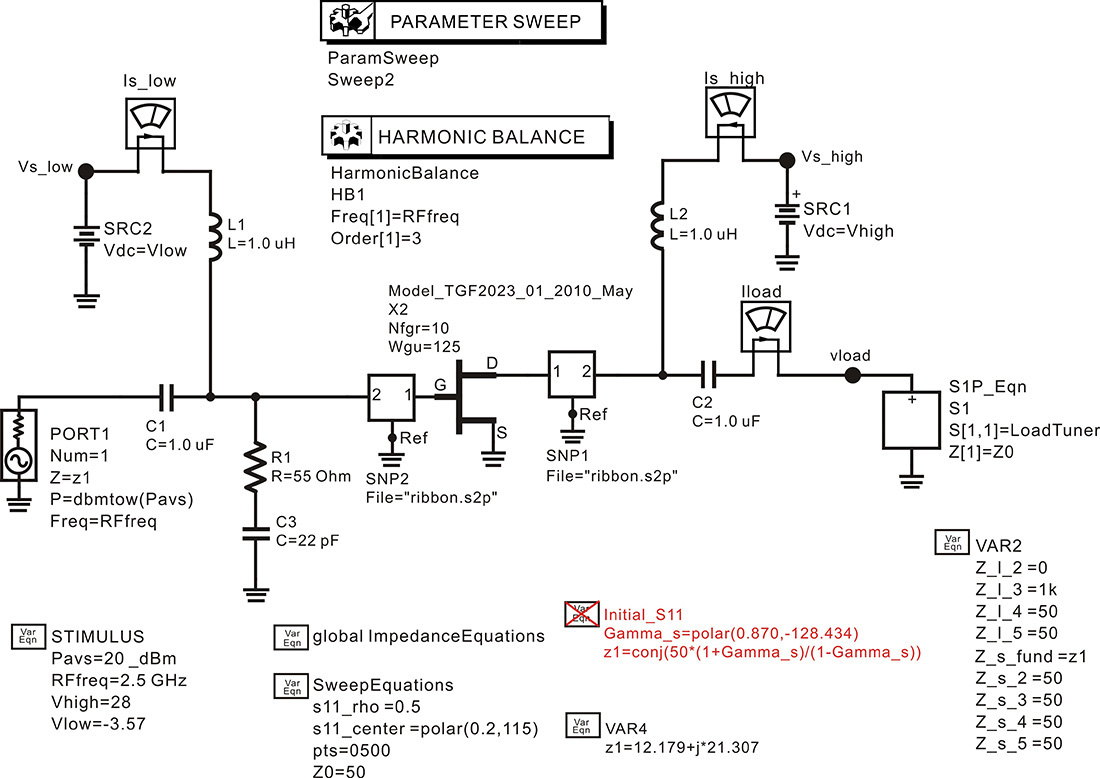

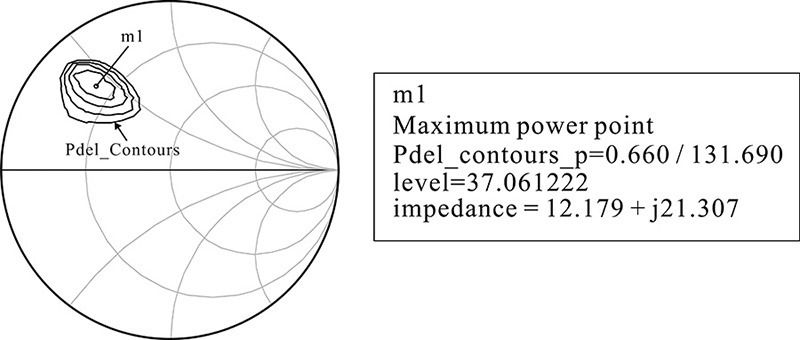

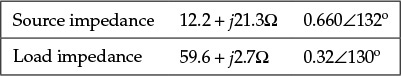

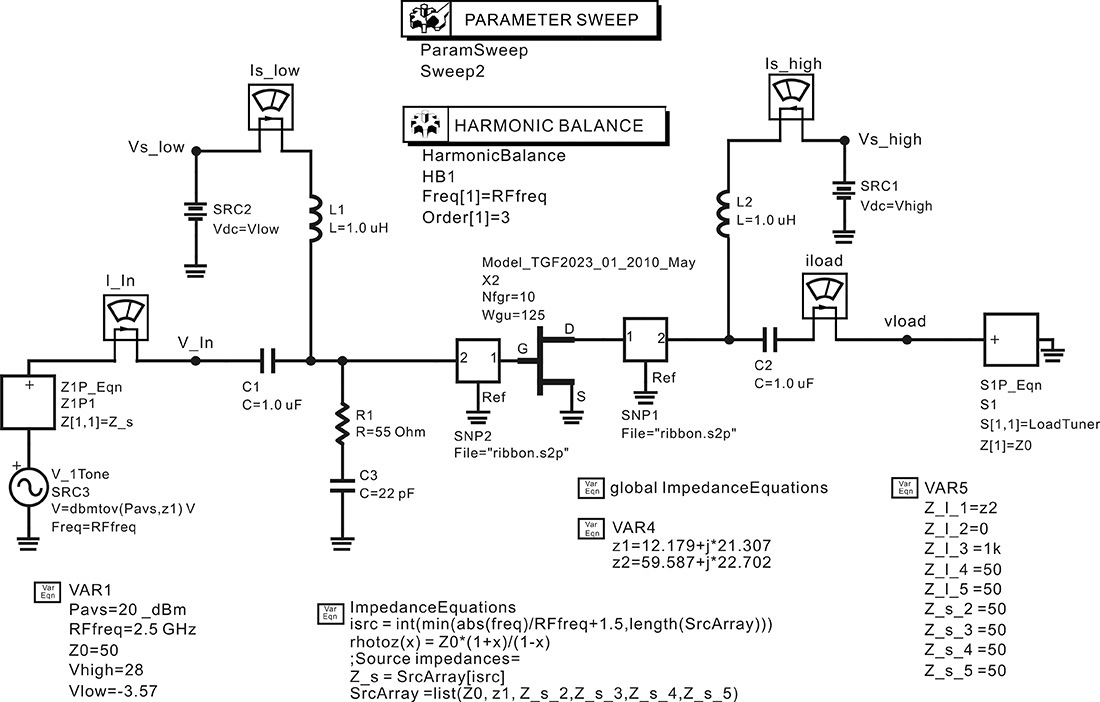

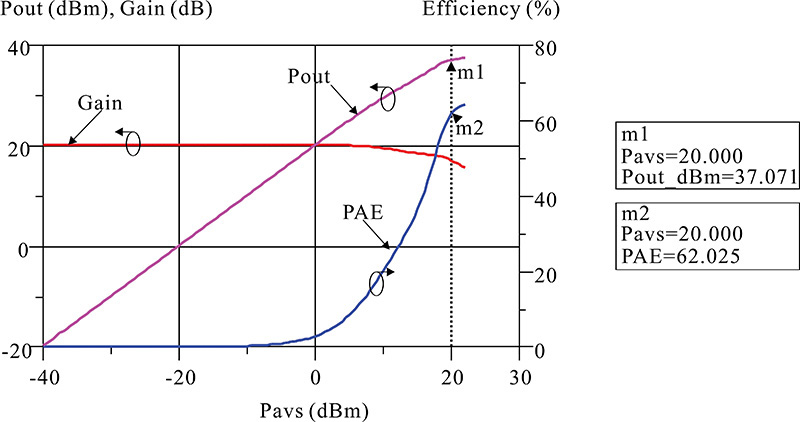

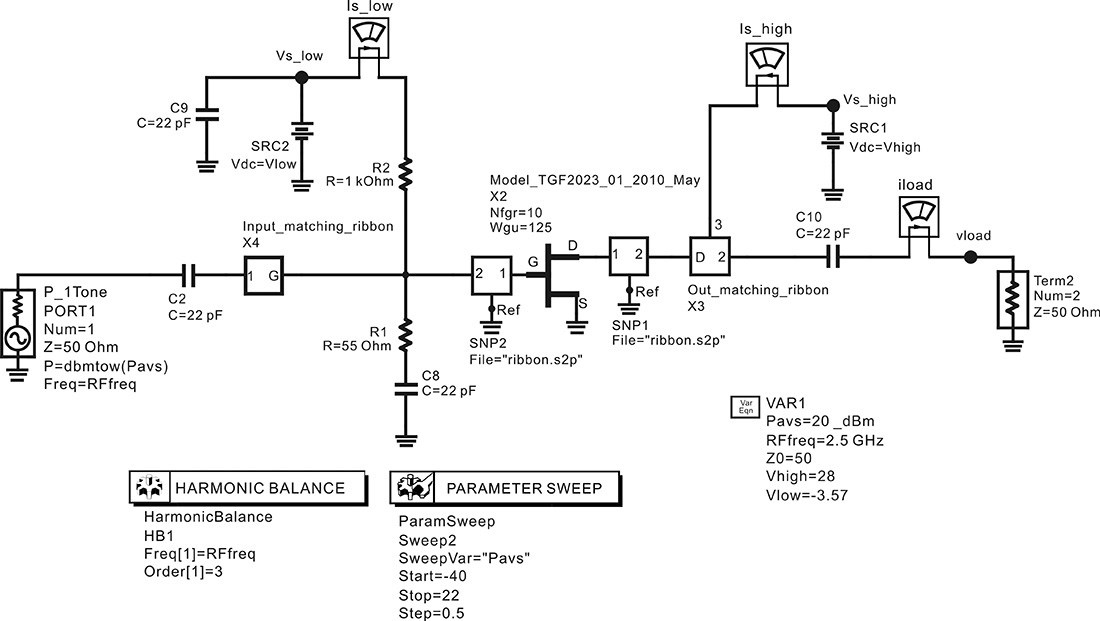

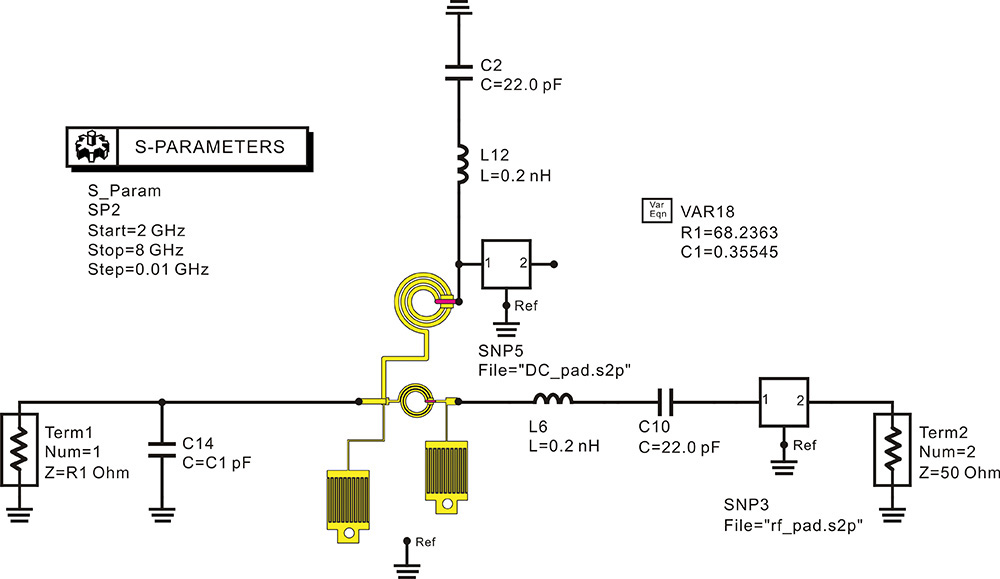

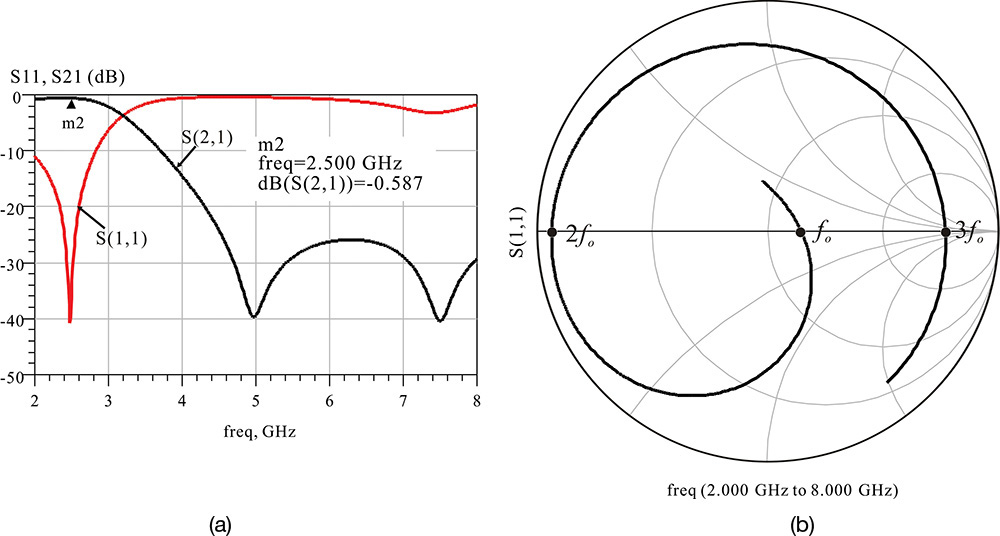

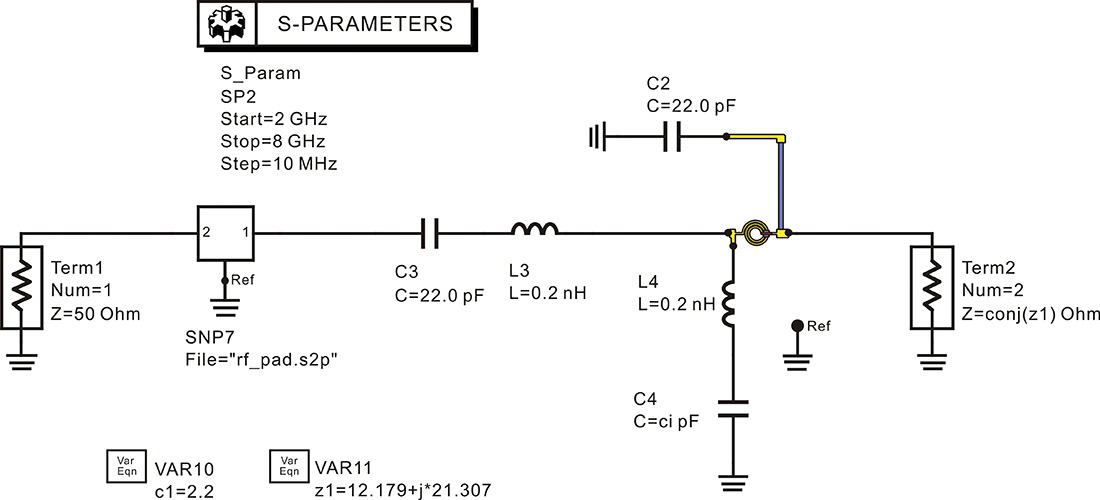

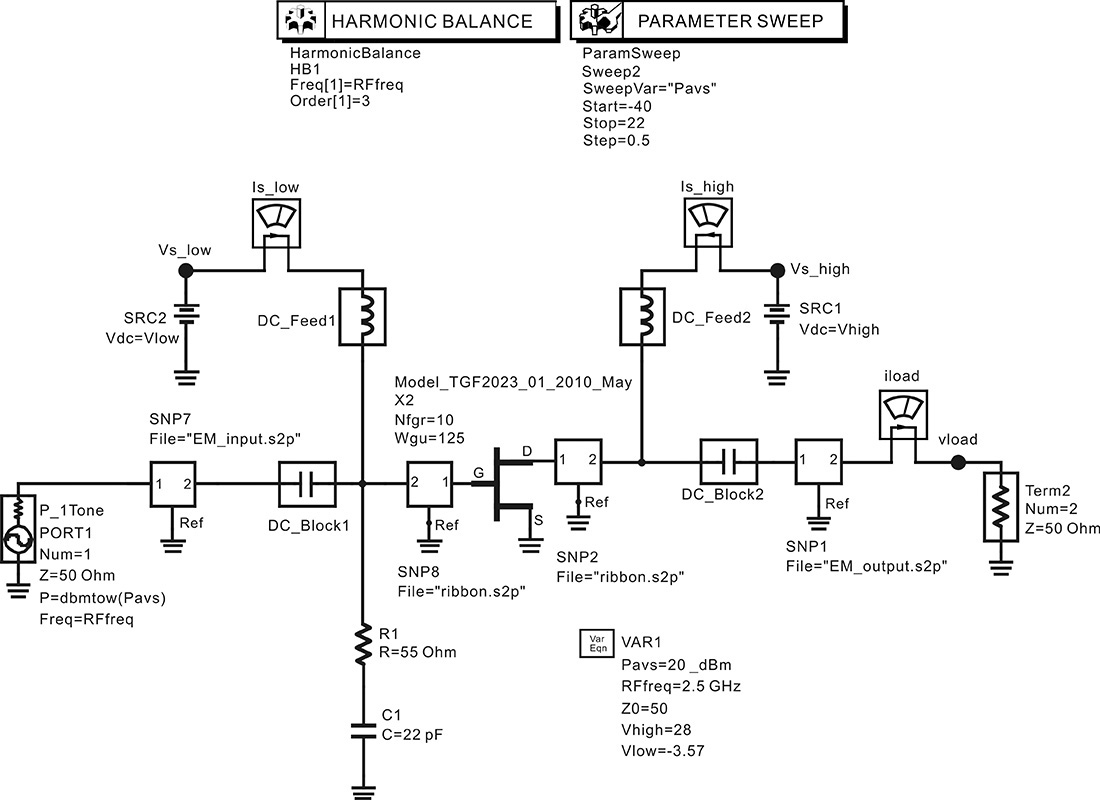

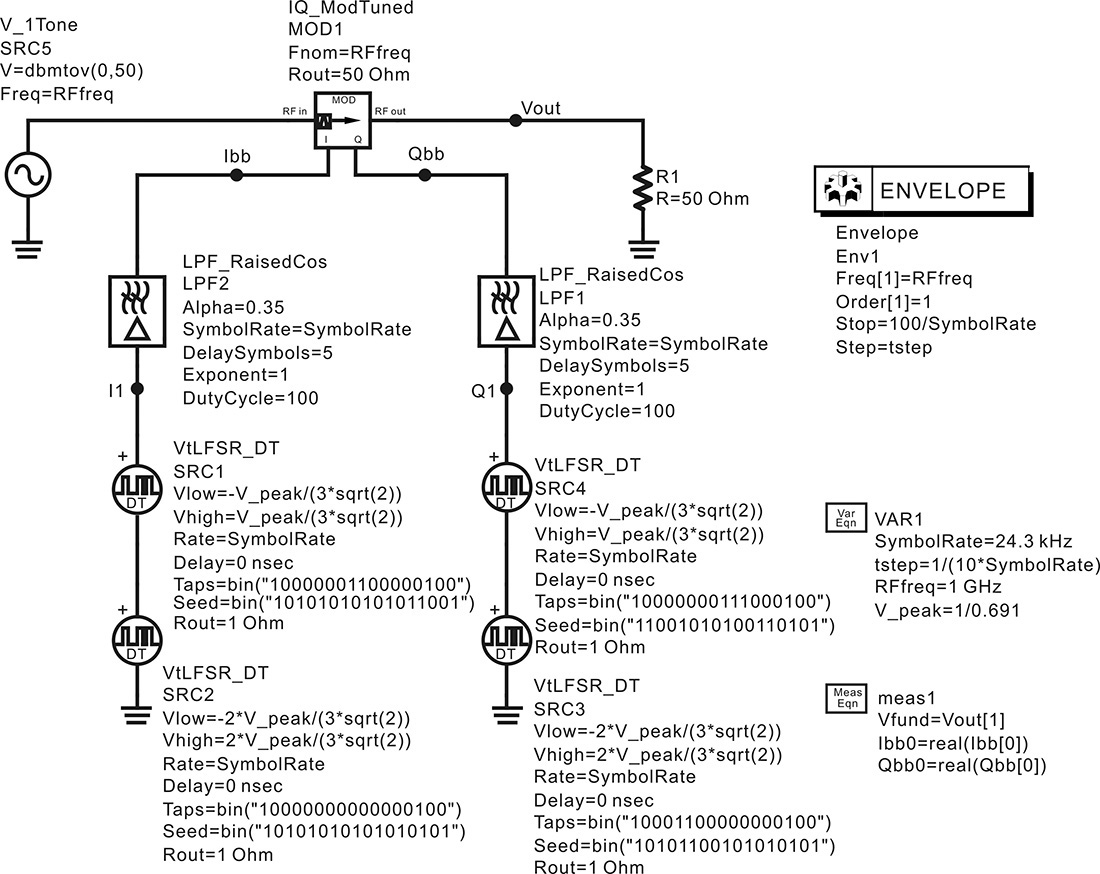

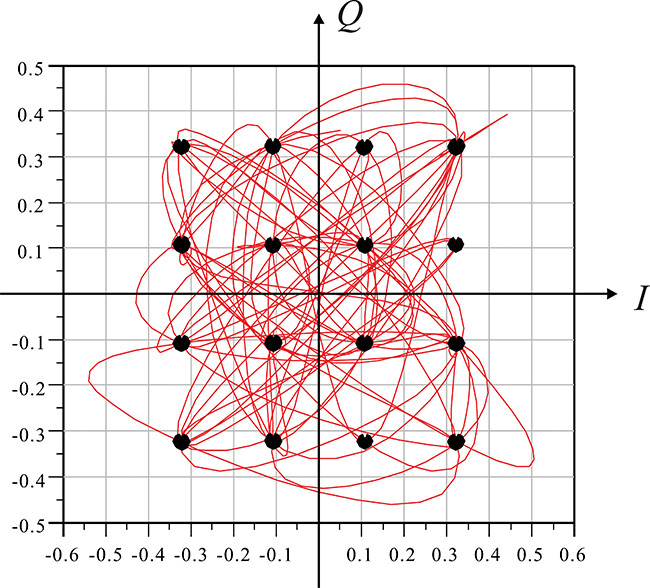

When the large-signal model of an active device is available, this method involves setting up a load-pull simulation circuit in ADS, as shown in Figure 9.13, and calculating the desired optimum source and output load impedances; see reference 1 at the end of this chapter. This approach is frequently used in the design of an MMIC (monolithic microwave integrated circuit) power amplifier.

Figure 9.13 Load-pull simulation in ADS. The load impedance is adjusted using the S1P Equation component. The value LoadTuner of the S1P Equation component is determined using the variable block named globalImpedanceEquation, which is hidden. The LoadTuner value is two-dimensionally swept by the Parmeter Sweep and Harmonic Balance simulation components.

However, in the case of a packaged active device, the equivalent circuit should take into account the parasitic elements that occur in packaging and may cause the equivalent circuit to become extremely complex and may degrade its accuracy. The advantage that the load-pull simulation method has over the experimental load-pull method is that the optimum source and load impedances can be obtained simply through simulation that reflects the changes that may occur in the power amplifier’s circuit conditions, such as frequency and the DC bias operating point. In contrast, with the experimental load-pull method, each time the power amplifier’s condition changes—for example, if the frequency is changed—a new measurement must be taken to obtain the optimum source and load impedances. The disadvantage is that because it is not easy to obtain the accurate large-signal model, the large-signal model itself includes a certain degree of inaccuracy, which makes the accuracy of the results problematic.

9.3.2.1 Load Impedance

In Figure 9.13, the input frequency RFfreq is 850 MHz and input power Pavs is 10 dBm. Inductors L1 and L2 function as an RFC because their values are set to 1 μH. The values have been set sufficiently large for the chosen frequency. The DC-block capacitors C1 and C2 have values of 1 μF, which is also sufficiently large. Port 1 is the input port that has an impedance of Z_s and a power level of Pavs. The function dbmtow(·) converts the power level expressed in dBm to W. An impedance tuner implemented as a one-port circuit is connected to the output of the active device. In Figure 9.13, Z_l_2, Z_l_3, Z_l_4, and Z_l_5 of VAR2 are the load impedances at the harmonic frequencies of 2fo, 3fo, 4fo, and 5fo, respectively. By altering the harmonic load impedances, the efficiency or output power of the power amplifier can be tuned. Similarly, Z_s_2, Z_s_3, Z_s_4, and Z_s_5 are the source impedances at the harmonic frequencies of 2fo, 3fo, 4fo, and 5fo, respectively. The harmonic source impedances are also adjustable. The value of the source impedance at the fundamental frequency Z_s_fund is set to 10 Ω. The frequency-dependent source and load reflection coefficients are defined using the variable block globalImpedanceEquations shown in Measurement Expression 9.1, which is not shown in the schematic window because of its complexity.

![]() VAR

VAR

global Impedance Equations

;Tuner reflection coefficient

LoadTuner=LoadArray[iload]

LoadArray=list(0,rho,fg(Z_l_2),fg(Z_l_3),fg(Z_l_4),fg(Z_l_5))

iload=int(min(abs(freq)/RFfreq+1.5,length(LoadArray)))

fg(x)=(x-Z0)/(x+Z0)

;Source impedances

Z_s=SrcArray[isrc]

SrcArray=list(Z0,Z_s_fund, Z_s_2, Z_s_3,Z_s_4, Z_s_5)

isrc=min(iload,length(SrcArray))

Measurement Expression 9.1 Source and load impedance setup

Measurement Expression 9.1 is the opened view of the globalImpedanceEquations. The value of LoadTuner here represents the resulting load impedance. The function fg(∙) is defined to convert the given harmonic load impedances into the corresponding reflection coefficients. The row vector, LoadArray, is formed using the converted reflection coefficients at each harmonic frequency. The function list(∙) is used to form a vector. Here, the first value of the LoadArray is the reflection coefficient at DC and the second value is the reflection coefficient at the fundamental frequency. All the values are set this way up to the fifth harmonic. It should be noted that the load impedance is open at DC because the reflection coefficient at DC is set to 0. The reflection coefficient of the fundamental frequency in LoadArray is set to rho, which is defined by the variable block named SweepEquations in Figure 9.13.

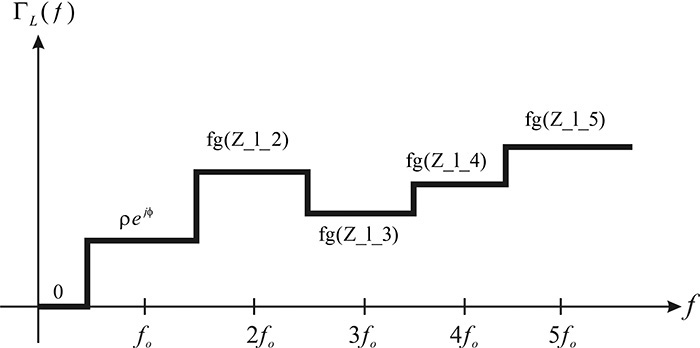

Figure 9.14 shows the desired frequency-dependent load reflection coefficient. Thus, the load reflection coefficient is ΓL = ρejφ for frequency 0.5fo < f < 1.5fo. The ranges of other harmonic frequencies are defined similarly to the fundamental frequency. The variable LoadTuner in Measurement Expression 9.1 represents the frequency-dependent load reflection coefficient shown in Figure 9.14 and it is synthesized using the row vector LoadArray.

In Measurement Expression 9.1, the frequency-dependent load reflection coefficient LoadTuner is implemented using the index of the row vector LoadArray. The variable iload represents the index. Define k as expressed in Equation (9.3).

When 0.5 × RFfreq < freq < 1.5 × RFfreq, the range of k is 2 < k < 3 from Equation (9.3). Also, it can be found that length(LoadArray) = 6. A smaller value between the two values for length(LoadArray) and k is selected using the min(∙) function. For 2 < k < 3, the smaller value becomes k. Thus, taking the integer part of k and using the int(∙) function gives a value of 2. Therefore, the value of iload becomes 2. The value of LoadTuner = LoadArray[iload] is the value corresponding to the index 2, which is ΓL = ρejφ. When 4.5 × RFfreq < freq, it becomes k > 6 from Equation (9.3). The smaller value thus becomes length(LoadArray) = 6. The corresponding reflection coefficient to index 6 is found to be fg(Z_l_5). With similar reasoning, it can be found that the frequency-dependent reflection coefficient LoadTuner shown in Figure 9.14 is synthesized.

It can be seen that the source reflection coefficient is determined in a similar way in Measurement Expression 9.1. The variable Z_s represents the frequency-dependent source reflection coefficient. The variable SrcArray is the row vector of the source reflection coefficients at each harmonic. The index that determines the value of the source reflection coefficient is isrc. It should be noted that the value of SrcArray at DC is set to the reference impedance Z0.

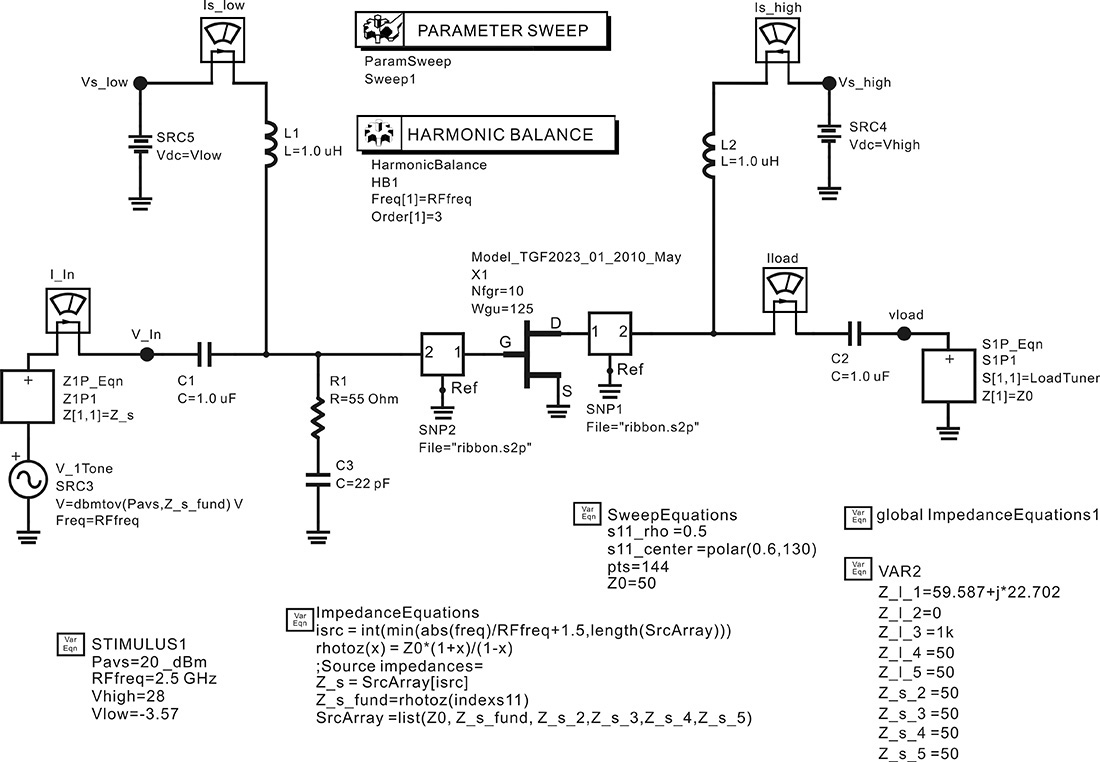

9.3.2.2 Sweep

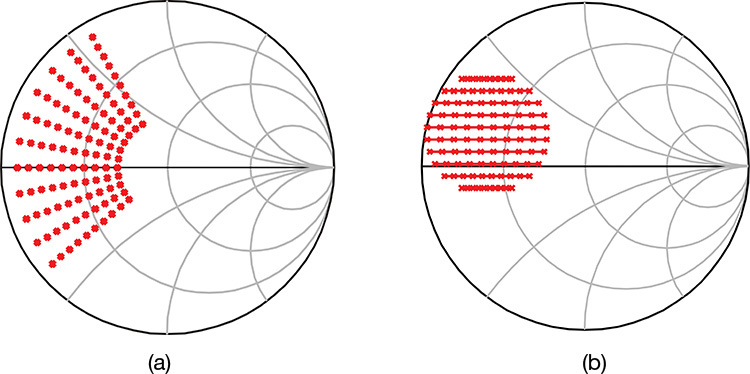

In Figure 9.13, the sweep of the load reflection coefficient is performed using harmonic balance simulation and parameter sweep. The variable rho that represents the load reflection coefficient at the fundamental frequency consists of Mag_rho and Phi_rho. The magnitude Mag_rho varies from 0.1 to 0.9, while the phase Phi_rho varies from 120° to 220°. This variation in the reflection coefficient is shown in Figure 9.15(a). However, the density of samples decreases as the radius approaches 1, thereby reducing the accuracy in the output power and efficiency contour plots. Instead, even though Figure 9.15(b) is somewhat complex in setting the sweep parameters, a region of the circle in the Smith chart can be uniformly sampled, which is advantageous when drawing more accurate contour plots for output power and efficiency. The simulation schematic for the samples shown in Figure 9.15(b) is shown in Figure 9.16.

Figure 9.15 Reflection coefficient sweeping methods: (a) samples obtained using the magnitude and angle method (polar sweep) and (b) uniform sampling of a region of the circle (uniform sample sweep)

Figure 9.16 Load-pull simulation for the newly specified sample method shown in Figure 9.15(b).

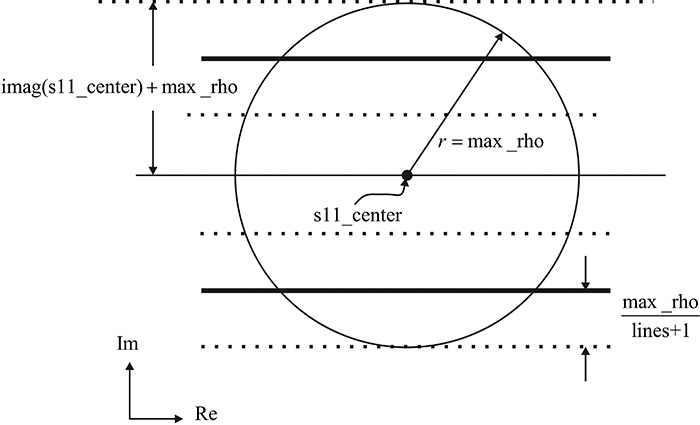

The simulation for the samples in Figure 9.15(b) can be carried out by sweeping the value of Γx for a given Γy when the load reflection coefficient is defined as ΓL = Γx + jΓy. In Figure 9.16, the sweep variables real_indexs11 and imag_indexs11 are defined to represent Γx and Γy. In the simulation schematic of Figure 9.16, harmonic balance simulation sweeps the value of Γx for a given Γy in the parameter sweep. The user must specify a number of samples and a region of the circle to be sampled. This is done by entering the number of samples and the center and radius of the circle. The variable block named SweepEquations in Figure 9.16 includes the necessary variables. The variables s11_center, s11_rho, and pts represent the center, the radius, and the number of samples. Using the user-specified variables, the number of lines in the direction of the y-axis, lines, and the number of samples per line, pts_per_line, are calculated and set in the variable SweepEquations VAR, which is hidden. Measurement Expression 9.2 is an opened view of SweepEquations.

real_indexs11=0

imag_indexs11=0

Z0=50

index_s11=real_indexs11+j*imag_indexs11

s11_rho=0.75

s11_center=-0.6+j*0.2

max_rho=min(1.0-mag(s11_center),mag(s11_rho))

pts=100

lines=max(int(sqrt(pts)),1)

pts_per_line=int(pts/lines)

argument=max_rho^2-(imag(s11_center)-imag_indexs11)^2

c_limit=sqrt(if(argument<0) then 0 else argument endif)

Measurement Expression 9.2 Opened view of the variable block named SweepEquations

The first two lines in the expression are for declaring the sweep variables real_indexs11 and imag_indexs11. Note that although they are set to 0, their values are newly defined through the parameter sweep. Variable index_s11 in the next line is the definition of ΓL at the fundamental frequency using the variables real_indexs11 and imag_indexs11. The value of index_s11 is used as ΓL instead of rho in the globalImpedanceEquations shown in Measurement Expression 9.1. Variables s11_rho and s11_center were described earlier and max_rho sets the new radius using the user-specified radius. This is necessary when the center and radius settings entered by the user are out of the unit Smith chart. Thus, the newly defined max_rho replaces the user-specified s11_rho.

Next, the number of lines in the direction of the y-axis, lines, is set using the total number of sample points, pts. Since the total number of sample points is proportional to the area, the variable lines is determined from sqrt(pts). The number of points per line, pts_per_line, then becomes the total number sample points divided by the number of lines, lines. Since lines and pts_per_line must be integers, the function int(⋅) converts them all into integers. Due to such definitions, the sample points at both ends of the sample lines will be tightly spaced, while they will be widely sampled around the center line.

After the settings are made, in the case of the x-axis, the sweep range from the left to the right should be specified. However, the sweep range varies according to the y-axis values. That is, given y, from the equation of a circle with radius r, the possible values of x in the circle are represented by –(r2 – y2)½ ≤ x ≤ (r2 – y2)½. The value (r2 – y2)½ is represented by argument. To prevent the argument from being 0, the variable c_limit is newly defined. Therefore, the variable real_indexs11 corresponding to the x-axis reflection coefficient is swept from real(s11_center)–c_limit to real(s11_center)+c_limit, as shown in Figure 9.16. The y-axis reflection coefficient could have been swept in the range imag(s11_center)-max_rho<y<imag(s11_center)+max_rho for the number of lines. However, when lines = 2, y sweeps the two points at the end of the radius, an undesirable situation. Thus, at the end of the radius, the range is set to sweep above and below the line by a sweep range of max_rho/(lines + 1), as shown in Figure 9.17.

9.3.2.3 Display

The simulated results for the previously defined settings are the voltages and currents for the load reflection coefficient change. In order to calculate the output power and efficiency, the equations shown in Measurement Expression 9.3 are entered in the display window to calculate the DC power consumption. The index[0] in this expression represents the DC component and the exist(·) function determines whether or not the variable calculated from the simulation exists or not. The function exist(·) gives a value of 0 when the value specified by the expression does not exist. Therefore, during simulation, when the DC source and DC current probe are not defined by the names shown in Measurement Expression 9.3, the calculation results in the wrong values. The value 1e-20 is added to the DC power consumption Pdc. When the power consumption is 0, the division by zero occurs in the efficiency calculation. Then, 1e-20 is added in order to prevent division by zero without affecting the calculation results.

![]() Vs_l=exist(“real(Vs_low[0])”)

Vs_l=exist(“real(Vs_low[0])”)

![]() Vs_h=exist(“real(Vs_high[0])”)

Vs_h=exist(“real(Vs_high[0])”)

![]() Is_l=exist(“real(Is_low.i[0])”)

Is_l=exist(“real(Is_low.i[0])”)

![]() Is_h=exist(“real(Is_high.i[0])”)

Is_h=exist(“real(Is_high.i[0])”)

![]() Pdc=Is_h*Vs_h+Is_l*Vs_l+1e-20

Pdc=Is_h*Vs_h+Is_l*Vs_l+1e-20

Measurement Expression 9.3 Equations in the display window for calculating the DC power consumption

![]() Pdel_Watts=real(0.5*vload[1]*conj(Iload.i[1]))

Pdel_Watts=real(0.5*vload[1]*conj(Iload.i[1]))

![]() Pavs_Watts=10**((Pavs[0,0]-30)/10)

Pavs_Watts=10**((Pavs[0,0]-30)/10)

![]() PAE=100*(Pdel_Watts-Pavs_Watts)/Pdc

PAE=100*(Pdel_Watts-Pavs_Watts)/Pdc

![]() Pdel_dbm=10*log10(Pdel_Watts)+30

Pdel_dbm=10*log10(Pdel_Watts)+30

Measurement Expression 9.4 Equations for calculating the power delivered to the load

Measurement Expression 9.4 shows the equations for calculating the power delivered to the load and the efficiency of using DC power consumption obtained from the load-pull simulation. The first line of this expression calculates the delivered power at the fundamental frequency. However, when a power probe P_Load is used, as shown in Figure 9.16, the first line changes as shown in Measurement Expression 9.5.

![]() Pdel_Watts=P_Load.p[1]

Pdel_Watts=P_Load.p[1]

Measurement Expression 9.5 Equation for the delivered power using the power probe

The second line in Measurement Expression 9.4 calculates the input power using a variable stored in the dataset in the simulation shown in Figure 9.16. The variable Pavs becomes a two-dimensional variable because the parameter-swept simulation was carried out for two independent variables. Thus, the constant value from the two-dimensional variable Pavs is obtained by specifying Pavs as Pavs[0,0]. In addition, because Pavs is specified in dBm, the unit is changed to W by the equation in the second line. The third line calculates the PAE and the last line calculates the delivered output power in dBm. Once PAE and Pdel_dbm are calculated, they can be used to plot the contours.

![]() PAE_step=2

PAE_step=2

![]() NumPAE_lines=5

NumPAE_lines=5

![]() PAEmax=max(max(PAE))

PAEmax=max(max(PAE))

![]() PAE_contours=contour(PAE,PAEmax-0.1-[0::(NumPAE_lines-1)]*PAE_step)

PAE_contours=contour(PAE,PAEmax-0.1-[0::(NumPAE_lines-1)]*PAE_step)

Measurement Expression 9.6 Equations for drawing the contour plot

It is common practice to plot the contours from the maximum point at equally spaced step changes in a descending order. To do this, we first need to obtain the maximum value. The method for doing this is identical to that for finding the maximum of the delivered power, so only the plot of PAE contours will be discussed. Since the max(∙) function used to obtain the maximum value gives the maximum for a single sweep variable, the maximum can be obtained by using the equation max(max(PAE)) shown in Measurement Expression 9.6. The NumPAE_lines in this expression represents the number of contour plots to be drawn. The interval is set by PAE_step. Since PAE in Measurement Expression 9.4 is calculated as a percentage, this corresponds to a step of 2%. The function contour(∙) in Measurement Expression 9.6 is a function that gives the coordinates (x, y) as the output. For the coordinates (x, y), x is the independent variable of the function contour(∙) and y is the value of the function contour(∙). In addition, x is the primary sweep variable, while y is a secondary sweep variable. In the case of the example in Figure 9.16, real_indexs11 is the independent variable of the PAE_contours defined in Measurement Expression 9.6. In the case of the load-pull simulation for the polar sweep in Figure 9.13, Mag_rho is the independent variable of PAE_contours. The y coordinate value is stored in PAE_contours. Thus, to explain Measurement Expression 9.6, for example, the (x, y) coordinates can be represented as (indep(PAE_contours), PAE_contours) and the corresponding value of the contour level is stored as a separate independent variable. The obtained PAE_contours should be converted to the complex numbers in the Smith chart using the equations shown in Measurement Expression 9.7. The first two equations in that expression are used to convert the uniformly sampled swept PAE_contours into the complex numbers in the Smith chart, while the last two equations are used to convert the polar swept PAE_contour into the complex numbers in the Smith chart.

![]() PAE_contours=contour(PAE, PAEmax-0.1-[0::(NumPAE_lines-1)]*PAE_step)

PAE_contours=contour(PAE, PAEmax-0.1-[0::(NumPAE_lines-1)]*PAE_step)

![]() PAE_contours_p=[indep(PAE_contours)+j*PAE_contours]

PAE_contours_p=[indep(PAE_contours)+j*PAE_contours]

![]() PAE_contours=contour(PAE, PAEmax-0.1-[0::(NumPAE_lines-1)]*PAE_step)

PAE_contours=contour(PAE, PAEmax-0.1-[0::(NumPAE_lines-1)]*PAE_step)

![]() PAE_conts_forSmithCh=indep(PAE_contours)*exp(j*PAE_contours*pi/180)

PAE_conts_forSmithCh=indep(PAE_contours)*exp(j*PAE_contours*pi/180)

Measurement Expression 9.7 Conversion of the contour plot values into complex numbers for plotting on the Smith chart

Open the HB1Tone_LoadPull.dsn of examples/RF_board/NADC_PA_prj in ADS and modify the original simulation schematic as shown in Figure 9E.1.

Figure 9E.1 HB1Tone_LoadPull.dsn in examples/RF_board/ NADC_PA_prj. The load impedance is swept by a uniform sample sweep. The values in the shaded area are changed from the values in Figure 9.16 for comparison.

Perform the simulation and plot the PAE and delivered power contours. Then, set the even harmonic impedance of the LoadTuner to 0 Ω and the odd harmonic impedance of the LoadTuner to 1 kΩ, and investigate the variation in the contour plot. The values of the LoadTuner can be specified using the numbers in the shaded area of Figure 9E.1.

Solution

A schematic that is different from that shown in Figure 9E.1 is displayed when the file mentioned in the specified directory is opened. After deleting the explanations in the original schematic, the schematic in Figure 9E.1 can be obtained. It can be seen that all the load impedances in Figure 9E.1 at all harmonics, except at the fundamental frequency, are set to 50 Ω. In addition, the sweep of the fundamental impedance is performed using the method shown in Figure 9.15(b). Also, the power probe P_Probe was used to calculate the power delivered to the load. Therefore, the power for the fundamental frequency becomes P_Load.p[1].

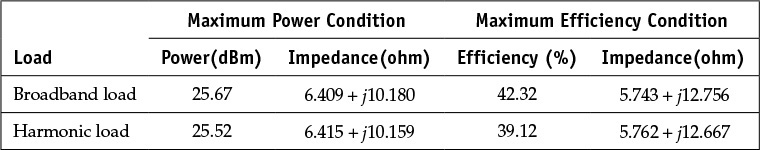

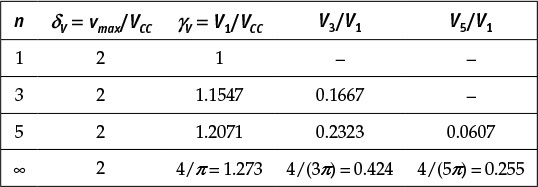

Figure 9E.2 is a comparison of the results obtained from the simulation with all harmonic load impedances set to 50 Ω (broadband load) with the simulation that has the even harmonic load impedances set to 0 and the odd harmonic impedances set to 1 kΩ (harmonic load). The comparison of contour plots for the delivered power is shown in Figure 9E.2(a) and the PAE contour plot comparison is shown in Figure 9E.2(b). It can be seen in Figure 9E.2(a) that the variations of the maximum point of the delivered power and the contours do not significantly depend on the harmonic impedance variation. On the other hand, unlike the contour plot of the delivered power, the PAE shows, to some degree, a change in response to changes in harmonic impedances. This will be explained in a later section of this chapter on class-F amplifiers. In addition, the results of the comparison are summarized as shown in Table 9E.1. The maximum powers in Table 9E.1 do not change significantly with respect to the change in the harmonic impedances but the maximum PAEs show significant changes. However, it can be seen that the fundamental impedance that gives maximum output power and maximum PAE does not change significantly.

Figure 9E.2 Comparison of (a) contour plots of the output powers and (b) PAEs with broadband load and harmonic load. Pdel_contours_p and Pdel_contours_p1 are the contour plots for delivered power for broadband and harmonic loads, respectively. PAE contours are similarly drawn.

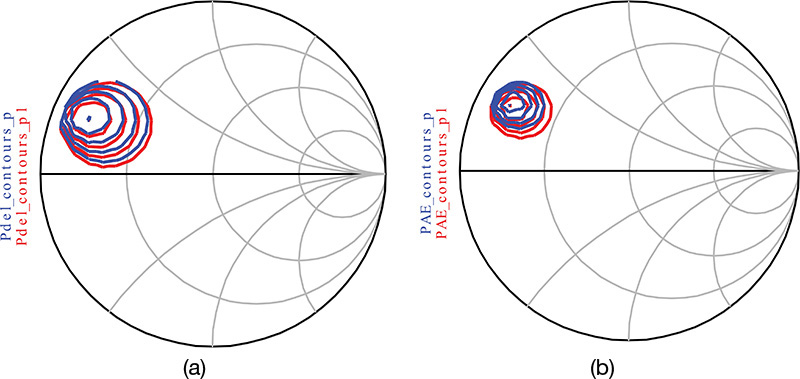

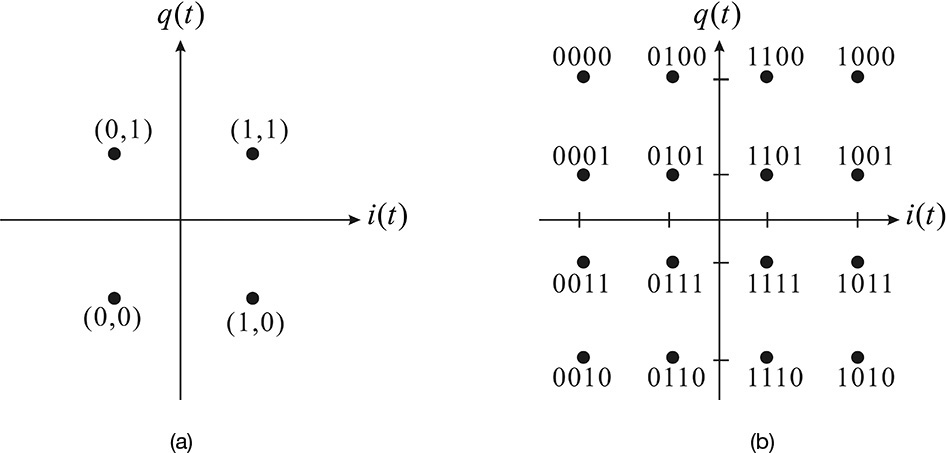

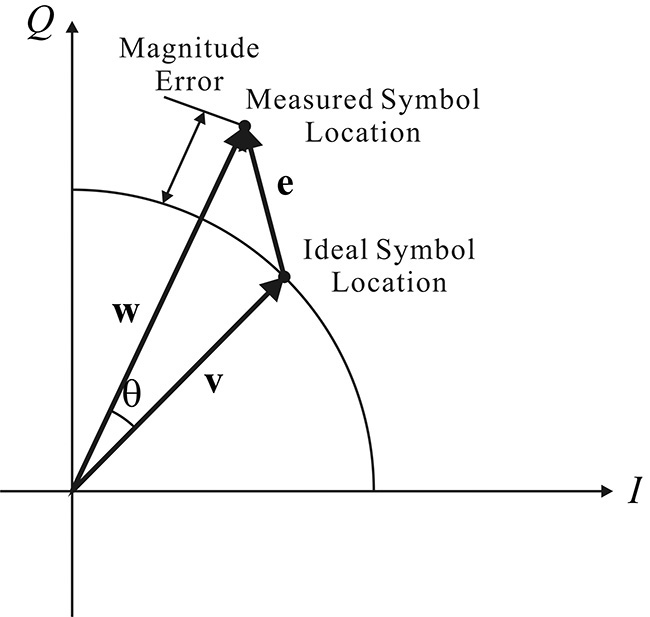

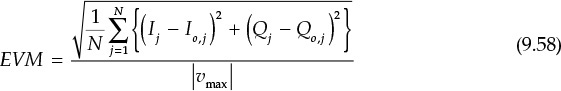

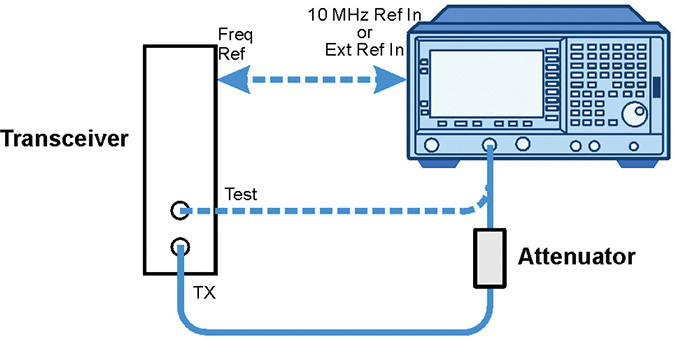

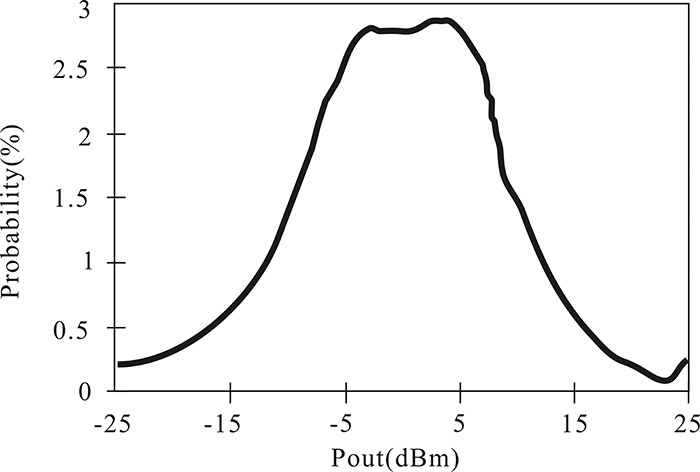

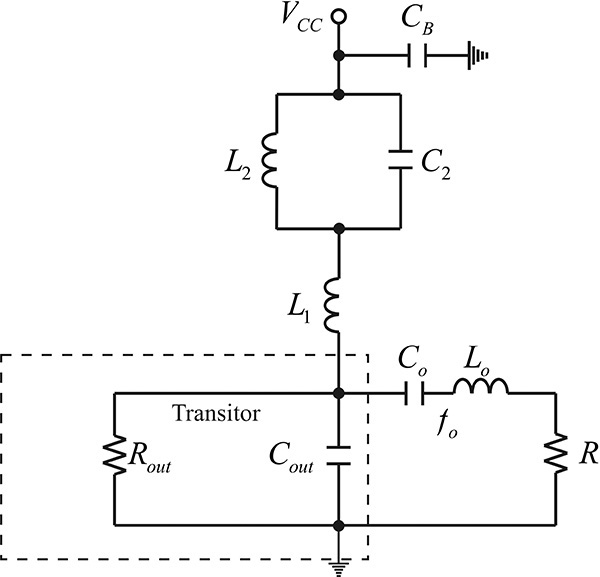

9.4 Classification

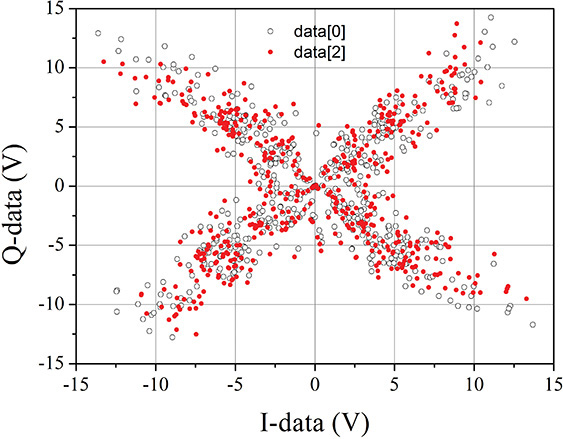

Power amplifiers are classified according to the DC bias point of the active device and the characteristics of the load network. This classification has a long history and is based on understanding the operation of the active device’s output behavior. Figure 9.18 shows the simplified IDS–VGS and IDS–VDS characteristics of an FET in order to classify the power amplifiers based on the DC bias point.

Figure 9.18 Simplified (a) IDS–VGS and (b) IDS–VDS and characteristics of an FET. Points QA, QB, and QC represent class-A, -B, and -C operating points, respectively.

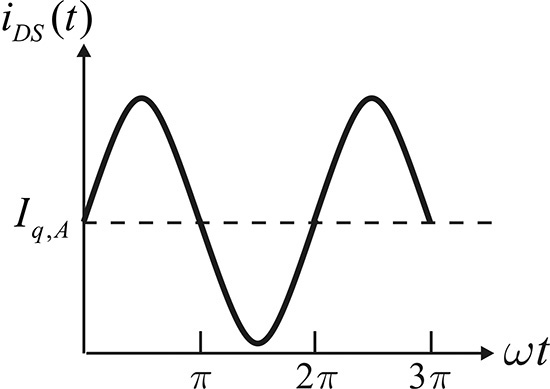

In the figure, when the amplifier is biased at VGS = VGS,A, VDS = VDD (operating point QA), considerable drain current Iq,A (quiescent drain current) flows in the amplifier even in the absence of RF input. A power amplifier that operates at this DC bias point is called a class-A power amplifier. When a sinusoidal input is applied to the class-A power amplifier, the output drain current iDS(t) conducts for a whole cycle of the sinusoidal input, as shown in Figure 9.19. Therefore, the input signal is faithfully amplified without distortion and shows a satisfactory linearity. However, as explained in section 9.1, the class-A power amplifier will have a maximum efficiency of 50%. In addition, the drain current flows even in the absence of RF input, which results in DC power consumption. Note that in the absence of RF input, the active device’s DC power consumption is maximum, which requires a large heat sink for sufficient heat dissipation.

The power consumption in the absence of RF input can be improved by moving the active device’s DC bias point. Suppose that the FET is DC biased at VDS = VDD and VGS is set at the FET’s pinch-off voltage VGS = –Vp, as shown in Figure 9.18. The DC bias point is called a class-B operating point and the power amplifier operating at this point is called a class-B power amplifier. In the class-B case, the drain current is Iq,B = 0 and will not flow in the absence of RF input. Thus, unlike the class-A amplifier, there is no DC power consumption in the absence of RF input. As another form of bias, VGS can be set smaller than the pinch-off voltage Vp of the FET. This DC bias point is called a class-C operating point and the power amplifier operating at the class-C DC bias point is called a class-C power amplifier. It should be noted that the drain current of the class-C power amplifier is also zero in the absence of RF input. On the other hand, the operating point is often mathematically interpreted as the DC bias for a negative drain current Iq,C in the absence of RF input, as shown in Figure 9.18. However, the real DC drain current is zero. The Iq,C is the projected value from the IDS–VGS characteristics curve. The drain current Iq,C at the class-C DC bias point indicates the required amplitude for the sinusoidal RF input applied to the gate to reach the pinch-off voltage. As such, the class-B and class-C power amplifiers have no DC power consumption in the absence of RF input, which is an advantage.

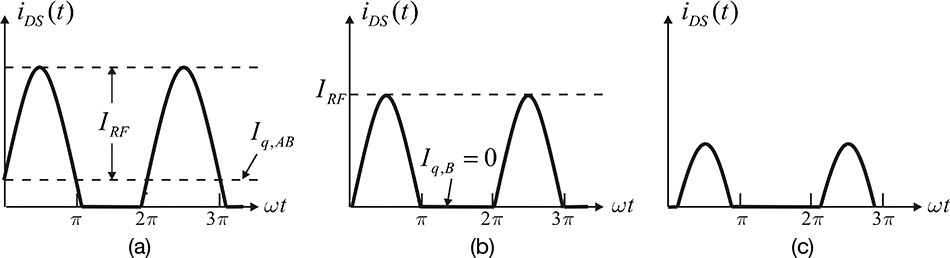

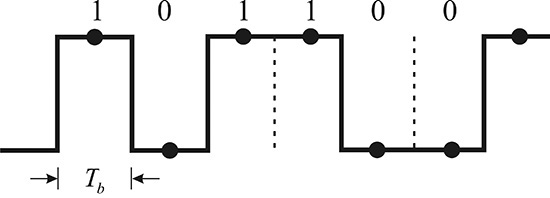

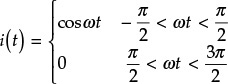

For a sinusoidal RF input applied to the class-B and C power amplifiers, the drain current iDS(t) flows for a conduction time interval determined according to their DC bias points, while it is zero for the remaining time interval, as shown in Figure 9.20. The time interval in which the drain current flows is called the conduction angle; the conduction angle of class-B is 180° while that of class-C is less than 180°. In addition, for an improvement in linearity and an increase in gain, a small DC current is made to flow in the absence of RF input, in which case the conduction angle becomes higher than 180°, an operation called class-AB.

Figure 9.20 Drain-current waveforms according to an operating point; (a) class-AB, (b) class-B, and (c) class-C

As shown in Figure 9.20, the drain current waveform shows the shape of a sinusoidal tip in the conduction angle; otherwise, the RF input waveform is cut off. Distortion can naturally be expected when the RF input signal is amplified through the drain current with the sinusoidal-tip shape. Suppose that a class-B or class-C power amplifier is employed in a communication system. The amplitude and phase of the waveform in Figure 9.20 vary according to the modulated input signal. Therefore, when the RF signal is amplified by the class-B or class-C power amplifier, as shown in Figure 9.20, a loss of information may result. However, if expanded in a Fourier series, the waveform of Figure 9.20 will result in harmonics of nfo. The harmonic signals can be removed using a filter after the amplification with the sinusoidal-tip-shaped waveforms. Both the amplitude and phase of the filtered waveform at the fundamental frequency are obviously proportional to the modulated RF input because the amplitude and phase of the sinusoidal-tip-shaped waveform in Figure 9.20 is proportional to the input signal. Thus, when the IDS–VGS characteristic is linear, as shown in Figure 9.18, a relatively faithful amplified signal can be obtained. However, the transfer characteristic, such as IDS–VGS, has some nonlinearity and results in distortion. Notably, the distortion becomes more significant as the operation point moves into a deeper class-C.

Previous explanations assume that the output of the active device is considered to be a transconductance-type current source. The output resistance of the current source is ignored. In a case where the output resistance cannot be ignored, it can be included in the load network. Thus, the necessary assumption for a transconductance-type current source is that the amplitude of the input is not set sufficiently large to drive the active device into the saturation region.

In the case of the class-D and class-E power amplifiers that are introduced in this section, the active device does not operate on the basis of the transconductance-type current source. The active device in class-D and class-E operations is assumed to be a switch. That is, when the input signal is sufficiently large, the active device no longer acts as a transconductance-type current source but instead functions as a switch. The modeling of an active device as a switch becomes more appropriate when the active device is driven by a square wave. Using the square wave can significantly increase efficiency, an operation that will be explained in this section. The classification of a class-F amplifier is somewhat ambiguous. Most of these amplifiers are classified according to the load network’s characteristics.

9.4.1 Class-B and Class-C Power Amplifiers

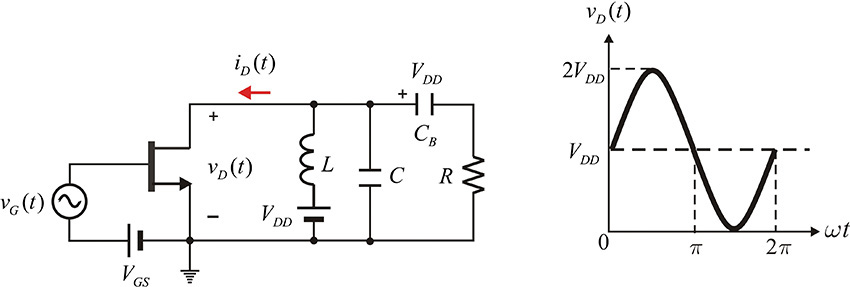

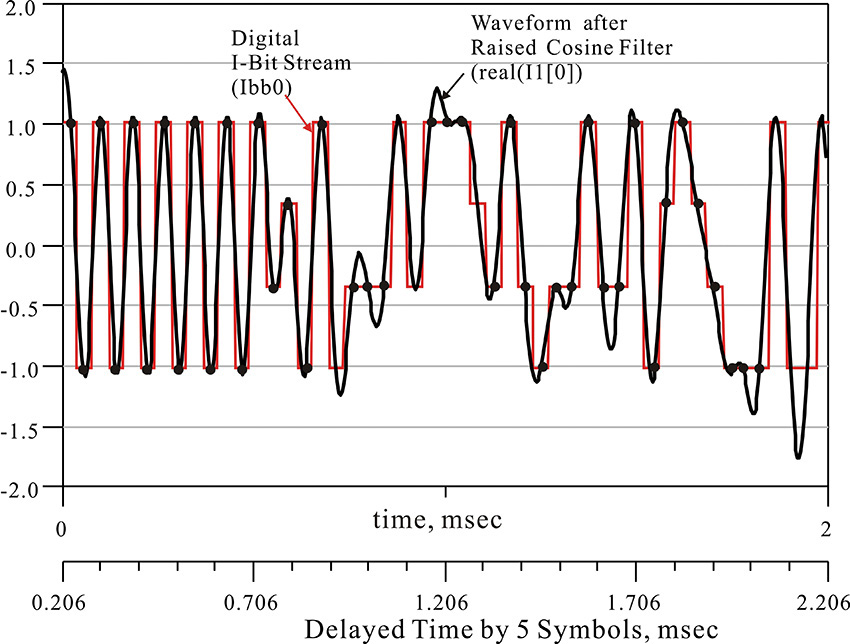

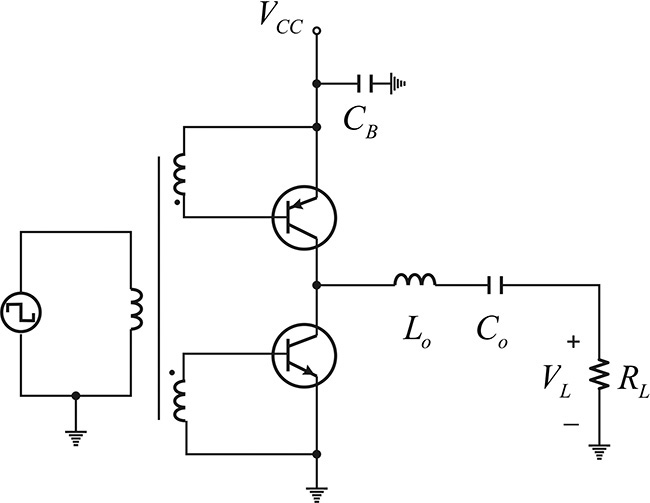

Figure 9.21 shows class-B and class-C power amplifier configurations. In that figure, the transistor can operate in class-AB, class-B, or class-C, depending on the DC bias voltage VGS. Here, vG(t) represents the RF input signal and the drain of the FET is biased at a DC voltage VDD. Capacitor CB at the output is a DC block capacitor. Inductor L forms a parallel resonant circuit with the capacitor C at the fundamental frequency fo.

Figure 9.21 Class-B and class-C power amplifier configuration and drain-voltage waveform. The gate bias voltage VGS sets the operating point of the class-B or -C accordingly. Capacitor CB is a DC block capacitor and the parallel resonant circuit at the fundamental frequency is formed by RLC. Due to the parallel resonance, the sinusoidal waveform appears at the drain and load.

The Q = ωoCR of the parallel resonant circuit is assumed to be sufficiently large. Thus, the impedance of the parallel resonant circuit is 0 at all harmonics except at the fundamental frequency. Consequently, the voltage due to the harmonic currents is 0 and does not appear across the load resistor R. Only the sinusoidal voltage due to the fundamental current appears across R. The voltage across R is sinusoidal and the drain voltage vD(t) is thus a sinusoidal voltage waveform raised by supply voltage VDD due to the DC voltage across the DC block capacitor, as shown in Figure 9.21. Since the supply voltage VDD is fixed, by selecting an appropriate load resistor R, the maximum peak voltage can reach VDD. It must be noted that a negative voltage does not appear at the drain. When an RF input VGcos(ωt) is applied, as shown in Figure 9.22, the output waveform of the drain current can be written as

Figure 9.22 Drain-current waveform that depends on the DC bias voltage VGS. According to VGS, the drain current may have a class-B or -C sinusoidal-tip-shaped waveform.

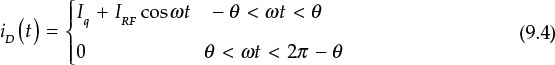

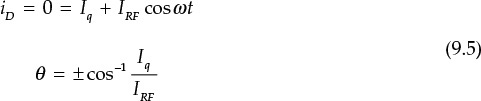

The Iq in Equation (9.4) becomes the DC quiescent current that flows in the absence of RF input. That is, Iq = 0 when the amplifier operates in class-B and in class-C when Iq < 0. In addition, IRF is the amplitude of the fundamental drain current. Using Equation (9.4), the conduction angle θ can be determined as expressed in Equation (9.5).

Now, using θ, Equation (9.4) can be rewritten and expressed as Equation (9.6).

Thus, the maximum current is expressed in Equation (9.7).

Expanding iD(t) in a Fourier series,

iD(t) = I0 + I1 cosωt + I2 cos 2ωt + ···

where the DC current component can be obtained as shown in Equation (9.8)

and the fundamental wave component I1 and harmonic components In can be expressed as Equations (9.9a) and (9.9b),

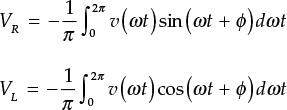

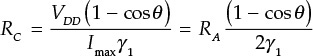

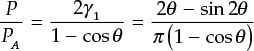

where γ0 and γ1 are functions of the conduction angle. Thus, denoting the voltage at fundamental frequency as V1, the drain efficiency can be computed as shown in Equation (9.10).

Here, ξ is defined as

and, since V1 < VDD, generally ξ ≤ 1. Therefore, by substituting ξ = 1 and θ = ½π into Equation (9.10), the maximum efficiency of a class-B amplifier, ηB,max is expressed in Equation (9.11).

From Imax in Equation (9.7), the value of the load giving maximum output power is given by Equation (9.12).

Then, the maximum output power is expressed in Equation (9.13).

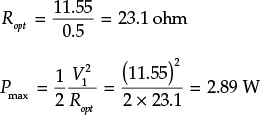

Calculate the optimum impedance Ropt of a 20-W class-B power amplifier for VDD = 20 V.

Solution

From Equation (9.13),

The meaning of the optimum load in Equation (9.12) can be understood by using a load line at the device output plane, which represents the trajectory of the voltage vD(t) and current iD(t). Using vD(t) and iD(t) in Figure 9.22, the load line can be drawn as shown in Figure 9.23. In that figure, the optimum load value that gives maximum output power in a class-B amplifier in Equation (9.12) can be easily inferred from Figure 9.23. In addition, the load resistance of a class-A amplifier that gives maximum output power is double that of the class-B amplifier. Also, from the load line of the class-C amplifier, as the conduction angle decreases, the optimum load resistance that gives maximum output power can also be seen to decrease, as shown in Figure 9.23.

Figure 9.23 Load lines of power amplifiers operating with class-A, -B, and -C. The optimum resistance is increasing as the class moves from C to A.

Set up a 1-A half-wave current source in ADS and configure the output circuit of a class-B amplifier. Set the load value from Equation (9.12) and confirm the voltage waveform vD(t) and drain efficiency. Also, plot the load line.

Solution

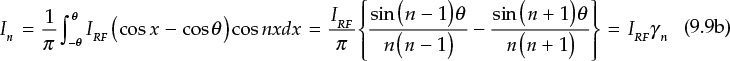

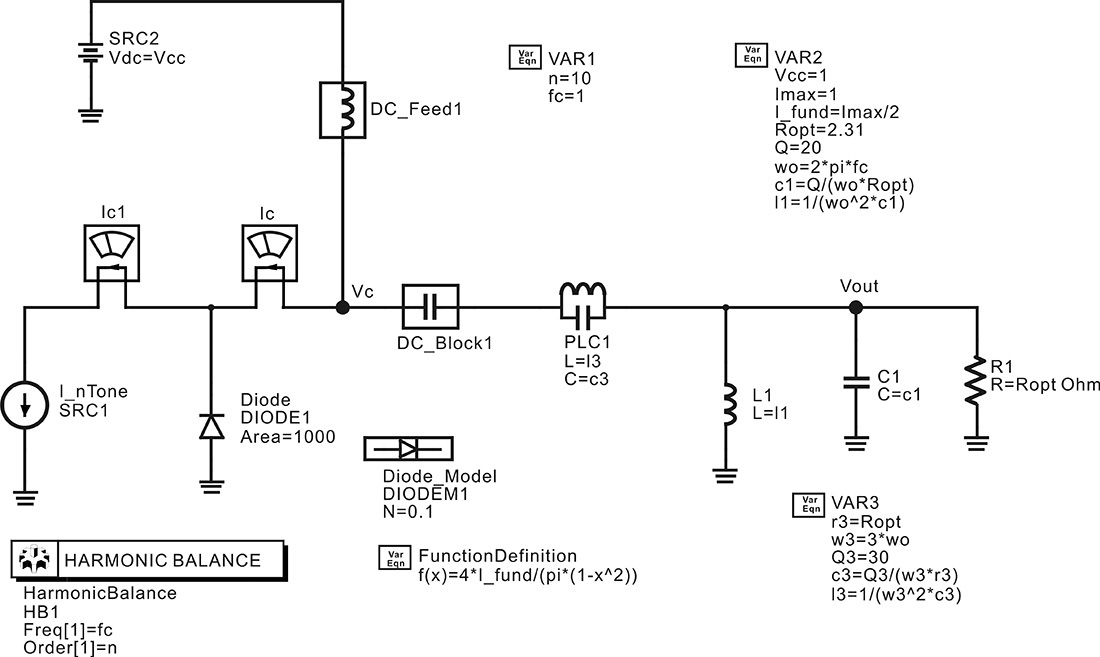

A half-wave current source can be configured in ADS using the n–tone current source, as shown in Figure 9E.3. The Fourier series of the half-wave current source,

Figure 9E.3 Half-wave current source configuration. The half-wave current source is implemented using a Fourier series.

can be expressed as

It should be noted that the Fourier series uses the two-sided spectra while the phasor uses only the positive frequency, that is, the one-sided spectrum. As a result, when expressed as a phasor, and for the harmonics n ≠ 0, the doubling of the value of In is required. In addition, since harmonics are, by default, represented by phasors in ADS, the harmonic phasor is represented by doubling the coefficient of the Fourier series given in the equations above. Thus, the half-wave current source can be configured as shown in Figure 9E.3. Note that I1 (I_fund) in Figure 9E.3 represents the phasor value and is set to Imax/2. The values of the other harmonics are accordingly set using I1. The output voltage vout across 1 Ω is used to check whether the expanded harmonic current of the Fourier series correctly produces the half-wave waveform in the time domain.

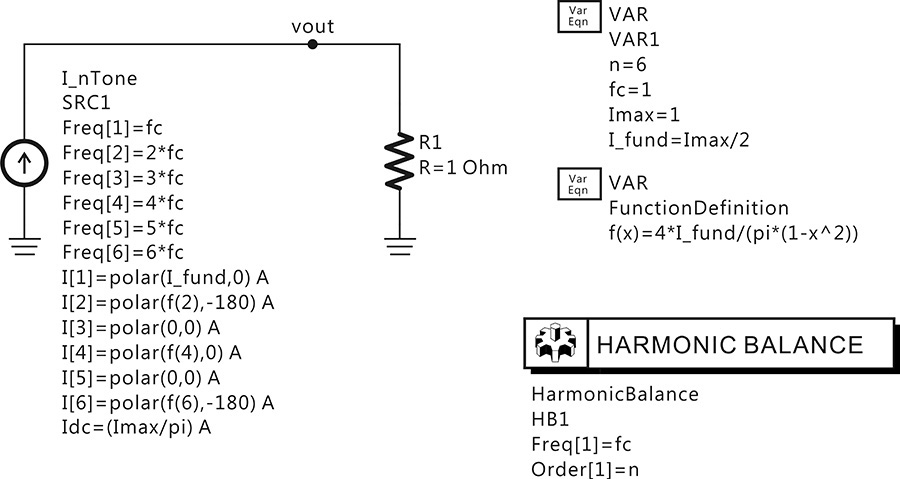

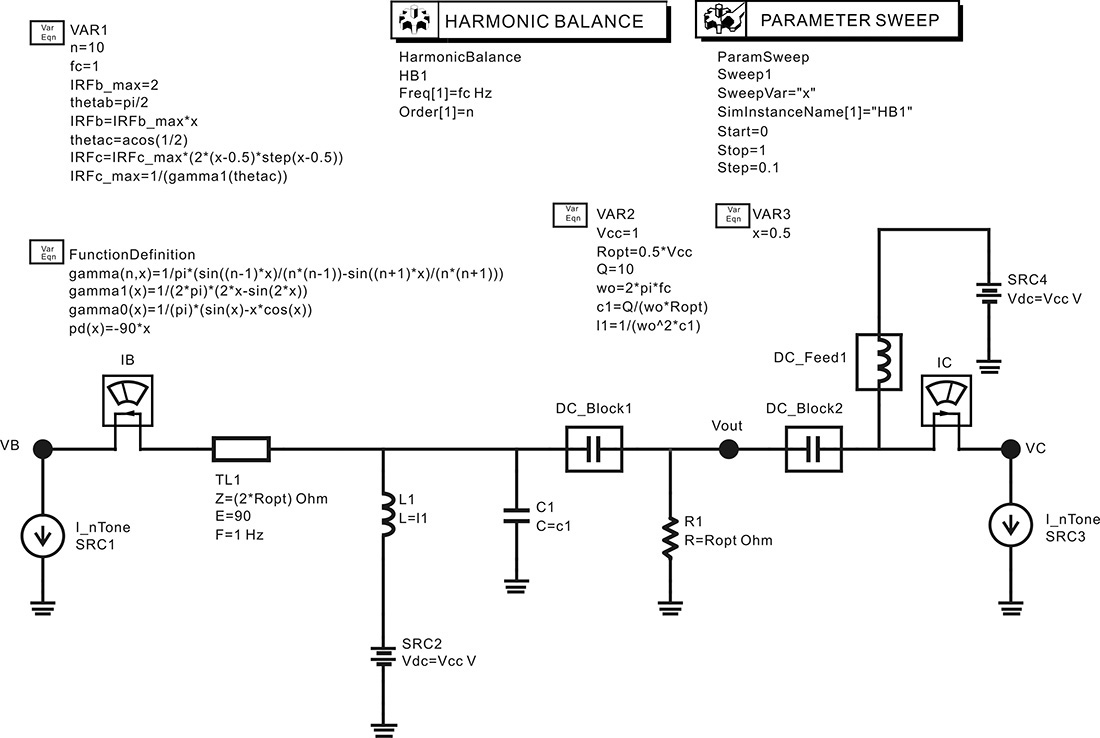

After the verification of the half-wave waveform, the output circuit of the class-B power amplifier can be configured as shown in Figure 9E.4. The current source of Figure 9E.3 is employed in the circuit of Figure 9E.4. The value of Imax in Figure 9E.4 is set to 1 A and the maximum value of the half-wave current source is thus 1 A. Using the maximum current value, the value of the optimum load Ropt can be computed to be 2Vcc from Equation (9.12). Also, in order to filter out harmonics, the parallel resonant circuit must have a high Q. The Q value of the parallel resonant circuit is set to Q = 10. Using Q and Ropt, the values of the inductor and the capacitor that constitute the parallel resonant circuit can be calculated.

Figure 9E.4 Output circuit of a class-B power amplifier. The current source is a half-wave and L1 and C1 are resonant at the fundamental frequency. The Q value of the parallel resonant circuit is set to 10.

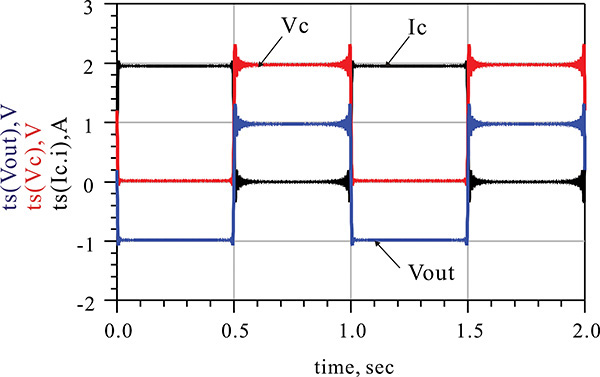

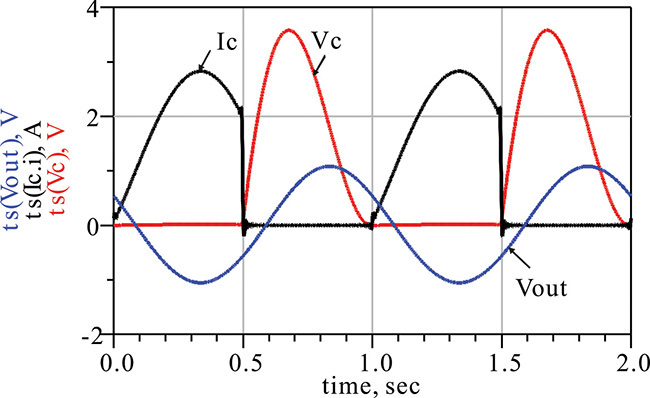

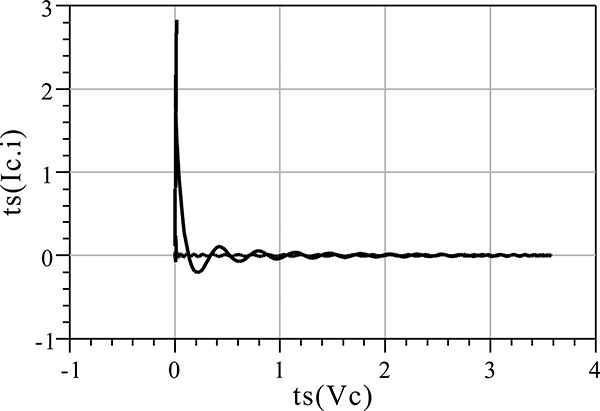

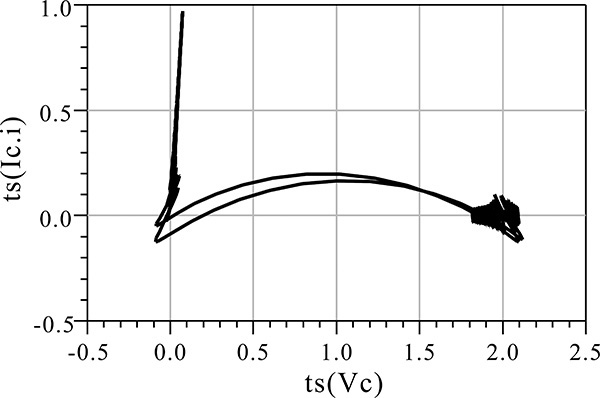

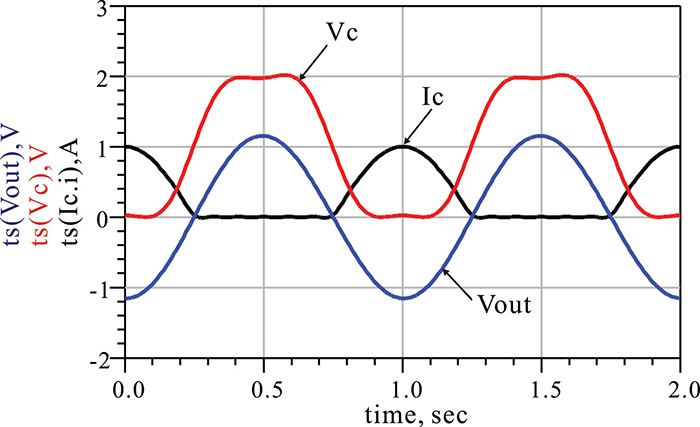

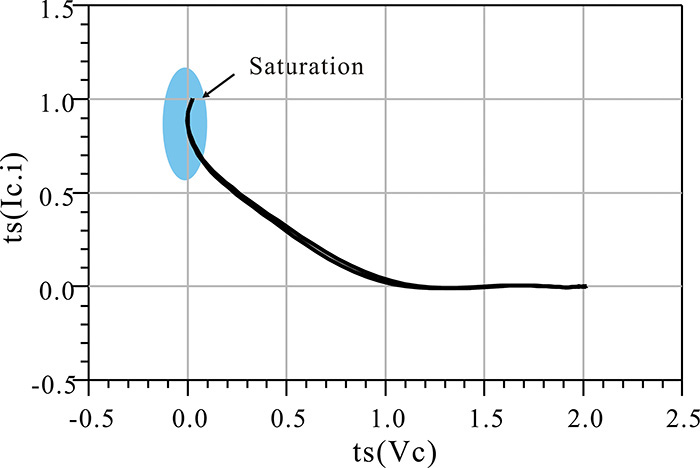

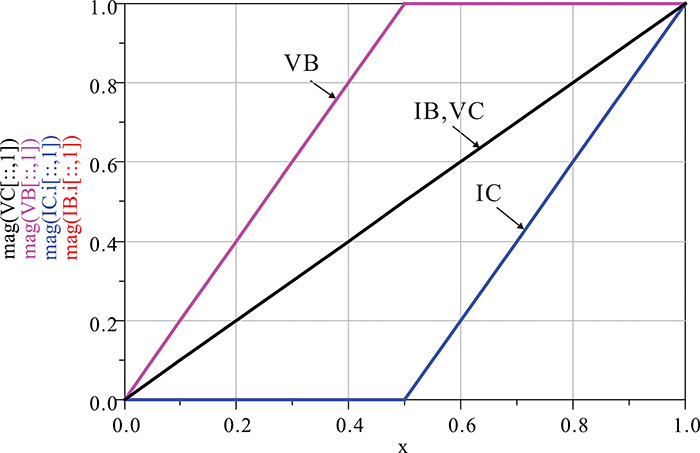

With the current and voltage waveforms shown in Figure 9E.5, plotting the current versus the voltage gives the load line, which is shown in Figure 9E.6. Since the voltage is not an exact sinusoidal waveform and has a slight distortion, the load line in Figure 9E.6 is not an exact straight line and shows a slight disparity.

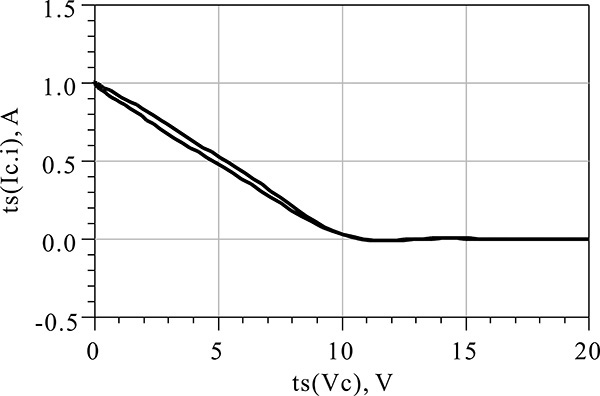

Figure 9E.5 Voltage Vc(t) and current Ic(t) waveforms. Vc(t) is almost sinusoidal while Ic(t) is a half-wave current. The function ts(⋅) generates the time-domain waveform using the set of harmonic voltages or currents.

Figure 9E.6 Load line. Note that the load line is the locus of voltage Vc(t) with respect to current Ic(t).

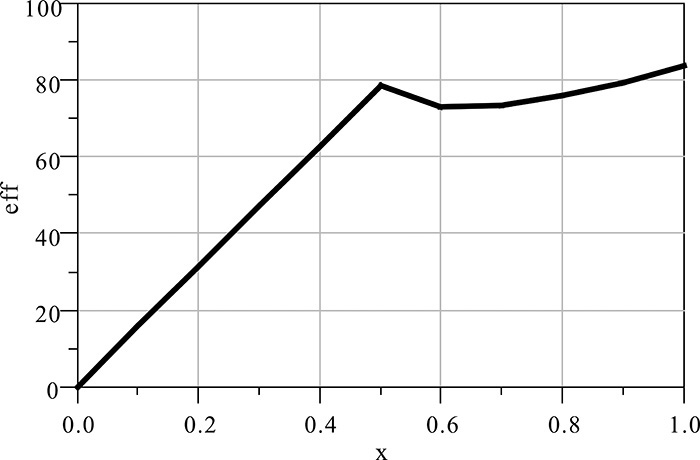

In order to calculate the efficiency, the equations in Measurement Expression 9E.1 are entered in the display window.

![]() Vcc=10

Vcc=10

![]() Ropt=2*Vcc

Ropt=2*Vcc

![]() Idc=real(Ic.i[0])

Idc=real(Ic.i[0])

![]() eff=(mag(Vout[1]))**2/(2*Ropt)/(Vcc*Idc)*100

eff=(mag(Vout[1]))**2/(2*Ropt)/(Vcc*Idc)*100

Measurement Expression 9E.1 Equations entered in the display window to calculate the efficiency

The calculated efficiency is 78.55%, which is close to the maximum efficiency of π/4 of a class-B power amplifier.

From Equation (9.10), the maximum efficiency is obtained when ξ = 1. The maximum efficiency due to variation in the conduction angle can be expressed as Equation (9.14).

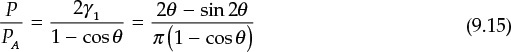

In addition, normalizing the maximum output power P, which varies with respect to the conduction angle, by the maximum power of the class-A power amplifier PA, gives Equation (9.15).

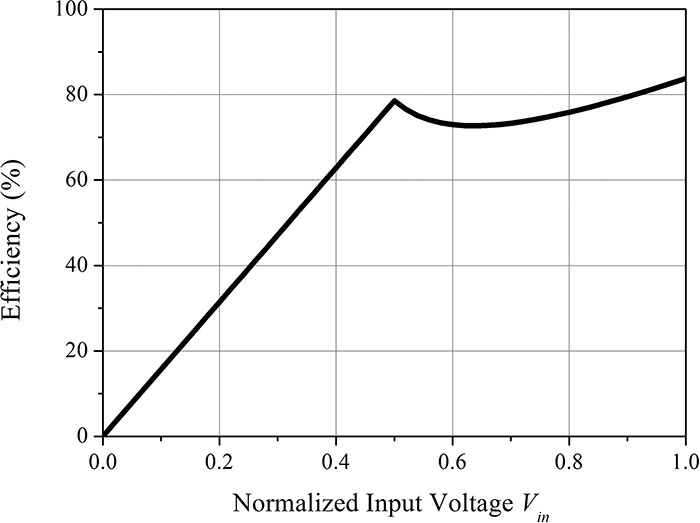

This is shown in Figure 9.24. As the conduction angle in that figure gets closer to 0, the efficiency gets closer to 100%. Also, as the conduction angle decreases, the output power decreases compared with that of the class-A power amplifier. Therefore, even though the efficiency is good, the maximum output power of the active device cannot be fully utilized. In addition, because the gain approaches 0, a significant increase in the input power is also required. Therefore, power amplifiers below class-B are not practically applicable even though they have increased efficiency.

Figure 9.24 The output power and efficiency variations vs. conduction angle. As the conduction angle decreases, the efficiency increases but the output power decreases.

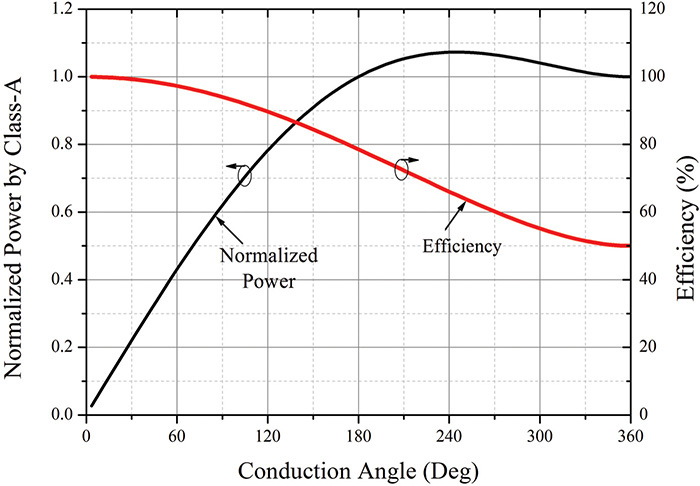

In the previous explanation using Figure 9.22, a class-B power amplifier is described as using a half-wave current source. It is noteworthy that a sinusoidal voltage appears across the load even though the output current of the active device shows a distorted half-wave current waveform. In addition, the phase and amplitude of the sinusoidal voltage across the load are proportional to those of the sinusoidal input. This indicates that the input signal is linearly amplified. In general, however, a class-B amplifier shows the PL–Pin characteristic shown in Figure 9.25. The PL–Pin characteristic has an S-shape for input power that causes distortion to appear in the output. This is primarily because the IDS–VGS characteristic is not linear. As a result, the PL–Pin characteristic has a distorted S-shape. This S-shaped PL–Pin characteristic can, to some extent, be corrected to a straight line by operating the amplifier in class-AB. An accurate measure of the distortion can be achieved by measuring the distortion for a modulated input signal, which will be described later in this chapter.

Figure 9.25 Typical output-power characteristic of a class-B amplifier for input power. Due to the nonlinearity of the ID–VGS characteristic, the S-shape curve appears.

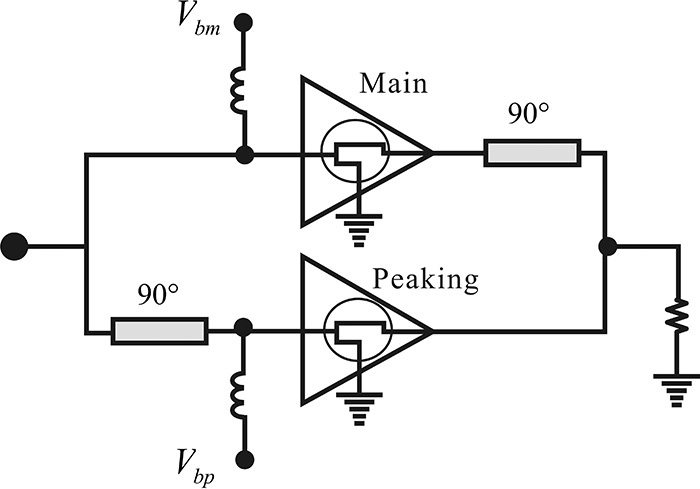

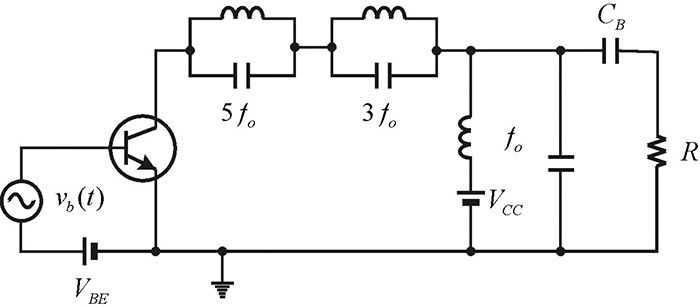

9.4.2 Class-D Power Amplifiers

A class-A amplifier’s efficiency can be significantly improved using a class-B operation. The collector or drain efficiency of the class-B operation is, however, still under 100%. A further improvement in efficiency that is closer to 100% can be achieved by operating the active device as a switch. In the class-B power amplifier, the active device operates as a transconductance-type current source that has a sinusoidal-tip-shaped waveform. When the sinusoidal input power is further increased, the active device’s output can be modeled as a switch that turns on and off according to the input signal. As the input increases, the output of the active device is shorted in the positive half cycle, while that output is opened in the negative half cycle. Note that because the active device’s output operates as a switch, there is no DC power consumption at that output. However, delivering a large input power to the active device can lead to real problems such as damaging the active device. Therefore, applying a square-wave input instead of a larger sinusoidal input makes the active device operate more like a switch. This can be implemented by inserting a drive circuit to convert the sine wave to a square wave. The active device then operates similarly to a switch according to the input signal. This operation is called class-D. Through the class-D operation, the drain or collector efficiency can be 100%. Table 9.2 shows the difference between the two operations when the active device is operated as a switch and as a transconductance-type current source.

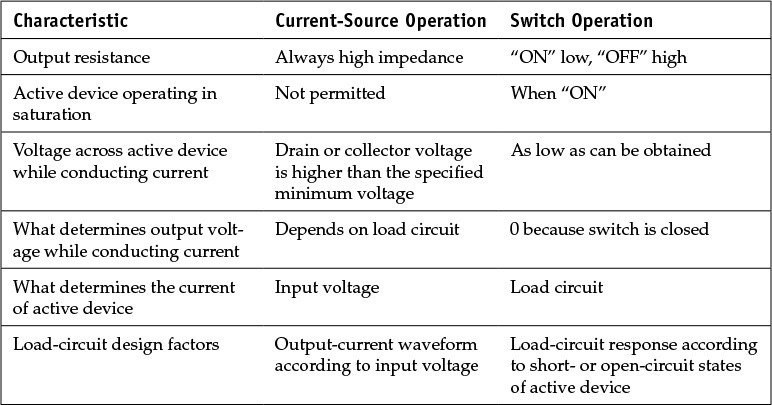

Table 9.2 Power amplifier design factors when an active device is operated as a current source or switch

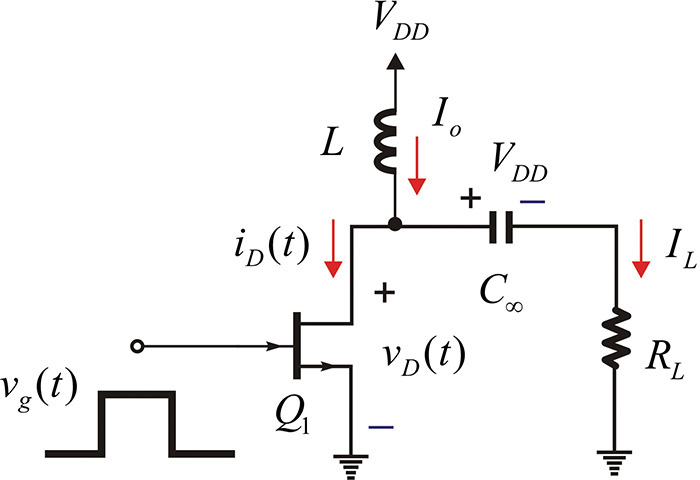

An example of the class-D power amplifier circuit is shown in Figure 9.26, where inductor L operates as an RFC and allows only DC current. The DC current value is assumed to be Io. Capacitor C∞ acts as a DC block and allows only DC voltage, which is intuitively determined to be VDD. Thus, when the active device is driven into the off state by the input signal, the voltage across the drain vD is given by

vD = VDD + ILRL

Figure 9.26 Class-D power amplifier circuit. Here, L and C∞ are an RFC and a DC block. The application of the square wave makes the transistor operate as a switch.

In addition, when the active device is on, vD is 0 and

vD = 0 = VDD + ILRL

Thus, the drain voltage alternates from 0 to VDD + ILRL according to the active device’s state, which changes from on to off. In contrast, when the active device is on, IL the current flowing through load RL is obtained as

and the drain current becomes

iD = Io – IL

Note that when the device is off, the drain current is 0, and when the device is on, the drain current has a value of Io – IL. Since the DC component must be Io, Io – IL = 2Io, then

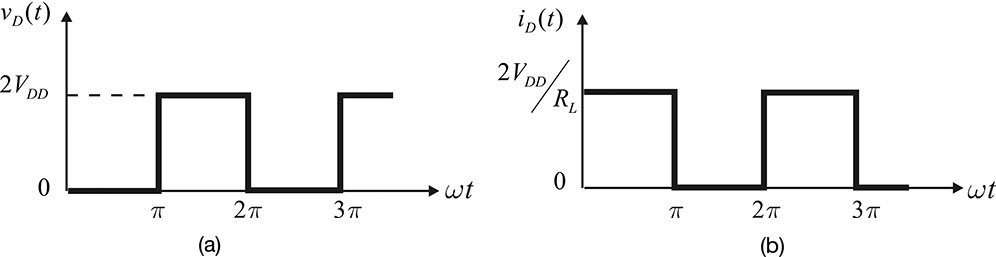

The resulting voltage and current waveforms are shown in Figure 9.27.

Using the switch provided in ADS, verify the class-D operation of the circuit in Figure 9.26.

Solution

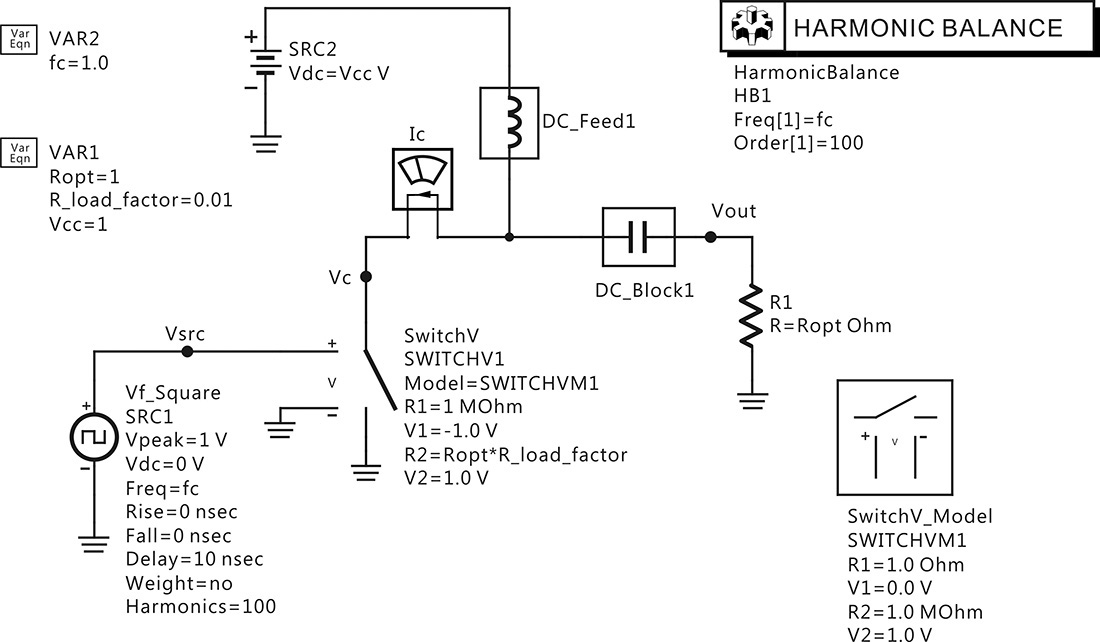

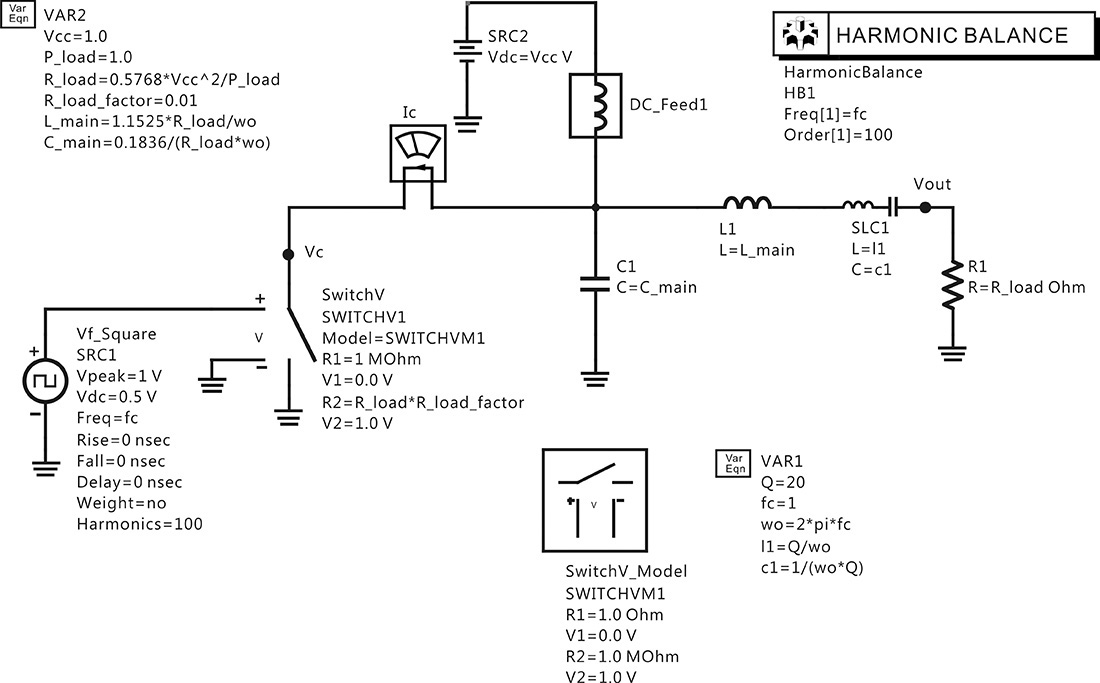

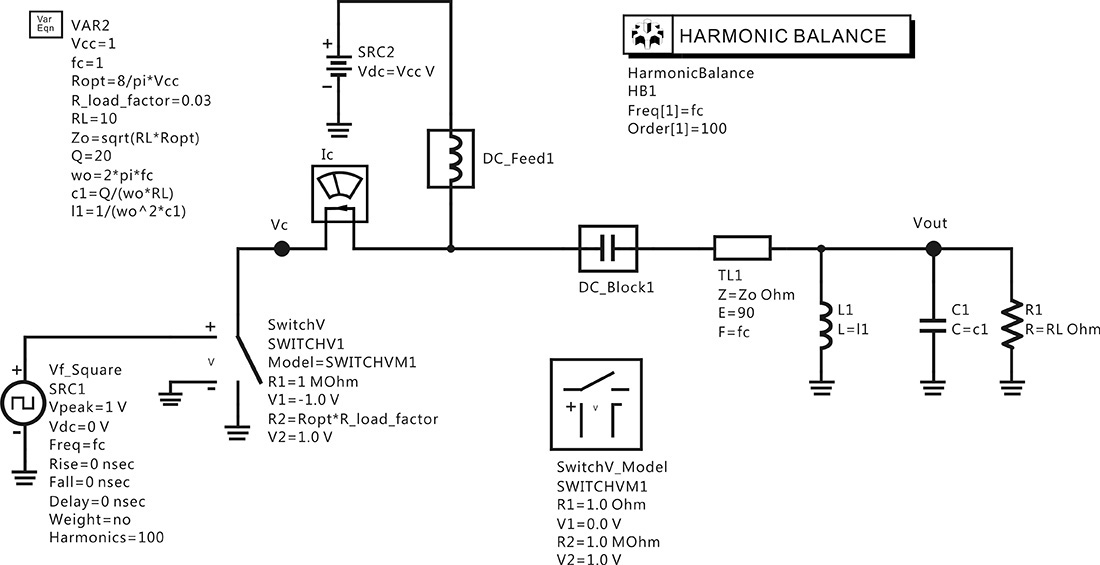

A class-D power amplifier using the switch is as shown in Figure 9E.7. The drive signal is a square wave that varies between 1 and –1 with respect to time as the Vdc = 0 of the square-wave source. The load value is set to Ropt and the resistance of the switch for –1 V is set to 1 MΩ and for 1 V to Ropt*R_load_factor. Note that R_load_factor is set to 0.01 Ω, which is sufficiently small compared with Ropt.

Figure 9E.7 A class-D power amplifier simulation. The switch is modeled by SwitchV, which has a resistance 1 MΩ at –1 V Vsrc input and has an on-resistance of Ropt*R_load_factor at 1 V Vsrc input.

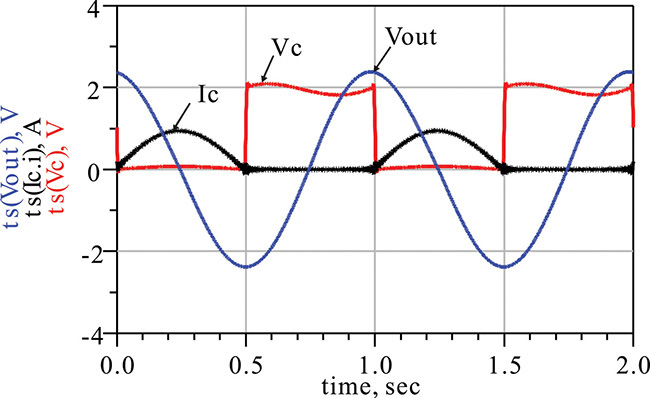

The simulated waveforms of this setup are shown in Figure 9E.8. In that figure, when the voltage is maximum, the current is 0 and vice versa. The power consumption of the DC voltage source SRC2 can be seen to be 1 W. Since the output power is 1 W, the efficiency can be seen to be 100%.

Figure 9E.8 Simulation results; (a) drain current and voltage, and (b) output voltage. Note that the average DC value of the load voltage Vout is 0. At the edge of the waveforms, ringing occurs due to Gibb’s phenomenon.

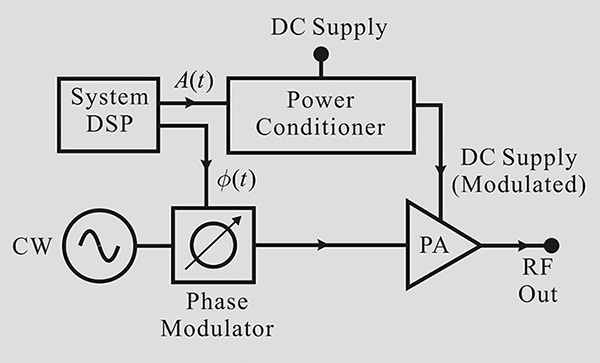

With the class-D operation, the active device’s output switches on/off according to the phase of the input signal. However, even though the phase information of the input signal is preserved at the amplifier output, the amplifier shows some losses to the amplitude information. The technique for solving this problem is that the amplitude and phase of the input voltage are separated using signal processing, and a square wave that varies according to the phase of the input signal is used as the driving input for the amplifier. The amplitude information can be restored by varying the supply voltage VDD in Figure 9.26 according to the amplitude of the input signal. Since the amplitude of the output signal of the class-D amplifier is related only to the supply voltage, the amplitude and phase information of the input signal can be restored at the amplifier output without any loss.

Even after solving the problem of the loss of the amplitude information, a significant amount of harmonics appears at the output, which presents another problem. A separate filter is required to remove the harmonics. There are several efficient ways of dealing with the harmonic problem of the class-D power amplifier. The voltage and current switching technique shown in Figure 9.28 is one of the ways to deal with the harmonic problem; see reference 3 at the end of this chapter for more information.

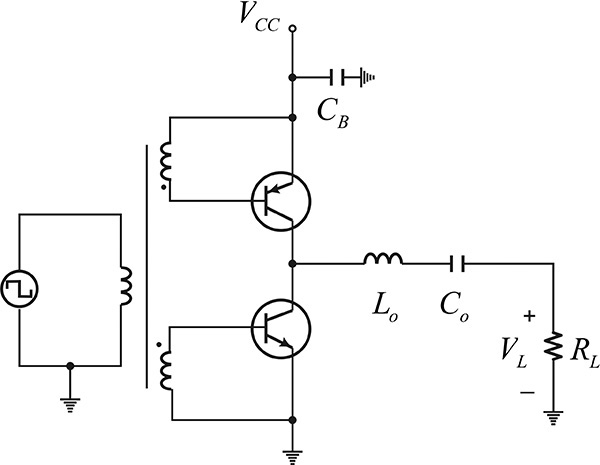

Figure 9.28 Voltage switching in a class-D power amplifier with a harmonics-eliminating filter. For high-state input, the npn transistor turns on and the current flows from the load RL to the npn transistor. For low-state input, the pnp transistor turns on the current flows from the pnp transistor to the load. The series resonant circuit eliminates the harmonics of the current and the sinusoidal voltage appears at the load.

In general, the efficiency of a practical class-D power amplifier seldom reaches 100%. One reason for the degraded efficiency is that the output voltage and current of the active device have finite rising and falling times, and a non-zero voltage appears when the device is conducting. Similarly, a non-zero current appears when the device is off. In addition, the charge on the drain capacitor, which is charged to maximum during the device’s off state, flows instantly to the drain when the device enters the on state. This sometimes causes permanent damage to the device and loss in the efficiency.

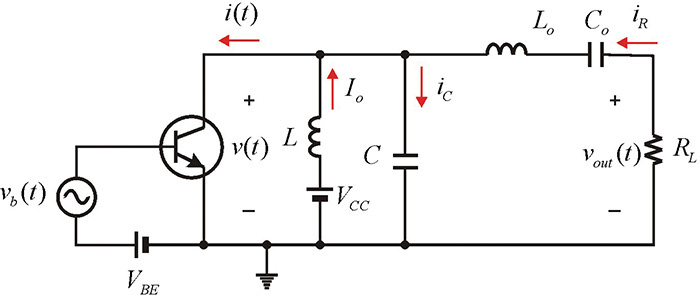

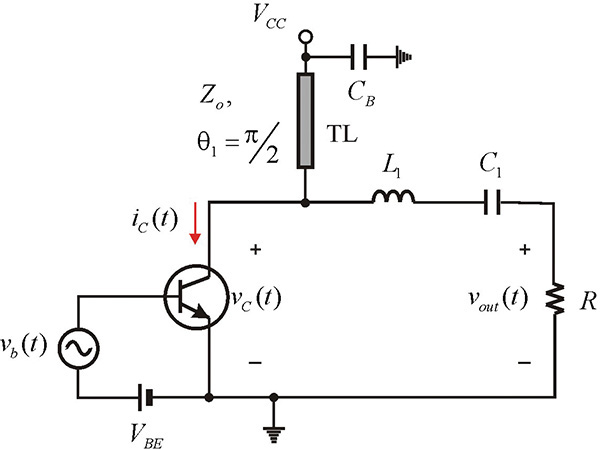

9.4.3 Class-E Power Amplifiers

The active device for a class-E amplifier, just as in a class-D amplifier, is operated as a switch. A patent for a class-E amplifier was applied for at the time when the class-E operation principle was still under development and was not yet a well-defined concept. The correct operation principle for the class-E amplifier was first analyzed by N. Sokal and A. Sokal in 1975, when they also presented its design approach.4 In addition, as there was a clear difference between the operation of the class-D and class-E amplifiers, the Sokals defined that operation as a class-E operation. The class-E power amplifier circuit developed by the Sokals is shown in Figure 9.29. However, there are various class-E amplifiers in addition to the class-E amplifier shown in that figure.

4. N. O. Sokal and A. D. Sokal, “Class E-A New Class of High-Efficiency Tuned Single-Ended Switching Power Amplifiers,” IEEE Journal of Solid-State Circuits 10, no. 3 (June 1975): 168–176.

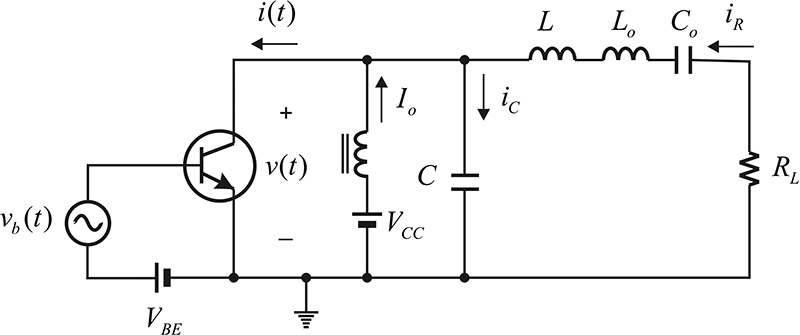

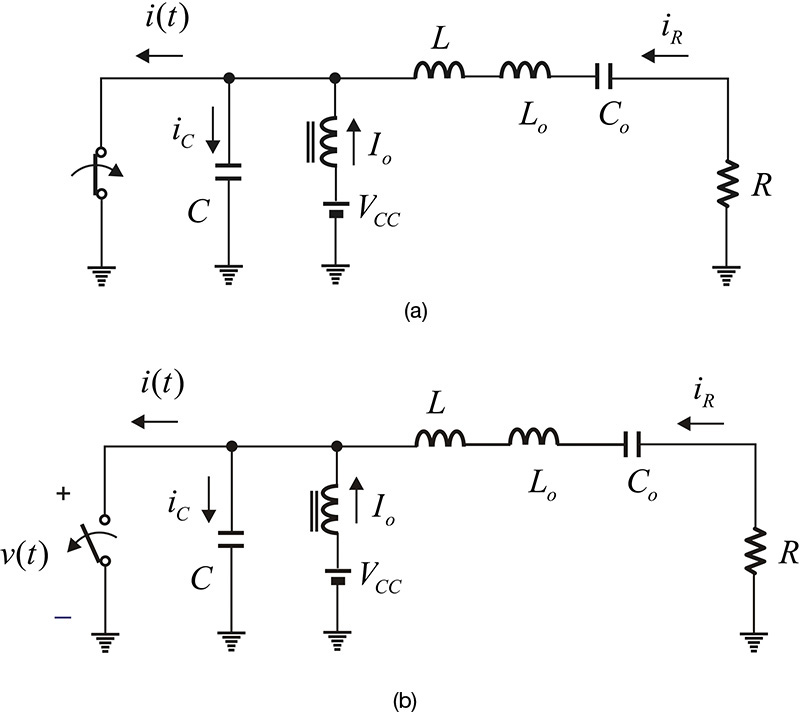

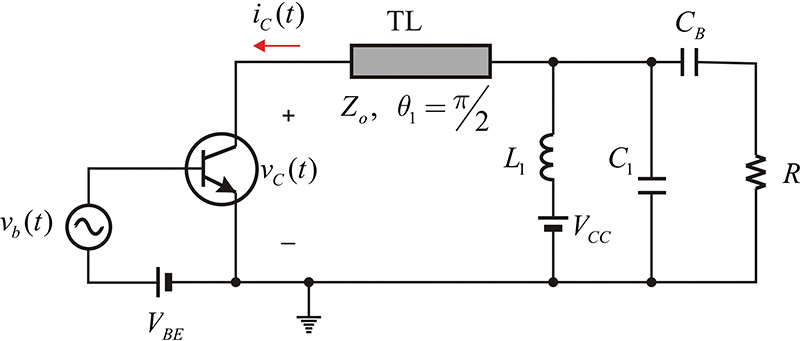

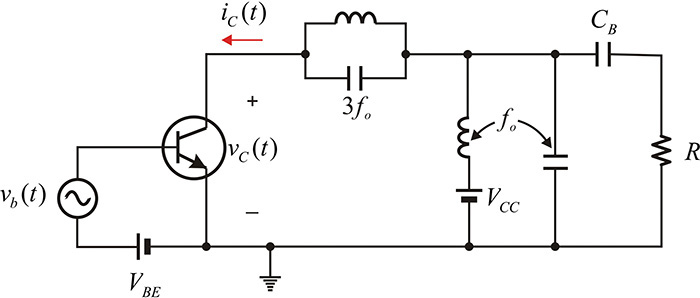

Figure 9.29 Class-E power amplifier configuration. The input vb(t) is a square wave and causes the transistor to operate as a switch. Lo and Co are resonant at the fundamental frequency. Note that the load circuit is not resonant at the fundamental frequency.

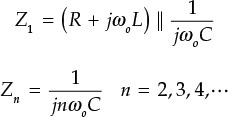

The configuration of the class-E input circuit shown in Figure 9.29 is the same as that for a class-D amplifier and the active device operates as a switch, which periodically turns on and off. Because of this, a transient analysis that depends on the on/off states is necessary to explain the class-E amplifier. Collector capacitance may exist in the collector terminal. In this case, the collector capacitance can be included in the capacitor C. DC current is supplied to the collector through the RFC, which is denoted as Io. The series resonator Lo–Co eliminates harmonics and is set to series resonate at the fundamental frequency. The Q of the series resonant branch is assumed to be sufficiently high, and harmonic currents other than those at the fundamental frequency cannot flow. Inductor L is added in series to the resonator; when the inductor is included, it makes the series resonant circuit resonate at a frequency lower than the fundamental (usually the resonator is said to be detuned). The class-E power amplifier generally has an optimized efficiency for the detuned series resonator, and it is analyzed by placing a separate L in series with the series resonator resonating at the fundamental frequency. It must be noted that the contribution of the inductor L appears only at the fundamental frequency and has no effects on the harmonics.

The output circuit of Figure 9.29 can be analyzed by considering the active device’s output as a switch. When the switch is opened, because a current Io + iR flows through capacitor C, the capacitor voltage rises and thus the collector voltage increases. On the other hand, when the switch is closed, the accumulated charge in the capacitor instantaneously flows through the switch in the form of an impulse current. In this case, even if there is a small voltage on the switch, power loss in the switch increases. This condition is not desirable for optimized efficiency. If the switch is open for the interval of 0.5T ≤ t ≤ T, the following must be satisfied at t = T for optimum efficiency, as expressed in Equation (9.16):

In addition to the impulse current due to the capacitor, a current Io + iR flows into the collector when the switch is closed. Although this is not an impulse-type current as in the case of the capacitor, it can cause a current with a step discontinuity. As this current flows instantaneously into the collector, it also leads to a loss of efficiency. In order to make this loss 0, Equation (9.17) must be satisfied.

The conditions of this equation mean that the capacitor current iC = Io + iR should be zero just before the switch is turned on. Thus, at the instant when the switch is closed, the current does not flow and the discontinuity of the current does not appear. These two conditions become the optimum conditions of the class-E power amplifier.

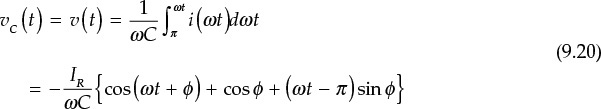

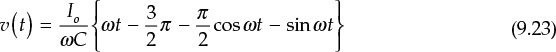

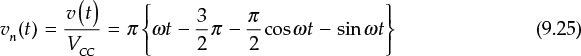

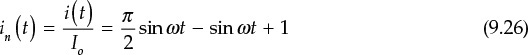

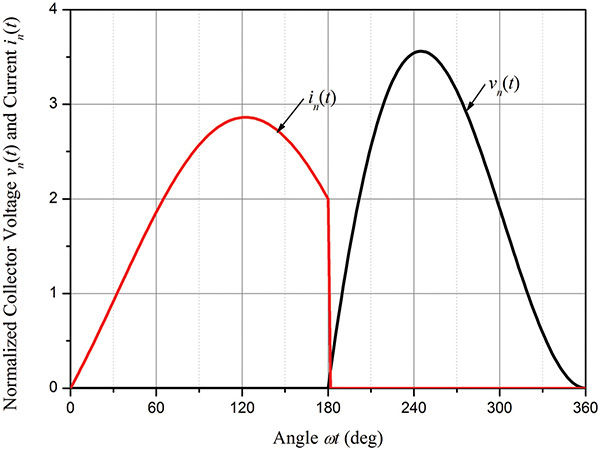

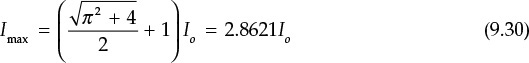

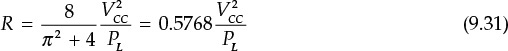

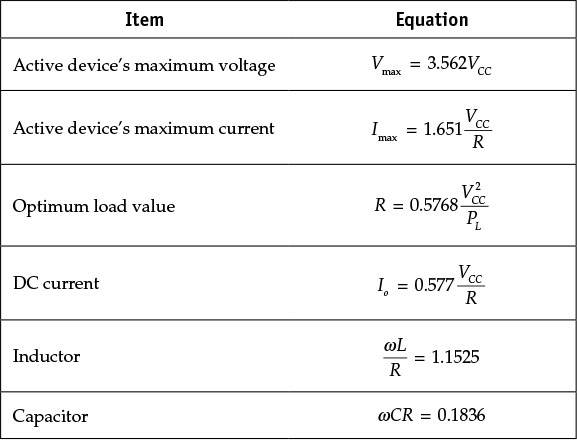

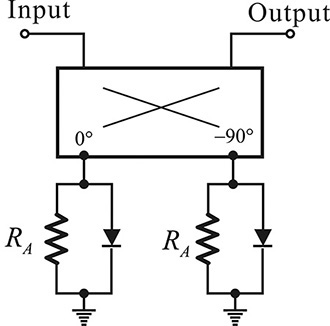

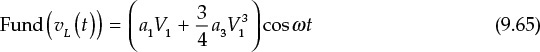

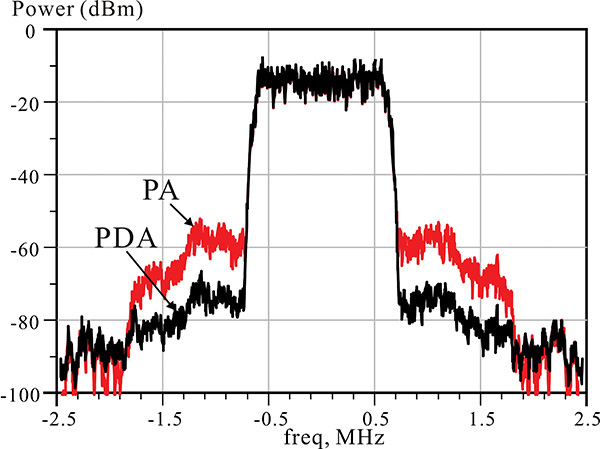

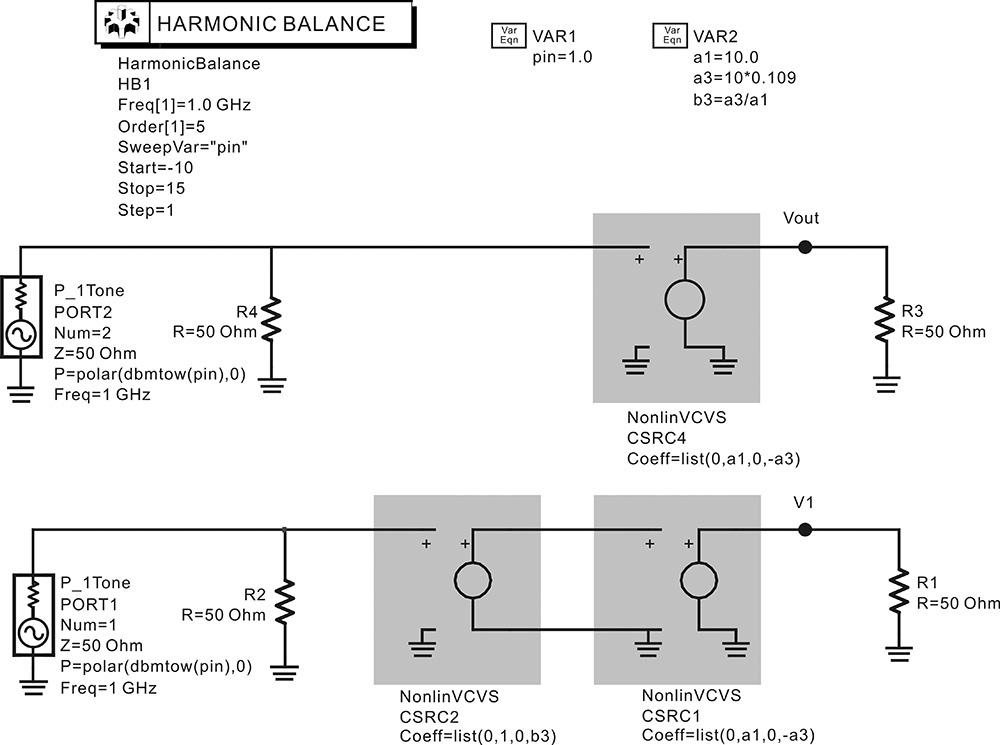

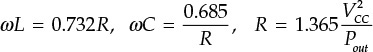

As a first step, the values of L and C that satisfy the optimum conditions for a given load R and supply voltage VCC should be determined through analysis. Then, the power delivered to the load PL and the DC current Io can be computed. Other parameters that must be determined include the maximum value of v(t), Vmax, and the maximum value of i(t), Imax. Using the determined Vmax and Imax, the active device appropriate for this class-E power amplifier can be selected.