Preface

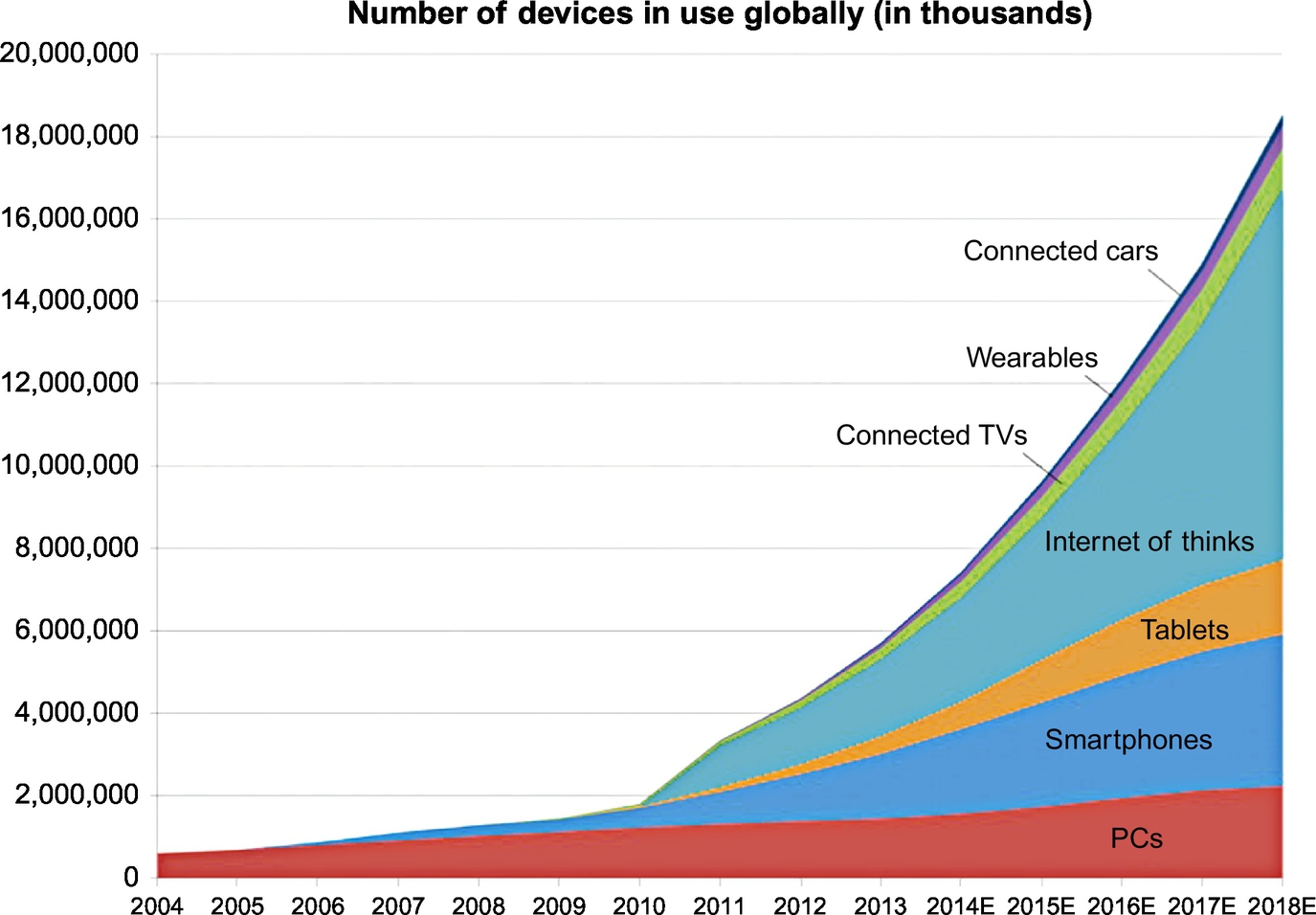

The adoption of rugged chips that can operate reliably even under extreme conditions has experienced an unprecedented growth. This growth is in tune with the revolutions related to mobile systems and the Internet of Things (IoT), emergence of autonomous and semiautonomous transport systems (such as connected and driverless cars), and highly automated factories and the robotics boom. The numbers are astonishing—if we consider just a few domains (connected cars, wearable and IoT devices, tablets and smartphones), we will end up having around 16 billion embedded devices surrounding us by 2018, as Fig. 1 shows.

A distinctive aspect of embedded systems (probably the most interesting one) is the fact that they allow us to take computing virtually anywhere, from a car's braking system to an interplanetary rover exploring another planet's surface to a computer attached to (or even implanted into!) our body. In other words, there exists a mobility aspect—inherent to this type of systems—that gives rise to all sorts of design and operation challenges, high energy efficiency and reliable operation being the most critical ones. In order to meet target energy budgets, one can decide to (1) minimize error detection or error tolerance related overheads and/or (2) enable aggressive power and energy management features, like low- or near-threshold voltage operation. Unfortunately, both approaches have direct impact on error rates. The hardening mechanisms (like hardened latches or error-correcting codes) may not be affordable since they add extra complexity. Soft error rates (SERs) are known to increase sharply as the supply voltage is scaled down. It may appear to be a rather challenging scenario. But looking back at the history of computers, we have overcome similar (or even larger) challenges. Indeed, we have already hit severe power density-related issues in the late 80s using bipolar transistors and here we are, almost 30 years after, still creating increasingly powerful computers and machines.

The challenges discussed above motivated us some years ago to ignite serious discussion and brainstorming in the computer architecture community around the most critical aspects of new-generation harsh-environment-capable embedded processors. Among a variety of activities, we have successfully organized three editions of the workshop on Highly-Reliable Power-Efficient Embedded Designs (HARSH), which have attracted the attention of researchers from academia, industry, and government research labs during the last years. Some of the experts that contributed material to this book had previously participated in different editions of the HARSH workshop. This book is in part the result of such continued efforts to foster the discussion in this domain involving some of the most influential experts in the area of rugged embedded systems.

This book was also inspired by work that the guest editors have been pursuing under DARPA's PERFECT (Power Efficiency Revolution for Embedded Computing Technologies) program. The idea was to capture a representative sample of the current state of the art in this field, so that the research challenges, goals, and solution strategies of the PERFECT program can be examined in the right perspective. In this regard, the book editors want to acknowledge DARPA's sponsorship under contract no. HR0011-13-C-0022.

We also express our deep gratitude to all the contributors for their valuable time and exceptional work. Needless to say, this book would not have been possible without them. Finally, we also want to acknowledge the support received from the IBM T. J. Watson Research Center to make this book possible.

Summer 2016