10

Distribution Feeder Analysis

The analysis of a distribution feeder will typically consist of a study of the feeder under normal steady-state operating conditions (power-flow analysis) and a study of the feeder under short-circuit conditions (short-circuit analysis). Models of all of the components of a distribution feeder have been developed in previous chapters. These models will be applied for the analysis under steady-state and short-circuit conditions.

10.1 Power-Flow Analysis

The power-flow analysis of a distribution feeder is similar to that of an interconnected transmission system. Typically, what will be known prior to the analysis will be the three-phase voltages at the substation and the complex power of all of the loads and the load model (constant complex power, constant impedance, constant current, or a combination). Sometimes, the input complex power supplied to the feeder from the substation is also known.

In Chapters 6, 7, and 8, phase frame models are developed for the series components of a distribution feeder. In Chapter 9, models are developed for the shunt components (static loads, induction machines, and capacitor banks). These models are used in the “power-flow” analysis of a distribution feeder.

A power-flow analysis of a feeder can determine the following by phase and total three-phase:

-

Voltage magnitudes and angles at all nodes of the feeder

-

Line flow in each line section specified in kW and kvar, amps and degrees, or amps and power factor

-

Power loss in each line section

-

Total feeder input kW and kvar

-

Total feeder power losses

-

Load kW and kvar based upon the specified model for the load

10.1.1 The Ladder Iterative Technique

Because a distribution feeder is radial, iterative techniques commonly used in transmission network power-flow studies are not used because of poor convergence characteristics [1]. Instead, an iterative technique called the “ladder technique” specifically designed for a radial system is used [2].

10.1.1.1 Linear Network

A modification of the “ladder” network theory of linear systems provides a robust iterative technique for power-flow analysis. A distribution feeder is nonlinear because most loads are assumed to be constant kW and kvar. However, the approach taken for the linear system can be modified to take into account the nonlinear characteristics of the distribution feeder. Figure 10.1 shows a linear ladder network.

For the ladder network, it is assumed that all of the line impedances and load impedances are known along with the voltage (VS) at the source. The solution for this network is to perform the “forward” sweep by calculating the voltage at node 5 (V5) under a no-load condition. With no load currents, there are no line currents; so the computed voltage at node 5 will equal that of the specified voltage at the source. The “backward” sweep commences by computing the load current at node 5. The load current I5 is:

I5=V5ZL5 (10.1)

For this “end-node” case, the line current I45 is equal to the load current I5. The “backward” sweep continues by applying Kirchhoff’s Voltage Law (KVL) to calculate the voltage at node 4:

V4=V5+Z45⋅I45 (10.2)

The load current I4 can be determined and then Kirchhoff’s Current Law (KCL) can be applied to determine the line current I34.

I34=I45+I4 (10.3)

FIGURE 10.1

Linear ladder network.

KVL is applied to determine the node voltage V3. The backward sweep continues until a voltage (V1) has been computed at the source. The computed voltage V1 is compared to the specified voltage VS. There will be a difference between these two voltages. The ratio of the specified voltage to the computed voltage can be determined as:

Ratio=VSV1 (10.4)

Because the network is linear, all of the line and load currents and node voltages in the network can be multiplied by the ratio for the final solution to the network.

10.1.1.2 Nonlinear Network

The linear network in Figure 10.1 is modified to a nonlinear network by replacing all of the constant load impedances by constant complex power loads as shown in Figure 10.2.

As with the linear network, the “forward” sweep computes the voltage at node 5 assuming no load. As before, the node 5 (end-node) voltage will equal that of the specified source voltage. In general, the load current at each node is computed by:

In=(SnVn)* (10.5)

The “backward” sweep will determine a computed source voltage V1. As in the linear case, this first “iteration” will produce a voltage that is not equal to the specified source voltage VS. Because the network is nonlinear, multiplying currents and voltages by the ratio of the specified voltage to the computed voltage will not give the solution. The most direct modification using the ladder network theory is to perform a “forward” sweep. The forward sweep commences by using the specified source voltage and the line currents from the previous “backward” sweep. KVL is used to compute the voltage at node 2 by:

FIGURE 10.2

Nonlinear ladder network.

V2=VS−Z12⋅I12 (10.6)

This procedure is repeated for each line segment until a “new” voltage is determined at node 5. Using the “new” voltage at node 5, a second backward sweep is started that will lead to a “new” computed voltage at the source. In this modified version of the ladder technique, convergence is determined by computing the ratio of difference between the voltages at the n − 1 and n iterations and the nominal line-to-neutral voltage. Convergence is achieved when all of the phase voltages at all nodes satisfy:

||Vn|−|Vn−1||Vnominal≤specified tolerance

Example 10.1 A single-phase lateral is shown in Figure 10.3.

The line impedance is:

z=0.3+j0.6 Ω/mile

The impedance of the line segment 1–2 is:

Z12=(0.3+j0.6)⋅30005280=0.1705+j0.3409 Ω

The impedance of the line segment 2–3 is:

Z23=(0.3+j0.6)⋅40005280=0.2273+j0.4545 Ω

FIGURE 10.3

Single-phase lateral.

The loads are:

S2=1500+j750S3=900+j500(kW + jkvar)

The source voltage at node 1 is 7200 V.

Use the modified ladder method to compute the load voltage after the second forward sweep.

Set initial conditions:

I12=I23=0 Vold=0 Tol=0.0001

The first forward sweep:

V2==Vs−Z12⋅I12=7200/0__V3=V2−Z23⋅I23=7200/0__Error=||V3|−|Vold||7200=1 (greater than Tol, start backward sweep)V3=Vold

The first backward sweep:

I3=((900+j500)⋅10007200/0__)*=143.0/−29.0_____ A

The current flowing in the line section 2–3 is:

I23=I3=143.0/−29.0______ A

The load current at node 2 is:

I2=((1500+j750)⋅10007200/0__)*=232.9/−27.5______ A

The current in line segment 1–2 is:

I12=I23+I2=373.8/−27.5______ A

The second forward sweep:

V2=VS−Z12⋅I12=7084.5/−0.7_____V3=V2−Z23⋅I23=7025.1/−1.0_____Error=||V3|−|Vold||7200=7084.5−72007200=0.0243 (greater than tolerance, continue)Vold=V3

At this point, the second backward sweep is used to compute the new line currents. This is followed by the third forward sweep. After four iterations, the voltages have converged to an error of 0.000017 with the final voltages and currents of:

[V2]= 7081.0/−.68_____[V3]= 7019.3/−1.02______[I12]= 383.4/−28.33_______[I23]= 146.7/−30.07______

10.1.2 General Feeder

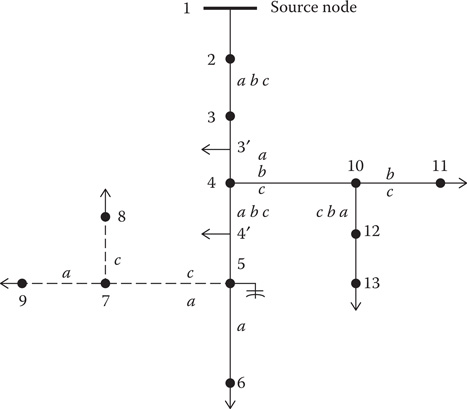

A typical distribution feeder will consist of the “primary main” with laterals tapped off the primary main and sublaterals tapped off the laterals, etc. Figure 10.4 shows an example of a typical feeder.

FIGURE 10.4

Typical distribution feeder.

In Figure 10.4, no distinction is made as to what type of element is connected between nodes. However, the phasing is shown, and this is a must. All series elements (lines, transformers, regulators) can be represented by the circuit in Figure 10.5. Note in Figure 10.4 that the lines between nodes 3 and 4 and between nodes 4 and 5 have “distributed” loads modeled at the middle of the lines. The model for the distributed loads was developed in Chapter 3. Connecting the loads at the center was only one of the three ways to model the load. A second method is to place one-half of the load at each end of the line. The third method is to place two-thirds of the load 25% of the way down the line from the source end. The remaining one-third of the load is connected at the receiving-end node. This “exact” model gives the correct voltage drop down the line in addition to the correct power-line power loss.

FIGURE 10.5

Standard feeder series component model.

In previous chapters, the forward and backward sweep models have been developed for the series elements. With reference to Figure 10.5, the forward and backward sweep equations are:

Forward sweep: [VLNabc]n=[A]⋅[VLNabc]m−[B]⋅[Iabc]nBackward sweep: [Iabc]n=[c]⋅[VLNabc]m+[d]⋅[Iabc]n (10.7)

In most cases, the [c] matrix will be zero. Long underground lines will be the exception. It was also shown that for the grounded wye–delta transformer bank, the backward sweep equation is:

[Iabc]n=[xt]⋅[VLNabc]n+[d]⋅[Iabc]m (10.8)

The reason for this is that the currents flowing in the secondary delta windings are a function of the primary line-to-ground voltages.

Referring to Figure 10.4, nodes 4, 10, 5, and 7 are referred to as “junction nodes.” In both the forward and backward sweeps, the junction nodes must be recognized. In the forward sweep, the voltages at all nodes down the lines from the junction nodes must be computed. In the backward sweeps, the currents at the junction nodes must be summed before proceeding toward the source. In developing a program to apply the modified ladder method, it is necessary for the ordering of the lines and nodes to be such that all node voltages in the forward sweep are computed and all currents in the backward sweep are computed.

10.1.3 The Unbalanced Three-Phase Distribution Feeder

The previous section outlined the general procedure for performing the modified ladder iterative technique. This section will address how that procedure can be used for an unbalanced three-phase feeder.

Figure 10.6 is the one-line diagram of an unbalanced three-phase feeder as shown in Figure 10.5.

FIGURE 10.6

Unbalanced three-phase distribution feeder.

The topology of the feeder in Figure 10.6 is the same as the feeder in Figure 10.5. Figure 10.6 shows more details of the feeder with step regulators at the source and a transformer bank at node 12. The feeder in Figure 10.6 can be broken into the “series” components and the “shunt” components. The series components have been shown in Section 10.1.2.

10.1.3.1 Shunt Components

The shunt components of a distribution feeder are:

-

Spot static loads

-

Spot induction machines

-

Capacitor banks

Spot static loads are located at a node and can be three-phase, two-phase, or single-phase, and connected in either a wye or a delta connection. The loads can be modeled as constant complex power, constant current, constant impedance, or a combination of the three.

A spot induction machine is modeled using the shunt admittance matrix as defined in Chapter 9. The machine can be modeled as a motor with a positive slip or as an induction generator with a negative slip. The input power (positive for a motor, negative for a generator) can be specified, and the required slip is computed using the iterative process described in Chapter 9.

Capacitor banks are located at a node and can be three-phase, two-phase, or single-phase, and can be connected in a wye or delta. Capacitor banks are modeled as constant admittances.

In Figure 10.6, the solid line segments represent overhead lines, while the dashed lines represent underground lines. Note that the phasing is shown for all of the line segments. In Chapter 4, the application of Carson’s equations for computing the line impedances for overhead and underground lines was presented. In that chapter, it is pointed out that two-phase and single-phase lines are represented by a 3 × 3 matrix with zeros set in the rows and columns of the missing phases.

In Chapter 5, the method for the computation of the shunt capacitive susceptance for overhead and underground lines was presented. Most of the times, the shunt capacitance of the line segment can be ignored; however, for long underground line segments, the shunt capacitance should be included.

The “node” currents may be three-phase, two-phase, or single-phase and consist of the sum of the spot load currents and one-half of the distributed load currents (if any) at the node plus the capacitor current (if any) at the node. It is possible that at a given node, the distributed load can be one-half of the distributed load in the “from” segment plus one-half of the distributed load connected to the “to” segment. In some cases, a “dummy” node is created in the center of the line, and the total distributed load is connected to this node.

10.1.4 Applying the Ladder Iterative Technique

Section 10.1.2 outlined the steps required for the application of the ladder iterative technique. Forward and backward sweep matrices have been developed in Chapters 6, 7, and 8 for the series devices. By applying these matrices, the computation of the voltage drops along a segment will always be the same regardless of whether the segment represents a line, voltage regulator, or transformer.

In the preparation of data for a power-flow study, it is extremely important that the impedances and admittances of the line segments are computed using the exact spacings and phasing. Because of the unbalanced loading and resulting unbalanced line currents, the voltage drops due to the mutual coupling of the lines become very important. It is not unusual to observe a voltage rise on a lightly loaded phase of a line segment that has an extreme current unbalance.

The real power loss in a device can be computed in two ways. The first method is to compute the power loss in each phase by taking the phase current squared times the total resistance of the phase. Care must be taken to not use the resistance value from the phase impedance matrix. The actual phase resistance that was used in Carson’s equations must be used. Developing a computer program calculating power loss this way requires that the conductor resistance is stored in the active database for each line segment. Unfortunately, this method does not give the total power loss in a line segment, since the power losses in the neutral conductor and ground are not included. In order to determine the losses in the neutral and ground, the method outlined in Chapter 4 must be used to compute the neutral and ground currents and then the power losses.

A second, and preferred, method is to compute the power loss as the difference of real power into a line segment minus the real power output of the line segment. Because the effects of the neutral conductor and ground are included in the phase impedance matrix, the total power loss in this method will give the same results as mentioned earlier, where the neutral and ground power losses are computed separately. This method can lead to some interesting numbers for very unbalanced line flows in that it is possible to compute what appears to be a negative phase power loss. This is a direct result of the accurate modeling of the mutual coupling between phases. Remember that the effects of the neutral conductor and the ground resistance are included in Carson’s equations. In reality, there cannot be a negative phase power loss. Using this method, the algebraic sum of the line power losses will equal the total three-phase power loss that was computed using the current squared times resistance for the phase and neutral conductors along with the ground current.

10.1.5 Let’s Put It All Together

At this point, the models for all components of a distribution feeder have been developed. The ladder iterative technique has also been developed. It is time to put them all together and demonstrate the power-flow analysis of a very simple system. Example 10.2 will demonstrate how the models of the components work together in applying the ladder technique to achieve a final solution of the operating characteristics of an unbalanced feeder.

Example 10.2

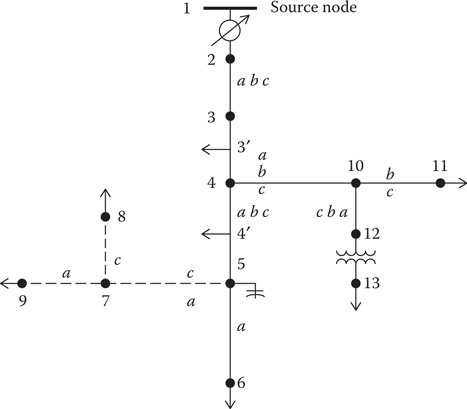

A very simple distribution feeder is shown in Figure 10.7. This system is the IEEE 4 Node Test Feeder that can be found on the IEEE website [3].

FIGURE 10.7

Example 10.2 feeder.

For the system in Figure 10.7, the infinite bus voltages are balanced three-phase of 12.47 kV line-to-line. The “source” line segment from node 1 to node 2 is a three-wire delta 2000 ft long line and is constructed on the pole configuration in Figure 4.7 without the neutral. The “load” line segment from node 3 to node 4 is 2500 ft long and is also constructed on the pole configuration in Figure 4.7 but is a four-wire wye; so the neutral is included. Both line segments use 336,400 26/7 ACSR phase conductors, and the neutral conductor on the four-wire wye line is 4/0 6/1 ACSR. Because the lines are short, the shunt admittance will be neglected. The 25°C resistance is used for the phase and neutral conductors:

336,400 26/7 ACSR: resistance at 25°C = 0.278 Ω/mile

4/0 6/1 ACSR: resistance at 25°C = 0.445 Ω/mile

The phase impedance matrices for the two line segments are:

[ZeqS]=[0.1414+j0.53530.0361+j0.32250.0361+j0.27520.0361+j0.32250.1414+j0.53530.0361+j0.29550.0361+j0.27520.0361+j0.29550.1414+j0.5353] Ω

[ZeqL]=[0.1907+j0.50350.0607+j0.23020.0598+j0.17510.0607+j0.23020.1939+j0.48850.0614+j0.19310.0598+j0.17510.0614+j0.19310.1921+j0.4970] Ω

The transformer bank is connected delta-grounded wye and the three-phase ratings are:

kVA=6000, kVLLS=12.47, kVLLL=4.16, Zpu=0.01+j0.06

The feeder serves an unbalanced three-phase wye-connected constant PQ load of:

Sa = 750 kVA at 0.85 lagging power factor

Sb = 900 kVA at 0.90 lagging power factor

Sc = 1100 kVA at 0.95 lagging power factor

Before starting the iterative solution, the forward and backward sweep matrices must be computed for each series element. The ladder method is going to be employed; therefore, only the [A], [B], and [d] matrices need to be computed.

Source line segment with shunt admittance neglected:

[U]=[100010001]

[A1]=[U]=[100010001]

[B1]=[ZeqS]=[0.1414+j0.53530.0361+j0.32250.0361+j0.27520.0361+j0.32250.1414+j0.53530.0361+j0.29550.0361+j0.27520.0361+j0.29550.1414+j0.5353]

[d1]=[U]=[100010001]

Load line segment:

[A2]=[U]=[100010001]

[B2]=[ZeqL] [0.1907+j0.50350.0607+j0.23020.0598+j0.17510.0607+j0.23020.1939+j0.48850.0614+j0.19310.0598+j0.17510.0614+j0.19310.1921+j0.4970]

[d2]=[U]=[100010001]

Transformer:

The transformer impedance must be converted to actual value in ohms referenced to the low-voltage windings.

Zbase=kVLLL2 ⋅1000kVA=2.88 Ω

Ztlow=(0.01+j0.06)⋅2.88=0.0288+j0.1728 Ω

The transformer phase impedance matrix is:

[Ztabc]=[0.0288+j0.17280000.0288+j0.17280000.0288+j0.1728] Ω

The “turns” ratio:

nt=kVLLSkVLNL=5.1958

The ladder sweep matrices are:

[At]=1nt ⋅ [10−1−1100−11] = [0.19250−0.1925−0.19250.192500−0.19250.1925]

[Bt]=[Ztabc]=[0.0288+j0.17280000.0288+j0.17280000.0288+j0.1728]

[dt]=1nt ⋅ [1−1001−1−101] = [0.1925−0.1925000.1925−0.1925−0.192500.1925]

Define the node 4 loads:

[S4] = [750/acos(0.85)___________900/acos(0.90)___________1100/acos(0.95)___________]=[750/31.79______900/25.84______1100/18.19______] = [637.5+j395.1810.0+j392.31045.0+j343.5] kVA

Define infinite bus line-to-line and line-to-neutral voltages:

[ELLs]=[12,470/30___12,470/−90____12,470/150____] V

[ELNs]=[7199.6/0__7199.6/−120_____7199.6/120____] V

The initial conditions are:

Start=[000] Tol=0.00001 VM=7199.6

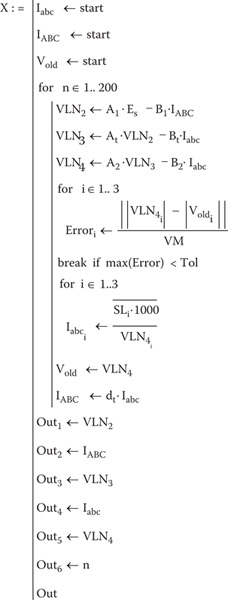

A Mathcad program is shown in Figure 10.8.

The Mathcad program is used to analyze the system, and after seven iterations, the load voltages on a 120-V base are:

[V4120]=[113.4111.5112.0] V

The voltages at node 4 are below the desired 120 V. These low voltages can be corrected with the installation of three step-voltage regulators connected in wye on the secondary bus (node 3) of the transformer. The new configuration of the feeder is shown in Figure 10.9.

FIGURE 10.8

Mathcad program.

FIGURE 10.9

Voltage regulator added to the system.

For the regulator, the potential transformer ratio will be 2400–120 V (Npt = 20), and the CT ratio is selected to carry the rated current of the transformer bank. The rated current is:

Irated=6000√3⋅2.4=832.7

The CT ratio is selected to be 1000:5 = CT = 200.

The potential transformer ratio is: Npt=VLNrated120=2400120=20

The equivalent phase impedance between nodes 3 and 4 is computed using the converged voltages at the two nodes. This is done so that the R and X settings of the compensator can be determined.

Zeqi=V3i−V4iI3i=[0.1563+j0.21840.1837+j0.28600.0919+j0.3695] Ω

The three regulators are to have the same R and X compensator settings. The average value of the computed impedances will be used.

Zavg=13⋅3∑k = 1Zeqk=0.1440+j0.2913 Ω

The value of the compensator impedance in volts is given by Equation 7.78:

R′+jX′=(0.1440+j0.2913)⋅100020=7.2+j14.6 V

The value of the compensator settings in ohms is:

Zcomp=RΩ+jXΩ=7.2+j14.65=1.44+j2.92 Ω

With the regulator in the neutral position, the voltages being input to the compensator circuit for the given conditions are:

Vregi=V3iPT=[117.5/−31.2______117.4/−151.5_______117.2/88.0_____] V

The compensator currents are:

Icompi=IabciCT=[1.6535/−63.8______2.0174/−179.1_______2.4560/64.9_____] A

With the input voltages and compensator currents, the voltages across the voltage relays in the compensator circuit are computed to be:

[Vrelay]=[Vreg]−[Zcomp]⋅[Icomp]=[113.0/−32.6______112.2/−153.5_______111.4/85.3_____] V

Notice how close these compare to the actual voltages on a 120-V base at node 4.

Assume that the voltage level has been set at 121 V with a bandwidth of 2 V. This means that the relay voltages must lie between 120 and 122 V. In order to model this system, the Mathcad routine in Figure 10.8 is slightly modified in the forward and backward sweeps. The initial matrices for the regulator are computed with the regulator taps set at zero.

Forward sweep

[VLN2]=[A1]⋅[Es]−[B1]⋅[IABC][VLN3r]=[At]⋅[VLN2]−[Bt]⋅[Iin][VLN3]=[Areg][VLN3]−[Breg]⋅[Iabc][VLN4]=[A2]⋅[VLN3]−[B2]⋅[Iabc]

Backward sweep

[Vold]=[VLN4][Iin]=[dreg]⋅[Iabc][IABC]=[dt]⋅[Iin]

After the analysis routine has converged, a new routine will compute whether or not tap changes need to be made. The Mathcad routine for computing the new taps is shown in Figure 10.10. Recall that in Chapter 7 it was shown that each tap changes the relay voltages by 0.75 V.

The computational sequence for the determination of the final tap settings and convergence of the system is shown in the flowchart in Figure 10.11.

FIGURE 10.10

Tap-changing routine.

The tap-changing routine changes individual regulators, so that the relay voltages lie within the voltage bandwidth. For this simple system, the initial change in taps becomes the final tap settings of:

[Tap]=[91011]

The final relay voltages are:

[Vrelay]=[120.3120.5120.6]

The final voltages on a 120-V base at the load center (node 4) are:

[VLN4120]=[120.6119.8121.2]

Figure 10.11

Computational sequence.

The compensator relay voltages and the actual load center voltages are very close to each other.

10.1.6 Load Allocation

Many times, the input complex power (kW and kvar) to a feeder is known because of the metering at the substation. This information can be either for the total three-phase or for each individual phase. In some cases, the metered data may be the current and power factor in each phase.

It is desirable to force the computed input complex power to the feeder to match the metered input. This can be accomplished (following a converged iterative solution) by computing the ratio of the metered input to the computed input. The phase loads can now be modified by multiplying the loads by this ratio. Because the losses of the feeder will change when the loads are changed, it is necessary to go through the ladder iterative process to determine a new computed input to the feeder. This new computed input will be closer to the metered input but most likely not within a specified tolerance. Following another ladder iteration, a ratio can be determined, and the loads modified followed. This process is repeated until the computed input is within a specified tolerance of the metered input.

Load allocation does not have to be limited to match metered readings just at the substation. The same process can be performed at any point on the feeder where metered data are available. The only difference is that now the “downstream” nodes from the metered point will be modified.

10.1.7 Loop Flow

The ladder interactive technique has proven to be a fast and efficient method for performing power-flow studies on radial distribution feeders. The shortcoming for this method is that there are cases where a feeder is not completely radial, and therefore a different method must be applied. Many times, the feeder may have just a few loops, in which case the ladder method can be modified to take into account the small looped feeder. A method called “loop flow” will be developed that will allow for loops in a predominately radial feeder [5].

10.1.7.1 Single-Phase Feeder

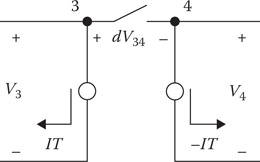

Figure 10.12 shows two small single-phase systems operating independently but with a switch between the two that once closed the two small systems become one looped system. When the switch is closed, the difference voltage (dV34) will be zero. Something has to be done to the system in order to force the difference voltage to be zero.

A way to simulate the closed switch is illustrated in Figure 10.13.

FIGURE 10.12

Single-phase system with a loop.

FIGURE 10.13

Simulation of closed switch.

To simulate the closed switch in Figure 10.13, it is necessary to determine the correct value of IT to be injected into node 3 and the negative of IT to be injected into node 4 that will force the voltage dV34 to be zero. The circuit in Figure 10.12 is modified to include the injected currents at nodes 3 and 4.

FIGURE 10.14

Modified circuit.

In Figure 10.14, the voltages at nodes 3 and 4 are given by:

V3=E1−Z12⋅(IL2+IT)−Z23⋅ITV3=E1−Z12⋅IL2−(Z12+Z23)⋅ITDefine:V3V=E1−Z12⋅IL2V3I=−(Z12+Z23)⋅ITTherefore: V3=V3V+V3I (10.9)

In a similar manner, the voltage at node 4 is computed as:

V4=E2−Z56⋅(IL5−IT)−Z45⋅(−IT)V4=E2−Z56⋅IL5+(Z56+Z45)⋅ITDefine:V4V=E2−Z56⋅IL5V4I=+(Z56+Z45)⋅ITTherefore:V4=V4V+V4I (10.10)

The voltage drop between nodes 3 and 4 consists of a component due to the source voltages and a component due to the injected currents. Using the final form of the node voltages, the difference voltage between nodes 3 and 4 is given by:

V3=V3V+V3IV4=V4V+V4IdV34=V3−V4=V3V−V4V+(V3I−V4I)dV34=dV34V+dV34I (10.11)

Applying Equations 10.9 and 10.10, the difference voltage resulting from the application of the injection currents is given by:

dV34I=V3I−V4I=−(Z12+Z23+Z56+Z45)⋅ITdV34I=−ThevZ⋅ITwhere ThevZ=Z12+Z23+Z56+Z45 (10.12)

For this simple system, ThevZ is the sum of the line impedances around the closed loop. This impedance is referred to as the Thevenin equivalent impedance. For a general system, the impedance is computed by the principle of superposition, where the voltage sources are set to zero, the loads neglected, and only the injected currents are applied to the system. For this simple system, such a circuit is shown in Figure 10.15.

Equation 10.12 applies KVL around the looped system in Figure 10.15. With the voltage drop dV34I computed, the Thevenin equivalent impedance is computed as:

ThevZ=−dV34IIT (10.13)

With ThevZ computed, the final goal is to determine the value of IT that will force the difference voltage to be zero as shown in Equation 10.14.

0=dV34V+dV34IdV34I=−dV34Vwhere: dV34I=−ThevZ⋅ITtherefore: −dV34V=−ThevZ⋅ITIT=dV34VThevZ (10.14)

FIGURE 10.15

Thevenin equivalent impedance circuit.

Because the loads on a distribution system are nonlinear, an iterative routine is used to compute the needed injection currents. Figure 10.16 shows a simple flowchart of an iterative routine used to compute the injected currents.

FIGURE 10.16

Flowchart for solution with injected currents.

It is noted in Figure 10.16 that the initial injection currents are set to zero. During the first iteration, the difference voltage will be a function of only the source voltages and the load currents. With this difference voltage computed, the first value of the injection currents is computed according to Equation 10.14 and then added to the initial value of IT=0. With the new value of injection currents, the circuit in Figure 10.14 is evaluated to compute the new difference voltage, which now includes the effect of the injection currents. The new difference voltage is checked to see whether it is within a specified tolerance of the desired zero. If it is not, an additional injection current is computed and added to the most recent value of the injection currents.

This simple single-phase circuit was used to demonstrate a method of simulating a looped system. To demonstrate how this approach is used in a larger system, the IEEE 13 Bus Test Feeder will be studied [4].

Example 10.3

Determine the values of the injected currents for the system in Figure 10.14 to simulate loop flow between the two sources.For the system, the following data are given:

E1=7200 V, E2=1.05⋅E1=7560 V

Impedance of the lines:

z1=0.5152+j1.1359 Ω/mile

Length of lines:

L12=5, L23=2, L45=3, L56=4 miles

Line impedances:

Z12=0.2576+j0.5679Z23=1.0304+j2.2718Z45=1.5456+j3.4077Z56=2.0608+j4.5436 Ω

Loads:

SL2=1500+j1250SL5=1000+j750 kW + jkvar

Step 1: Set the voltage sources to zero, and apply the positive and negative injection currents.

The base values are:

kVAbase=1000, kVLNbase=7.2Ibase=kVAbasekVLNbase=138.9

The injected current magnitude is set to the base current:

IT1=Ibase=138.9IT2=−IT1=−138.9

The analysis of the system with the two injected currents gives:

V3I=433.1/−114.4_______V4I=1212.6/65.6_____dV34I=V3I−V4I=1645.7/−114.4

The Thevenin equivalent impedance is:

Zth=−dV34IIT=1645.7/−114.4_______138.9/0__=4.8944+j10.7911

Step 2: Set the injected currents to zero and compute dV34

With the injected currents equal to zero, a Mathcad routine computes the voltages as:

V3V=7043.97/−0.6_____V4V=6734.96/−3.4____dV34V=V3V−V4V=454.86/45.2_____

With the equivalent Thevenin impedance computed, the first value of the required injected current is:

ITadd=V34VZth=38.39/−20.4______IT=IT+ITadd=0+38.39/−20.4______=38.39/−20.4______

The difference voltage is now computed with the voltage sources and injected currents. After this first iteration, the difference voltage is computed to be:

V3=6958.3/−1.3_____V4=7007.5/−1.4_____dV34=50.6/164.9_____

The added injection current and new total injected current is:

ITadd=50.6/164.9______11.85/65.60______=4.28/99.27______IT=IT+ITadd=38.39/−20.4_+4.28/99.27______=36.46/−14.52_______

The difference voltage is again computed using the new value of injected current. This process continues until after the fifth iteration when the difference voltage is:

V3=6970.42./−1.33______V4=6970.42./−1.33______dV34=V3−V4=0

The line currents flowing with injected currents are:

I23=36.8842/−14.65_______I45=36.8842/−14.65_______

Because these two currents are identical, the two systems are now operating as one system, with system 1 providing current to system 2 just as though the switch between nodes 3 and 4 was closed.

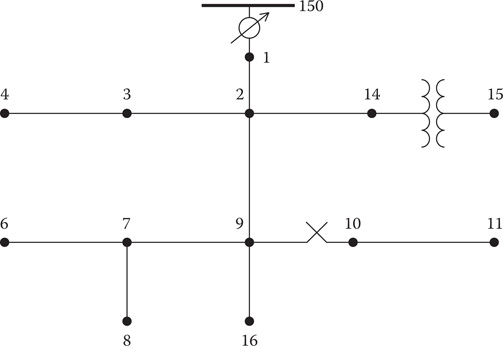

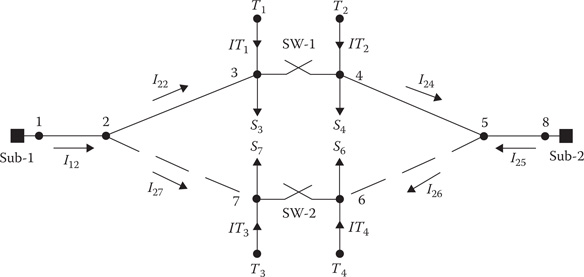

10.1.7.2 IEEE 13 Bus Test Feeder

The IEEE 13 Bus Test Feeder was developed to allow distribution analysis programs to be tested with the results compared to the published results. This feeder will be used to demonstrate the simulation of a looped system using the method presented in the previous section. A one-line diagram of the IEEE 13 Bus Test Feeder is shown in Figure 10.17 [3].

FIGURE 10.17

IEEE 13 Bus Test Feeder.

Example 10.4

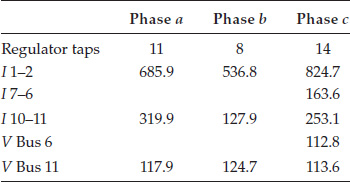

The system in Figure 10.17 was created in Windmil. With the original data, partial results are shown in Table 10.1. The currents are in amps, and the voltages are line-to-neutral on a 120-V base.

TABLE 10.1

Original Feeder Results

As seen in Table 10.1, the voltages are very unbalanced at Bus 11. This unbalance was purposely created so that distribution analysis programs could be tested for convergence in a very unbalanced feeder. No effort will be made in this text to balance the voltages. Even though the voltages are unbalanced, they are still within the ANSI standard [5] of all voltages being between 114 and 126 V.

Rather than balance the voltages, two new loads are going to be added to the existing feeder, which will lead to the need for the looped feeder. The following loads are added to the system:

Bus 6: Phase c: 200+ j100kW+ jkvar

Bus 11: Three-phase load: 750+ j525 kW + jkvar

With the new loads and the voltage regulator operating, the partial results are shown in Table 10.2.

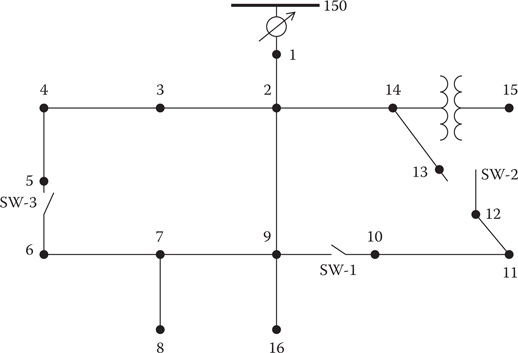

The voltage at Bus 6 has gone below the ANSI minimum of 114 V. The voltage at Bus 11 Phase c is also below the ANSI standard. The actual problem with Bus 11 is that the current capacity of 260 A on the underground concentric neutral cable between Bus 10 and Bus 11 is exceeded. In order to solve these problems and to demonstrate the looped feeder simulation, two new lines will be added to the system. The one-line diagram of the modified IEEE 13 feeder is shown in Figure 10.18.

TABLE 10.2

New Loads Added

FIGURE 10.18

Modified IEEE 13 Bus Test Feeder.

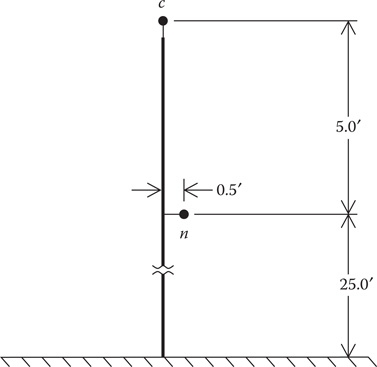

The new line from Bus 4 to Bus 5 consists of 1/0 ACSR 6/1 constructed on a single pole as shown in Figure 10.19. The length of the line is 600ft.

The three-phase line from Bus 14 to Bus 13 consists of 4/0 ACSR 6/1 phase and neutral conductors with a pole configuration as shown in Figure 10.20. The length of the line is 800 ft.

In order to simulate the loop flow, currents must be injected into Buses 5, 6, 13, and 11 as shown in Figure 10.21.

The line from Bus 2 to bus 9 has a distributed load, which is modeled as two-thirds of the distributed load at Bus 2a, which is one-third the length of the line, and the remaining distributed load is connected at the end of the line at the new Bus 9a. In Figure 10.21, SW-1 is a three-phase switch that can only be modeled as open or closed. SW-2 is a three-phase switch that can be modeled as open, closed, or looped. SW-3 is a single-phase switch on phase c and can only be modeled as open or looped.

FIGURE 10.19

Single-phase line.

FIGURE 10.20

Three-phase line.

FIGURE 10.21

Injected currents.

The first step in simulating loop flow is to compute the Thevenin equivalent impedance at each looped switch for each phase. The currents injected into Bus 13 (IT1) will be in phases a, b, and c. The injected currents at Bus 11 (IT3) will be the negative of IT1. Switch SW-3 is a single-phase switch on Phase c. Therefore, the injected current at Bus 5 (IT2) will only be a Phase c current. The injected current at Bus 6 (IT4) will be the negative of IT2. There will be a Thevenin equivalent impedance computed at each switch for each phase injected at each of the injection nodes. This will lead to a 4 × 4 Thevenin equivalent matrix (ThevZ). For this process, the value of the injected current is assumed to be the base current of the system 694.4 A.

For the computation of ThevZ, the source voltages and all loads are set to zero. Refer to Figure 10.21 with SW-1 closed. The line-to-neutral voltages at Buses 13, 11, 5, and 6 are computed with only the Phase a currents being injected at Buses 13 and 12. A Mathcad program is used to compute the voltages. With only the Phase a currents, the vectors for the injected currents at the switch buses are:

[IT1]=[694.400] [IT3]=[−694.400] (10.15)

The bus voltages with just the Phase a-injected current at Bus 13 are computed to be:

[V13]=[239.5/−122.5_______77.3/−110.5_______89.8/−107.3______] [V12]=[330.0/64.2_____147.8/65.2_____125.9/61.4_____][V5c]=0 [V6c]=118.9/−110.5_______ (10.16)

The difference voltages are:

[dV1312]=[568.6/−118.6______224.9/−113.3______214.7/−113.9______]dV56c=118.93/−110.5_______ (10.17)

Equation 10.17 is used to compute the first column elements of the ThevZ matrix.

[ThevZ1,1ThevZ2,1ThevZ3,1]=−1IT⋅[dV1312adV1312bdV1312c]=[0.3921+j0.71870.1282+j0.29740.1252+j0.2826]Thevz4,1=−dV56cIT=0.0598+j0.1605 Ω (10.18)

This process is repeated with the injected currents in Phase b at Buses 13 and 12, followed by the injected currents in Phase c at Buses 13 and 12. The last step is to have the Phase c currents injected at Buses 5 and 6. The final ThevZ matrix in ohms is:

[ThevZ]=[0.3921+j0.71780.1282+j0.29740.1252+j0.28260.0598+j0.16050.1282+j0.29740.3866+j0.73020.1262+j0.24370.0581+j0.14580.1252+j0.28260.1262+j0.24370.3880+j0.73240.1293+j0.39200.0598+j0.16050.0581+j0.14580.1293+j0.39200.6328+j0.9023] (10.19)

With TheZ computed, the values of the needed injection currents must be determined with the loads and capacitors included. The method is to apply Equation 10.18 in matrix form for the IEEE 13 bus feeder and solve for the [IT] array. The equation is:

[IT1aIT1bIT1cIT2c] = [ThevZ]−1 ⋅ [dV1311adV1311bdV1311cdV56c] (10.20)

In order to determine the injection currents, the power-flow program must be run where all of the loads and capacitor along with the injection currents are modeled. The tap settings for the regulator are set at the same taps as in Table 10.2. As was done with the single-phase system, initially all of the injection currents are set to zero, and the difference voltages in Equation 10.20 are computed. Equation 10.20 is used to compute the initial change in injection currents. The computed difference voltages for this first iteration are:

[dV1312adV1312bdV1312cdV56c]=[181.2/50.8_____39.4/−17.4_____206.2/151.8______228.7/153.6______] V (10.21)

With the difference voltages computed, Equation 10.20 is used to compute the injection currents that will force the difference voltages to zero. During the first iteration, the injection currents were set to zero. Applying Equation 10.14 will give the “added” injection currents needed. After the first iteration, the computed injection currents are:

[IT1aIT1bIT1cIT2c]=[304.6/−22.0______145.5/−122.4_______261.7/102.8______147.4/99.0_____] A (10.22)

With the currents in Equation 10.22 injected into the buses, the power-flow program is run again. Because the current flows on the lines will now be different, the bus voltages will also change. Because many of the loads are modeled as constant PQ, those load currents are subject to change. The second iteration is necessary to recalculate the bus voltages and determine whether additional injection currents are needed. After the second iteration, the difference voltages across the looped switches are:

[dV1311adV1311bdV1311cdV56c]=[8.2/−165.1_______4.4/−108.2_______17.1/−76.8______18.1/−76.3______] V (10.23)

Because the difference voltages are not close to zero, additional injection currents are needed. The additional currents are:

[ITadd]=[15.1/97.9_____1.2/−8.5_____18.6/−129.3_______11.0/−132.5_______] A (10.24)

The total injection currents for the next iteration are:

[IT1aIT1bIT1cIT2]=[304.6/−22.0_____145.5/−122.4_______261.7/102.8______147.4/99.0_____]+[15.1/97.9_____1.2/−8.5____18.6/−129.3_____11.0/−132.5_______]=[297.4/−19.4______145.0/−122.0_______250.7/106.2______140.8/102.5______] (10.25)

Following this procedure, after the fourth iteration, the difference voltages are very small, and the process stops. The injected currents and difference voltages are:

[IT1aIT1bIT1cIT2c]=[298.0/−19.5______145.0/−121.9_______251.7/106.0______141.4/102.4______] A[dV1311adV1311bdV1311cdV56c]=[0.0276/−121.2_______0.0343/−93.9.6________0.0931/−62.4______0.0963/−62.2______] V (10.26)

In Table 10.2, it was shown that when the new loads were added at Buses 6 and 11, the bus voltage at Bus 6 was below the ANSI standard. Moreover, the concentric neutral line was overloaded. By adding the looped switches, Table 10.3 shows the results.

TABLE 10.3

Looped Switches

A comparison of Tables 10.2 and 10.3 shows the following:

-

The voltage at Bus 6 is now above the minimum ANSI standard of 114 V.

-

The current flowing in the concentric neutral cable from Bus 10 to Bus 11 is much lower than the cable current rating.

-

The voltages at Bus 11 are not as unbalanced and are somewhat higher.

-

The current out of the substation is basically the same, since the net injection currents are zero; so the slight change in this current is because of the change in load currents for the constant PQ loads.

-

The regulator tap positions have not changed, since the current into the line drop compensator is basically the same as that before the looped switches were closed.

10.1.7.3 Summary of Loop Flow

A method of simulating a looped distribution system has been presented. The loop is simulated by the installation of a switch between two existing buses in the feeder. To simulate the loop flow, the voltage at buses on the two sides of the switch must be equal. This is accomplished by the injection of a positive current at one of the buses and a negative value on the other bus. A method of calculating the necessary injection currents to force the difference voltage across the loop switch to be zero has been presented. Initially, a simple single-phase system was used to develop the technique. Following that, the IEEE 13 Bus Test Feeder was used to demonstrate the closing of a three-phase loop switch and a single-phase loop switch.

10.1.8 Summary of Power-Flow Studies

This section has developed a method for performing power-flow studies on a distribution feeder. Models for the various components of the feeder have been developed in previous chapters. The purpose of this section has been to develop and demonstrate the modified ladder iterative technique using the forward and backward sweep matrices for the series elements. It should be obvious that a study of a large feeder with many laterals and sublaterals cannot be performed without the aid of a complex computer program. In addition to the ladder iterative technique, a method of modeling a feeder with closed loops was presented under the name “loop flow.”

The development of the models and examples in this text use actual values of voltage, current, impedance, and complex power. When per-unit values are used, it is imperative that all values be converted to per-unit using a common set of base values. In the usual application of per-unit, there will be a base line-to-line voltage and a base line-to-neutral voltage; in addition, there will be a base line current and a base delta current. For both the voltage and current, there is a square root of three relationships between the two base values. In all of the derivations of the models, and in particular those for the three-phase transformers, the square root of three has been used to relate the difference in magnitudes between line-to-line and line-to-neutral voltages and between the line and delta currents. Because of this, when using the per-unit system, there should be only one base voltage, and that should be the base line-to-neutral voltage. When this is done, for example, the per-unit positive and negative sequence voltages will be the square root of three times the per-unit positive and negative sequence line-to-neutral voltages. Similarly, the positive and negative sequence per-unit line currents will be the square of three times the positive and negative sequence per-unit delta currents. By using just one base voltage and one base current, the per-unit generalized matrices for all system models can be determined.

10.2 Short-Circuit Studies

The computation of short-circuit currents for unbalanced faults in a normally balanced three-phase system has traditionally been accomplished by the application of symmetrical components. However, this method is not well suited to a distribution feeder that is inherently unbalanced. The unequal mutual coupling between phases leads to mutual coupling between sequence networks. When this happens, there is no advantage of using symmetrical components. Another reason for not using symmetrical components is that the phases between which faults occur are limited. For example, using symmetrical components line-to-ground faults are limited to phase a to the ground. What happens if a single-phase lateral is connected to Phase b or c and the short-circuit current is needed? This section will develop a method for short-circuit analysis of an unbalanced three-phase distribution feeder using the phase frame [4].

10.2.1 General Short-Circuit Theory

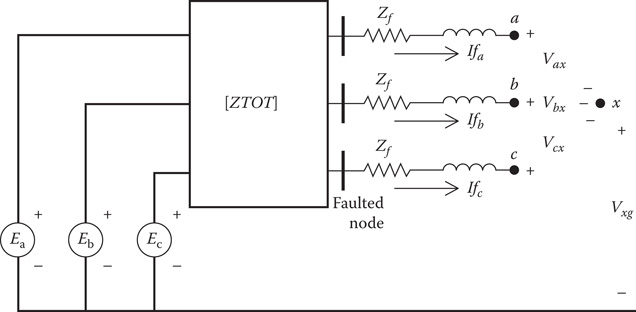

Figure 10.22 shows the unbalanced feeder as modeled for short-circuit calculations.

Short circuits can occur at any one of the five points shown in Figure 10.22. Point 1 is the high-voltage bus of the distribution substation transformer. The values of the short-circuit currents at point 1 are normally determined from a transmission system short-circuit study. The results of these studies are supplied in terms of the three-phase and single-phase short-circuit Mega-Volt-Amperes (MVAs). Using the short-circuit MVAs, the positive and zero sequence impedances of the equivalent system can be determined. These values are needed for the short-circuit studies at the other four points in Figure 10.22.

FIGURE 10.22

Unbalanced feeder short-circuit analysis model.

Given the three-phase short-circuit MVA magnitude and angle, the positive sequence equivalent system impedance in ohms is determined by:

Z+=kVLL2(MVA3-phase)* Ω (10.27)

Given the single-phase short-circuit MVA magnitude and angle, the zero sequence equivalent system impedance in ohms is determined by:

Z0=3⋅kVLL2(MVA1-phase)*−2.Z+ Ω (10.28)

In Equations 10.27 and 10.28, kVLL is the nominal line-to-line voltage in kV of the transmission system.

The computed positive and zero sequence impedances need to be converted into the phase impedance matrix using the symmetrical component transformation matrix defined in Equation 4.63 in Chapter 4.

[Z012]=[Z0000Z1000Z1][Zabc]=[As]⋅[Z012]⋅[As]−1 (10.29)

For short circuits at points 2, 3, 4, and 5, it is necessary to compute the Thevenin equivalent three-phase circuit at the short-circuit point. The Thevenin equivalent voltages will be the nominal line-to-ground voltages with the appropriate angles. For example, assume the equivalent system line-to-ground voltages are balanced three-phase of nominal voltages with the Phase a voltage at zero degrees. The Thevenin equivalent voltages at points 2 and 3 will be computed by multiplying the system voltages by the generalized transformer matrix [At] of the substation transformer. Carrying this further, the Thevenin equivalent voltages at points 4 and 5 will be the voltages at node 3 multiplied by the generalized matrix [At] for the in-line transformer.

The Thevenin equivalent phase impedance matrices will be the sum of the Thevenin phase impedance matrices of each device between the system voltage source and the point of fault. Step-voltage regulators are assumed to be set in the neutral position, so that they do not enter into the short-circuit calculations. Anytime that a three-phase transformer is encountered, the total phase impedance matrix on the primary side of the transformer must be referred to the secondary side using Equation 8.160.

Figure 10.23 illustrates the Thevenin equivalent circuit at the faulted node [3].

In Figure 10.23, the voltage sources Ea, Eb, and Ec represent the Thevenin equivalent line-to-ground voltages at the faulted node. The matrix [ZTOT] represents the Thevenin equivalent phase impedance matrix at the faulted node. The fault impedance is represented by Zf in Figure 10.23.

KVL in matrix form can be applied to the circuit in Figure 10.23.

[EaEbEc]=[ZaaZabZacZbaZbbZbcZcaZcbZcc]⋅[IfaIfbIfc]+[Zf000Zf000Zf]⋅[IfaIfbIfc]+[VaxVbxVcx]+[VxgVxgVxg] (10.30)

Equation 10.30 can be written in compressed form as:

[Eabc]=[ZTOT]⋅[Ifabc]+[ZF]⋅[Ifabc]+[Vabcx]+[Vxg] (10.31)

Combine terms in Equation 10.31.

[Eabc]=[ZEQ]⋅[Ifabc]+[Vabcx]+[Vxg] (10.32)

where

[ZEQ]=[ZTOT]+[ZF] (10.33)

Solve Equation 10.15 for the fault currents:

[Ifabc]=[Y]⋅[Eabc]−[Y]⋅[Vabcx]−[Y]⋅[Vxg] (10.34)

where

[Y]=[ZEQ]−1 (10.35)

FIGURE 10.23

Thevenin equivalent circuit.

Since the matrices [Y] and [Eabc] are known, define:

[IPabc]=[Y]⋅[Eabc] (10.36)

Substituting Equation 10.19 into Equation 10.17 and rearranging results in:

[IPabc]=[Ifabc]+[Y]⋅[Vabcx]+[Y]⋅[Vxg] (10.37)

Expanding Equation 10.37:

[IPaIPbIPc] = [IfaIfbIfc]+[YaaYabYacYbaYbbYbcYcaYcbYcc]⋅[VaxVbxVcx] +[YaaYabYacYbaYbbYbcYcaYcbYcc]⋅[VxgVxgVxg] (10.38)

Performing the matrix operations in Equation 10.38:

IPa=Ifa+(Yaa⋅Vax+Yab⋅Vbx+Yac⋅Vcx)+Ysa⋅VxgIPb=Ifb+(Yba⋅Vax+Ybb⋅Vbx+Ybc⋅Vcx)+Ysb⋅VxgIPc=Ifa+(Yca⋅Vax+Ycb⋅Vbx+Ycc⋅Vcx)+Ysc⋅Vxg (10.39)

where

Ysa=Yaa+Yab+YacYsb=Yba+Ybb+YbcYsc=Yca+Ycb+Yccor: Ysi=3∑k=1Yi,k (10.40)

Equations 10.39 become the general equations that are used to simulate all types of short circuits. Basically, there are three equations and seven unknowns (Ifa, Ifb, Ifc, Vax, Vbx, Vcx, and Vxg). The other three variables in the equations (IPa, IPb, and IPc) are functions of the total impedance and the Thevenin voltages and are therefore known. In order to solve Equations 10.22, it will be necessary to specify four additional independent equations. These equations are functions of the type of fault being simulated. The additional four equations required for various types of faults are given below. These values are determined by placing short circuits in Figure 10.13 to simulate the particular type of fault. For example, a three-phase fault is simulated by placing a short circuit from node a to x, node b to x, and node c to x. That gives three voltage equations. The fourth equation comes from applying KCL at node x, which gives the sum of the fault currents to be zero.

10.2.2 Specific Short Circuits

Three-Phase Faults

Vax=Vbx=Vcx=0Ia+Ib+Ic=0 (10.41)

Three-phase-to-ground Faults

Vax=Vbx=Vcx=Vxg=0 (10.42)

Line-to-line Faults (assume i–j fault with phase k unfaulted)

Vix=Vjx=0Ifk=0Ifi+Ifj=0 (10.43)

Line-to-line-to-ground Faults (assume i–j–g fault with phase k unfaulted)

Vix=Vjx=0Vxg=0Ik=0 (10.44)

Line-to-ground Faults (assume phase k fault with phases i and j unfaulted)

Vkx=Vxg=0Ifi=Ifj=0 (10.45)

Notice that Equations 10.43, 10.44, and 10.45 will allow the simulation of line-to-line faults, line-to-line-to-ground, and line-to-ground faults for all phases. There is no limitation to b–c faults for line-to-line and a–g for line-to-ground as is the case when the method of symmetrical components is employed.

A good way to solve the seven equations is to set them up in matrix form.

[IPaIPbIPc0000] = [100Y1,1Y1,2Y1,3Ys1010Y2,1Y2,2Y2,3Ys2001Y3,1Y3,2Y3,3Ys3____________________________] ⋅ [IfaIfbIfcVaxVbxVcxVxg] (10.46)

Equation 10.29 in condensed form:

[IPs]=[C]⋅[X] (10.47)

Equation 10.47 can be solved for the unknowns in matrix [X]:

[X]=[C]−1⋅[IPs] (10.48)

The blanks in the last four rows of the coefficient matrix in Equation 10.46 are filled in with the known variables depending upon what type of fault is to be simulated. For example, the elements in the [C] matrix simulating a three-phase fault would be:

C4,4=C5,5=C6,6=1C7,1=C7,2=C7,3=1

All of the other elements in the last four rows will be set to zero.

Example 10.5

Use the system in Example 10.2, and compute the short-circuit currents for a bolted (Zf = 0) line-to-line fault between Phases a and b at node 4.

The infinite bus balanced line-to-line voltages are 12.47 kV, which leads to balanced line-to-neutral voltages at 7.2 kV.

[ELLs]=[12,470/30___12,470/−90____12,470/150____] V

[ELNs]=[W]⋅[ELLs][7199.6/0__7199.6/−120_____7199.6/120____] V

The line-to-neutral Thevenin circuit voltages at node 4 are determined using Equation 8.165.

[Eth4]=[At]⋅[ELNs]=[2400/−30____2400/−150_____2400/150____] V

The Thevenin equivalent impedance at the secondary terminals (node 3) of the transformer consists of the primary line impedances referred across the transformer plus the transformer impedances. Using Equation 8.165:

[Zth3]=[At]⋅[ZeqSABC]⋅[dt]+[Ztabc]

[Zth3]=[0.0366+j0.1921−0.0039−j0.0086−0.0039−j0.0106−0.0039−j0.00860.0366+j0.1886−0.0039−j0.0071−0.0039−j0.0106−0.0039−j0.00710.0366+j0.1906] Ω

Note that the Thevenin impedance matrix is not symmetrical. This is a result, once again, of the unequal mutual coupling between the phases of the primary line segment.

The total Thevenin impedance at node 4 is:

[Zth4]=[ZTOT]=[Zth3]+[ZeqLabc]

[ZTOT]=[0.2273+j0.69550.0568+j0.22160.0559+j0.16450.0568+j0.22160.2305+j0.67710.0575+j0.18600.0559+j0.16450.0575+j0.18600.2287+j0.6876] Ω

The equivalent admittance matrix at node 4 is:

[Yeq4]=[ZTOT]−1

[Yeq4]=[0.5031−j1.4771−0.1763+j0.3907−0.0688+j0.2510−0.1763+j0.39070.5501−j1.5280−0.1148+j0.3133−0.0688+j0.2510−0.1148+j0.31330.4843−j1.4532] S

Using Equation 10.36, the equivalent injected currents at the point of fault are:

[IP]=[Yeq4]⋅[Eth4]=[4466.8/−96.3______4878.9/138.0______4440.9/16.4_____] A

The sums of each row of the equivalent admittance matrix are computed according to Equation 10.40.

Ysi=3∑k=1Yeqi,k= [0.2580−j0.83540.2590−j0.82400.3008−j0.8889] S

For the a–b fault at node 4, according to Equation 10.43:

Vax=0Vbx=0Ifc=0Ifa+Ifb=0

The coefficient matrix [C] using Equation 10.46:

[C]=[1000.5031−j1.4771−0.1763+j0.3907−0.0688+0.25100.2580−j.8354010−0.1763+j.39070.5501−j1.5280−0.1148+j.31330.2590−j.8240001−0.0688+j.2510−0.1148+j.31330.4843−j1.45320.3008−j.88900001000000010000100001100000]

The injected current matrix is:

[IPs]=[4466.8/−96.3______4878.9/138.0______4440.9/16.4_____0000]

The unknowns are computed by:

[X] = [C]−1⋅ [IPs]=[4193.7/−69.7______4193.7/110.3______0003646.7/88.1_____1220.2/−91.6______]

The interpretation of the results are:

Ifa=X1=4193.7/−69.7______Ifb=X2=4193.7/110.3______Ifc=X3=0Vax=X4=0Vbx=X5=0Vcx=X6=3646.7/88.1_____Vxg=X7=1220.2/−91.6_____

Using the line-to-ground voltages at node 4 and the short-circuit currents and working back to the source using the generalized matrices will check the validity of these results.

The line-to-ground voltages at node 4 are:

[VLG4]=[Vax+VxgVbx+VxgVcx+Vxg]=[1220.2/−91.6______1220.2/−91.6______2426.5/88.0_____] V

The short-circuit currents in matrix form are:

[I4]=[I3]=[4193.7/−69.7______4193.7/110.3______0] A

The line-to-ground voltages at node 3 are:

[VLG3]=[a2]⋅[VLG4] + [b1]⋅[I4] =[1814.0/−47.3_________1642.1/−139.2_________2405.1/89.7_________] V

The equivalent line-to-neutral voltages and line currents at the primary terminals (node 2) of the transformer are:

[VLN2]=[at]⋅[VLG3]+[bt]⋅[I3]=[6784.3/0.2____7138.8/−118.7______7080.6/118.3______] V

[I2]=[dt]⋅[I3]=[1614.3/−69.7______807.1/110.3______807.1/110.3______] A

Finally, the equivalent line-to-neutral voltages at the infinite bus can be computed.

[VLN1]=[a1]⋅[VLN2] + [b1]⋅[I2]=[7201.2/0__7198.2/−120_____7199.3/120____] V

The source line-to-line voltages are:

[VLL1]=[Dv]⋅[VLN1]=[12,470/30_____12,470/−90____12,470/150____]

These are the same line-to-line voltages that were used to start the short-circuit analysis.

10.2.3 Backfeed Ground Fault Currents

The wye–delta transformer bank is the most common transformer connection used to serve three-phase loads or a combination of a single-phase lighting load and a three-phase load. With this connection, a decision has to be made as to whether or not to ground the neutral of the primary wye connection. The neutral can be directly connected to the ground or grounded through a resistor or left floating (ungrounded wye–delta). When the neutral is grounded, the transformer bank becomes a grounding bank that provides a path for zero sequence fault currents. In particular, the grounded connection will provide a path for a line-to-ground fault current (backfeed current) for a fault upstream from the transformer bank. A method for the analysis of the upstream fault currents will be presented [6].

10.2.3.1 One Downstream Transformer Bank

A simple system consisting of one downstream grounded wye–delta transformer bank is shown in Figure 10.24.

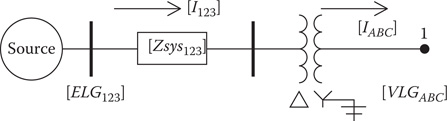

In Figure 10.24, the substation transformer is connected to a high-voltage equivalent source consisting of a three-phase voltage source and an equivalent impedance matrix. The equivalent source and substation transformer bank combination can be represented as shown in Figure 10.25.

In Chapter 8, it was shown that the combination of the equivalent source and substation transformer could be reduced to a Thevenin equivalent circuit as shown in Figure 10.26.

FIGURE 10.24

Simple system.

FIGURE 10.25

Equivalent source and substation transformer.

FIGURE 10.26

Thevenin equivalent circuit.

The Thevenin equivalent voltages and impedance matrix are given by:

[Eth]=[At]⋅[ELG123][ZthABC]=[A t]⋅[Zsys123]⋅[dt]+[Bt]where for the delta-grounded wye transformer:nt=kVLLprimarykVLNsecondary[At]=1nt⋅[10−1−1100−11][Bt]=[Zta000Ztb000Ztc][dt]=1nt⋅[1−1001−1−101][Zsys123]=[Zl1,1Zl1,2Zl1,3Zl2,1Zl2,2Zl2,3Zl3,1Zl3,2Zl3,3] (10.49)

Applying the Thevenin equivalent circuit, Figure 10.24 is modified to that of Figure 10.27.

In Figure 10.27, the equivalent impedance matrix is:

[Zeq]=[ZthABC] + [Z12ABC] (10.50)

A question that comes up when a wye–delta transformer bank is to be installed is whether the neutral should be grounded. If the neutral is to be grounded, it can either be a direct ground or be grounded through a resistance. The other option is to just leave the neutral floating. Figure 10.28 shows the three-phase circuit for the modified simple system in Figure 10.27 when a line-to-ground fault has occurred at node 2 in Figure 10.27. Note the question mark on grounding of the neutral.

FIGURE 10.27

Modified simple system.

FIGURE 10.28

Three-phase circuit with floating transformer neutral.

For future reference, the source voltages are [EsABC]=[Eth]. When the neutral is left floating in Figure 10.28, there is no path for the currents to flow from the transformer back to the fault. In this case, the only short-circuit current will be from the substation to the faulted node.

Figure 10.29 represents the transformer bank grounded neutral through a resistance.

FIGURE 10.29

Three-phase circuit with grounded transformer neutral.

Before getting into the derivation of the computation of the short-circuit currents in Figure 10.29, it is important to do a visual analysis of the circuit. The most important observation is that there is a path for the current ItA to flow from the phase A transformer through the fault and back to the neutral through the grounding resistance (Zg). Note that this resistance can be set to zero for the direct grounding of the neutral. Because ItA flows, there must be a current in the delta transformer secondary. This current is given by:

Iab=nt⋅ItA (10.51)

Because the line currents out of the delta are zero, then all of the currents flowing in the delta must be equal.

Iab=Ibc=Ica=nt⋅ItA (10.52)

Because the delta currents are equal, define the currents out of the transformer:

ItA=ItB=ItC=It (10.53)

The sum of the line-to-line secondary voltages must add to zero:

Vab+Vbc+Vca=0 (10.54)

10.2.3.2 Complete Three-Phase Circuit Analysis

A method to calculate the short-circuit currents is to apply basic circuit and transformer analysis to determine all voltages and currents. A three-phase circuit showing an A–G fault at node 2 is shown in Figure 10.29. There are 28 unknowns, which will require 28 independent equations. Without going into detail, the 28 equations are:

-

13 KVL

-

6 basic transformer primary/secondary

-

5 KCL

-

4 unique to type of fault

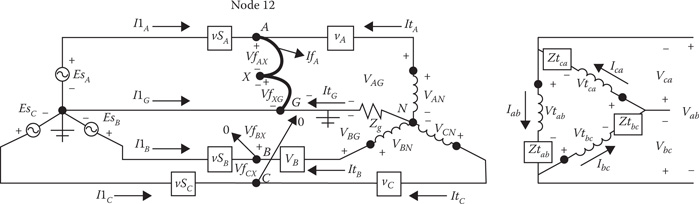

The 28 independent equations will be reduced to 8 independent equations that will compute the voltages and currents in the fault and the backfeed current from the transformer bank. All other system voltages and currents can be computed by knowing these eight variables.

In Figure 10.30, a node X has been installed to represent the fault at node 2. With the node X, there are four voltages defined as VfAX, VfBX, VfCX, VfXG and three fault currents defined as IfA, IfB, IfC. The different types of faults are modeled by setting the appropriate voltages and currents to zero. For example, for an A–G fault, the following conditions are set:

FIGURE 10.30

Three-phase circuit with AG fault.

VfAX=0VfXG=0IfB=0IfC=0 (10.55)

In Figure 10.30, three loop equations can be written between the source and the faulted node.

EsA=VfAX+VfXG+Zeq1,1⋅I1A+Zeq1,2⋅I1B+Zeq1,3⋅I1CEsB=VfBX+VfXG+Zeq2,1⋅I1A+Zeq2,2⋅I1B+Zeq2,3⋅I1CEsC=VfCX+VfXG+Zeq3,1⋅I1A+Zeq3,2⋅I1B+Zeq3,3⋅I1C (10.56)

KCL can be applied at the faulted node point:

I1A=IfA−ItI1B=IfB−ItI1C=IfC−It (10.57)

Substitute Equation 10.57 into Equation 10.56:

EsA=VfAX+VfXG+Zeq1,1⋅IfA+Zeq1,2⋅IfB+Zeq1,3⋅IfC−Zx1⋅ItEsB=VfBX+VfXG+Zeq2,1⋅IfA+Zeq2,2⋅IfB+Zeq2,3⋅IfC−Zx2⋅ItEsC=VfCX+VfXG+Zeq3,1⋅IfA+Zeq3,2⋅IfB+Zeq3,3⋅IfC−Zx3⋅Itwhere for i = 1, 2, 3: Zxi=3∑k=1Zeqi,k (10.58)

The line-to-ground voltages at the transformer primary terminals are:

VAG=VfAX+VfXG+(Z2311+Z2312+Z2313)⋅ItVBG=VfBX+VfXG+(Z2321+Z2322+Z2323)⋅ItVCG=VfCX+VfXG+(Z2331+Z2332+Z2333)⋅It

VAG=VfAX+VfXG+Zy1⋅ItVBG=VfBX+VfXG+Zy2⋅ItVCG=VfCX+VfXG+Zy2⋅It (10.59)

The line-to-neutral ideal transformer voltages are:

VAN=VAG+3⋅Zg⋅ItVAN=VBG+3⋅Zg⋅ItVAN=VCG+3⋅Zg⋅It (10.60)

Substitute Equation 10.59 into Equation 10.60:

VAN=VAG+3⋅Zg⋅It=VfAX+VfXG+(Zy1 +3⋅Zg)⋅ItVBN=VBG+3⋅Zg⋅It=VfBX+VfXG+(Zy2 +3⋅Zg)⋅ItVCN=VCG+3⋅Zg⋅It=VfCX+VfXG+(Zy3 +3⋅Zg)⋅It (10.61)

From the currents flowing in the delta secondary are:

Iab=Ibc=Ica=nt⋅ItAIab=Ibc=Ica=nt⋅Itsince: ItA=It (10.62)

The line-to-line secondary voltages are:

Vab=Vtab+Ztab⋅IabVbc=Vtbc+Ztbc⋅IbcVca=Vtca+Ztca⋅Ica (10.63)

In Equation 10.63:

Vtab=1nt⋅VANVtbc=1nt⋅VBNVtca=1nt⋅VCNIab=Ibc=Ica=nt⋅It (10.64)

Substitute Equation 10.64 into Equation 10.63:

Vab=1nt⋅VAN+Ztab⋅nt⋅ItVbc=1nt⋅VBN+Ztbc⋅nt⋅ItVca=1nt⋅VCN+Ztca⋅nt⋅Itbut: Vab+Vbc+Vca=0therefore: 0=1nt⋅(VAN+VBN+VCN)+nt⋅Ztsum⋅Itwhere Ztsum=Ztab+Ztbc+Ztca (10.65)

Substitute Equation 10.61 into Equation 10.65:

0=1nt⋅(VAN+VBN+VCN)+nt⋅Ztsum⋅ItVAN=VfAX+VfXG+(Zy1 +3⋅Zg)⋅ItVBN=VfBX+VfXG+(Zy2 +3⋅Zg)⋅ItVCN=VfCX+VfXG+(Zy3 +3⋅Zg)⋅It0=1nt⋅((VfAX+VfBX+VfCX+3⋅VfXG)+Zysum+9⋅Zg)⋅It+nt⋅Ztsum⋅It0=1nt⋅(VfAX+VfBX+VfCX+3⋅VfXG)+1nt⋅(Zysum+nt2⋅Ztsum+9⋅Zg)⋅It0=1nt⋅(VfAX+VfBX+VfCX+3⋅VfXG)+Ztotal⋅It (10.66)

where

Ztotal=1nt⋅(Zysum+nt2⋅Ztsum+9⋅Zg)

Combining Equations 10.58 and 10.66 gives four equations with eight unknowns:

EsA=VfAX+VfXG+Zeq1,1⋅IfA+Zeq1,2⋅IfB+Zeq1,3⋅IfC−Zx1⋅ItEsB=VfBX+VfXG+Zeq2,1⋅IfA+Zeq2,2⋅IfB+Zeq2,3⋅IfC−Zx2⋅ItEsC=VfCX+VfXG+Zeq3,1⋅IfA+Zeq3,2⋅IfB+Zeq3,3⋅IfC−Zx3⋅It0=1nt⋅(VfAX+VfBX+VfCX+3⋅VfXG)+Ztotal⋅It (10.67)

where

Ztotal=1nt⋅(Zysum+Ztsum+9⋅Zg)Zysum=Zy1+Zy2+Zy3Ztsum=Ztab+Ztbc+Ztca

Equation 10.67 gives four independent equations. The final four independent equations are unique for the type of fault to be modeled. The four equations that model each of the various types of faults are defined in Equations 10.41 to 10.45.

A general matrix equation for modeling a B–C–G fault is shown in the forthcoming. The first four rows in the coefficient matrix [C] come from Equation 10.69, and the last four rows are for the B–C–G fault as specified in Section 10.2.2.

[EsAEsBEsC00000] = [Zeq1,1Zeq1,2Zeq1,3−Zx11001Zeq2,1Zeq2,2Zeq2,3−Zx20101Zeq3,1Zeq3,2Zeq3,3−Zx30011000Ztotal1nt1nt1nt3nt10000000000001000000001000000001] ⋅ [IfAIfBIfCItVfAXVfBXVfCXVfXG][Ex]=[C]⋅[X] (10.68)

Example 10.6

The system in Figure 10.29 is to be analyzed for a B–C–G fault at node 2. The given information for the system is as follows:

Equivalent system:

[ELLsys]=[230,000/60___230,000/−60____230,000/180____] [ELNsys]=[W]⋅[ELLsys]=[132,790.6/30___132,790.6/−90____132,790.6/150____] V

Line length = 200 miles[Zsys123]=[88.1693+j226.958125.6647+j90.926025.6647+j71.397125.6647+j90.926087.7213+j235.691424.5213+j78.284725.6647+j71.397124.5213+j78.284785.7213+j235.6814] Ω

Substation transformer:

kVA=2500 kVLLpri=230 kVLLsec=12.47 Zsub=0.005+j0.06 per-unitZbasesec=kVLLsec2 ⋅1000kVA=62.2004Zt=Ztsub⋅Zbasesec=0.311+j3.732[ZsubABC]=[0.311+j3.7320000.311+j3.7320000.311+j3.732]

Compute substation transformer matrices:

kVLNsec=kVLLsec√3=7.1996nt=kVLLprikVLNsec=31.9464[At]=1nt ⋅ [10−1−1100−11][Bt]=[ZsubABC][dt]=1nt ⋅ [1−1001−1−101]

Compute substation transformer Thevenin equivalent circuit relative to secondary (Chapter 8, Section 8.12):

[Eth]=[At]⋅[ELNsys]=[7199.5579/0_7199.5579/−120_7199.5579/120_][ZthABC]=[At]⋅[Zsys123]⋅[dt]+[Bt][ZthABC]=[0.4311+j4.40454−0.0601−j0.1400−0.0600−j0.1734−0.0601−j0.14000.4311+j4.0071−0.0600−j0.1351−0.0600−j0.1734−0.0600−j0.13510.4309+j4.0405]

Given distribution line impedance matrices as follows:

[Z12ABC]=[0.9151+j2.15610.3119+j1.00330.3070+j0.76990.3119+j1.00330.9333+j2.09630.3160+j0.84730.3070+j0.76990.3160+j0.84730.9229+j2.1301][Z23ABC]=[0.4576+j1.07800.1559+j0.50170.1535+j0.38490.1559+j0.50170.4666+j1.04820.1580+j0.42360.1535+j0.38490.1580+j0.42360.4615+j1.0651] Ω

Grounded wye–delta transformer data:

kVA1=50 kVA2=100 kVA3=50Ztpu1=0.011+j0.018 Ztpu2=0.01+j0.021 Ztpu3=0.011+j0.018kVLNpri=7.2 kVLLsec=0.48nt=kVLNprikVLLsec=15For i = 1, 2, 3 ZDbasei=kVLLlo2⋅1000kVAi=[4.6082.3044.608]Ztdeli=Ztpui⋅ZDbasei=[0.0507+j0.08290.0230+j0.04840.0507+j0.0829]Ztab=Ztdel1 Ztbc=Ztdel2 Ztca=Ztdel3Grounding resistance: Zg=5 Ω

Compute impedance terms for Equation 10.50:

[Zeq]=[ZthABC]+[Z12ABC][Zeq]=[1.3462+j6.20150.2518+j0.86330.2470+j0.59650.2518+j0.86331.3643+j6.10350.2560+j0.71220.2470+j0.59650.2560+j0.71221.3539+j6.1706]For i = 1,2,3[Zxi]=3∑k=1Zeqi,k=[1.8450+j766131.8722+j7.67901.8569+j7.4793][Zyi]=3∑k=1Z23ABCi,k=[0.7670+j1.96460.7806+j1.97350.7730+j1.8736]Zysum=3∑k=1Zyk=2.3205+j5.8118Ztsum=Ztab+Ztbc+Ztca=0.1244+j0.2143Ztotal=1nt⋅(Zysum+nt2⋅Ztsum+9⋅Zg)=5.0209+j3.6015

Using the Thevenin source voltages and the numerical values from above, create the Equation 10.68 matrices for the B–C–G fault at node 2. Remember that the last four rows of the [C] matrix represent the type of fault as specified in Section 10.2.2.

[Ex]=[7199.5579/0__7199.5579/−120_____7199.5579/120____00000]

[C]=[1.3462+j6.20150.2518+j0.86330.2470+j0.5965−1.8450−7.661310010.2518+j0.86331.3643+j6.10350.2560+j0.7122−1.8722−j7.679001010.2470+j0.59650.2560+j0.71221.3539+j6.1706−1.8569−j7.479300110005.0209+j3.60150.06670.06670.06670.210000000000001000000001000000001]

Solve for the unknown matrix [X]:

[X]=[C]−1⋅[Ex]

The computed short-circuit currents are:

[IfAIfBIfC]=[X1X2X3]=[01342.2/165.84______1194.6/40.15______]It=X4=81.5/143.53_______For i = 1, 2, 3[I1AI1BI1C]=[IfAIfBIfC]−[ItItIt]=[81.5/−36.46_______1267.2/167.24_______1216.09/36.41______]

Note from above that each of the distribution transformer primary windings has a short-circuit current of 81.5 A flowing. The rated currents for the three transformers are:

Iratedi=kVAikVLNhi=[6.9413.896.94] A

The percentage overrated current for the transformers are:

Ioveri=ItIhii⋅100=[1173.6586.81173.6] %

Obviously, the fuses on the distribution transformers are going to blow because of the backfeed current.

This method of analysis for a grounded wye–delta bank with a ground resistance can be used to simulate an ungrounded wye–delta bank by setting the grounding resistance to a very large value. For example, use a grounding resistance of 99,999.

Zg=99,999[IfABC]=[01257.4/167.5______1217.0/36.1_____]It=0[IABC]=[01257.4/167.5______1217.0/36.1_____]

Note that for this case, the backfeed current from the transformer bank is zero.

10.2.3.3 Backfeed Currents Summary

When a wye–delta transformer connection is used, the basic question is whether the neutral should be grounded. In this section, a method of analyzing a simple system was developed for analysis and then demonstrated with an example. It can b e concluded that there is a very significant backfeed current when the neutral is grounded. The backfeed current is in the range of 1000% of the rated transformer currents; so the transformer fuses will blow for the upstream fault. It was also demonstrated that if the grounding resistance is set to a very large value, the backfeed current will be zero, thus simulating an ungrounded wye–delta transformer bank connection. The final conclusion is that the neutral should never be grounded either directly or through a grounding resistance.

10.3 Summary

This chapter has demonstrated the application of the element models that are used in the power-flow analysis and short-circuit analysis of a distribution feeder. The modified ladder iterative technique was used for the power-flow analysis. For a simple radial feeder with no laterals, the examples demonstrated that only the forward and backward sweeps were changed by adding the sweep equations for the new elements. A feeder with laterals and sublaterals will require the ladder forward and backward sweep for each lateral and sublateral. In some cases, there is a need to model a feeder with a limited number of loops. A loop-flow method of modifying the ladder technique was developed, and an example was developed to demonstrate the loop-flow method.

For the short-circuit analysis of a feeder, using the symmetrical component analysis will not work because not all possible short circuits can be modeled. Rather, a method in the phase domain for the computation of any type of short circuit was developed and demonstrated.

The backfeed short-circuit currents due to a grounded wye–delta transformer bank were developed and demonstrated by way of an example. The final idea is to demonstrate that a grounded wye–delta transformer bank should never be used.

The examples in this chapter have been very long and should be used as a learning tool. Many of the interesting operating characteristics of a feeder can only be demonstrated through numerical examples. The examples were designed to illustrate some of these characteristics.

Armed with a computer program using the models and techniques of this text provides the engineer with a powerful tool for solving present-day problems and long-range planning studies.

Problems

The power-flow problems in this set require the application of the modified ladder technique. Students are encouraged to write their own computer programs to solve the problems.

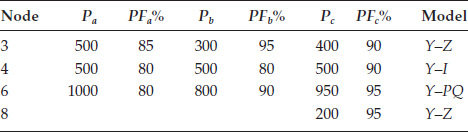

The first six problems of this set will be based upon the system in Figure 10.31.

FIGURE 10.31

Wye homework system.

The substation transformer is connected to an infinite bus with balanced three-phase voltages of 69 kV. The substation transformer is rated:

-

5000 kVA, 69 kV delta–4.16 grounded wye, Z = 1.5 + j8.0%

The phase impedance matrix for a four-wire wye line is:

[z4-wire]=[0.4576+j1.07800.1560+j0.50170.1535+j0.38490.1560+j0.50170.4666+j1.04820.1580+j0.42360.1535+j0.38490.1580+j0.42360.4615+j1.0651] Ω/mile

The secondary voltages of the infinite bus are balanced and being held at 69 kV for all power-flow problems.

The four-wire wye feeder is 0.75 miles long. An unbalanced wye-connected load is located at node 3 and has the following values:

-

Phase a: 750 kVA at 0.85 lagging power factor

-

Phase b: 500 kVA at 0.90 lagging power factor

-

Phase c: 850 kVA at 0.95 lagging power factor

The load at node 4 is zero initially.

10.1 For the system as described earlier and assuming that the regulators are in the neutral position:

-

Determine the forward and backward sweep matrices for the substation transformer and the line segment.

-

Use the modified ladder technique to determine the line-to-ground voltages at node 3. Use a tolerance of 0.0001 per-unit. Give the voltages in actual values in volts and on a 120-V base.

10.2 Three Type B step-voltage regulators are installed in a wye connection at the substation in order to hold the load voltages (node 3) at a voltage level of 121 V and a bandwidth of 2 V.

-

Compute the actual equivalent line impedance between nodes 2 and 3.

-

Use a potential transformer ratio of 2400–120 V and a current transformer ratio of 500:5 A. Determine the R and X compensator settings calibrated in volts and ohms. The settings must be the same for all three regulators.

-

For the load conditions in Problem 10.1 and with the regulators in the neutral position, compute the voltages across the voltage relays in the compensator circuits.

-

Determine the appropriate tap settings for the three regulators to hold the node 3 voltages at 121 V in a bandwidth of 2 V.

-

With the regulator taps set, compute the actual load voltages on a 120-V base.

10.3 A wye-connected three-phase shunt capacitor bank of 300 kvar per phase is installed at node 3. With the regulator compensator settings from Problem 10.2, determine:

-

The new tap settings for the three regulators

-

The voltages at the load on a 120-V base

-

The voltages across the relays in the compensator circuits

10.4 The load at node 4 is served through an ungrounded wye–delta transformer bank. The load is connected in delta with the following values:

-

Phase a–b: 400 kVA at 0.9 factor power factor

-

Phase b–c: 150 kVA at 0.8 lagging power factor

-

Phase c–a: 150 kVA at 0.8 lagging power factor

The three single-phase transformers are rated as:

-

“Lighting transformer”: 500 kVA, 2400–240 V, Z = 0.9 + j3.0%

-

“Power transformers”: 167 kVA, 2400–240 V, Z = 1.0 + j1.6%

Use the original loads and the shunt capacitor bank at node 3 and this new load at node 4 and determine:

-

The voltages on 120 V base at node 3 assuming the regulators are in the neutral position

-

The voltages on 120 V base at node 4 assuming the regulators are in the neutral position

-

The new tap settings for the three regulators

-

The node 3 and node 4 voltages on 120 V base after the regulators have changed tap positions

10.5 Under short-circuit conditions, the infinite bus voltage is the only voltage that is constant. The voltage regulators in the substation are in the neutral position. Determine the short-circuit currents and voltages at nodes 1, 2, and 3 for the following short circuits at node 3.

-

Three-phase to ground

-

Phase b to ground

-

Line-to-line fault on Phases a–c

10.6 A line-to-line fault occurs at node 4. Determine the currents in the fault and on the line segment between nodes 2 and 3. Determine the voltages at nodes 1, 2, 3, and 4.

10.7 A three-wire delta line of length 0.75 miles is serving an unbalanced delta load of:

-

Phase a–b: 600 kVA, 0.9 lagging power factor

-

Phase b–c: 800 kVA, 0.8 lagging power factor

-

Phase c–a: 500 kVA, 0.95 lagging power factor

The phase impedance matrix for the line is:

[z3-wire]=[0.4013+j1.41330.0953+j0.85150.0953+j0.78020.0953+j0.85150.4013+j1.41330.0953+j0.72660.0953+j0.78020.0953+j0.72660.4013+j1.4133] Ω/mile

The line is connected to a constant balanced voltage source of 4.8 kV line-to-line. Determine the load voltages on a-120 V base.

10.8 Add two Type B step-voltage regulators in an open-delta connection using phases A–B and B–C to the system in Problem 10.7. The regulator should be set to hold 121 ± 1 V. Determine the R and X settings and the final tap settings. For the open-delta connection, the R and X settings will be different on the two regulators.

10.9 The three-wire line of Problem 10.7 is connected to a substation transformer connected delta–delta. The substation transformer is connected to a 69-kV infinite bus and is rated:

10,000 kVA, 69 kV delta–4.8 kV delta, Z = 1.6 + j7.8%

Determine the short-circuit currents and substation transformer secondary voltages for the following short circuits at the end of the line:

-

Three-phase

-

Line-to-line between Phases a–b

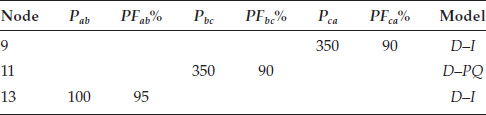

10.10 Two three-phase systems are shown in Figure 10.32.

FIGURE 10.32

Loop-flow system.

In Figure 10.32, the solid lines represent three-phase lines, while the dashed lines represent phase C single-phase lines. The phase conductors are 336,400 26/7 ACSR, and the neutral conductor is 1/0 ACSR. The impedance matrices are:

Three-phase lines:

[z3]=[0.5396+j1.09780.1916+j0.54750.1942+j0.47050.1916+j0.54750.5279+j1.12330.1884+j0.42960.1942+j0.47050.1884+j0.42960.5330+j1.1122]

Single-phase C line:

[z1]=[000000000.5328+j1.1126] Ω/mile

The two sources are 12.47 kV substations operating at rated line-to-line voltages.

The line lengths in feet are:

L12=2000, L23=2500, L27=1000, L45=6000, L56=750, L58=5000

The loads are:

S3a=500 kW at 90% PF S4a=500 kW at 80 PFS3b=600 kW at 85% PF S4b=400 kW at 85 PFS3c=400 kW at 95% PF S4c=600 kW at 90 PFS7c=500 kW at 80 PF S4c=450 kW at 90 PF

The base kVA = 5000, and the base line-to-line kV = 12.470.

The two switches are open.

-

Determine the node voltages.

-

Determine the line currents.

The two switches are closed.

-

Determine the values of the injected currents at nodes 3, 4, 6, and 7.

-