Digital Logic IC Basics

Modern digital ‘logic’ ICs are widely available in three basic types, as either TTL devices (typified by the 74LS00 logic family, etc.), as ‘slow’ CMOS devices (typified by the ‘4000’ logic family), or as ‘fast’ CMOS devices (typified by the 74HC00 and 74AC00 logic families). Each of these families has its own particular advantages and disadvantages, and its own special set of usage rules. This book sets out to explain the basic principles and usage rules, etc., of each of these three basic digital logic families, and to act as a practical usage guide to the vast range of ICs that are available in each of these families. This opening chapter concentrates on digital logic IC basics.

Digital Logic IC Basics

An IC can be simply described as a complete electronic circuit or ‘electronic building block’ that is integrated within one or more semiconductor slices or ‘chips’ and encapsulated in a small multi-pin package, and which can be made fully functional by merely wiring it to a suitable power supply and connecting various pins to appropriate external input, output, and auxiliary networks.

ICs come in both ‘linear’ and ‘digital’ forms. Linear ICs are widely used as pre-amplifiers, power amplifiers, oscillators, and signal processors, etc., and give a basic output that is directly proportional to the magnitude (analogue value) of the input signal, which itself may have any value between zero and some prescribed maximum limit. One of the simplest types of linear IC element is the unity-gain buffer; if a large sine-wave signal is connected to the input of this circuit, it produces a low-impedance output of almost identical form and amplitude, as shown in Figure 1.1(a). Digital ICs, on the other hand, are effectively blind to the precise amplitudes of their input signals, and simply recognize them as being in either a ‘low’ or a ‘high’ state (usually known as ‘logic-0’ and ‘logic-1’ states respectively); their outputs similarly have only two basic states, either ‘low’ or ‘high’ (logic-0 or logic-1). One simple type of digital IC element is the non-inverting buffer; if a large sine-wave signal is connected to the input of this circuit, it produces an output that (ideally) is of purely digital form, as shown in Figure 1.1(b).

Figure 1.1 When a large input sine wave is fed to the input of a linear buffer (a), it produces a good sine-wave output, but when fed to the input of a digital buffer (b) it produces a purely digital output

Digital ICs are available in a variety of rather loosely defined categories such as ‘memory’ ICs, ‘electronic delay-line’ ICs, and ‘microprocessor support’ ICs, etc., but the most widely used category is that known as the ‘logic’ type, in which the ICs are designed around fairly simple logic circuits such as digital buffers, inverters, gates, or flip-flop elements. Digital logic circuits come in a variety of basic types, and can be built using a variety of types of discrete or integrated technologies; Figures 1.2 to 1.7 show a selection of very simple logic circuits that are designed around discrete components.

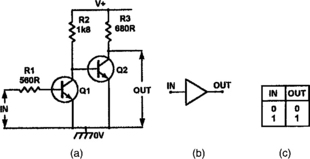

Figure 1.2(a) shows a simple inverting digital buffer (also known as a NOT logic gate), consisting of an unbiased transistor wired in the common-emitter mode, and (b) shows the international symbol that is used to represent it (the arrow-head indicates the direction of signal flow, and the small circle on the symbol’s output indicates the ‘inverting’ action). The circuit action is such that Q1 is cut off (with its output high) when its input is in the zero state, and is driven fully on (with its output pulled low) when its input is high; this information is presented in concise form by the Truth Table of (c), which shows that the output is at logic-1 when the input is at logic-0, and vice versa.

Figure 1.3(a) shows a simple non-inverting digital buffer, consisting of a direct coupled pair of common-emitter (inverter) transistor stages, and (b) shows the arrow-like international symbol that is used to represent it; (c) shows the Truth Table that describes its action, e.g. the output is at logic-0 when the input is at logic-0, and is at logic-1 when the input is at logic-1.

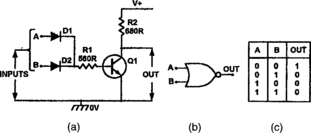

In digital electronics, a ‘gate’ is a logic circuit that opens or gives an ‘output’ (usually defined as a ‘high’ or logic-1 state) only under a certain set of input conditions. Figure 1.4(a) shows a simple 2-input OR gate, made from two diodes and a resistor, and (b) shows the international symbol that is used to represent it; (c) shows its Truth Table (in which the inputs are referred to as A or B), which shows that the output goes to logic-1 if A or B goes to logic-1.

Figure 1.5 shows the circuit, symbol, and Truth Table of a 2-input NOR (Negated-output OR) gate, in which the output is inverted (as indicated by the output circle) and goes to logic-0 if either input goes high.

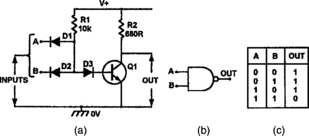

Figure 1.6(a) shows a simple 2-input AND gate, made from two diodes and a resistor, and (b) shows its standard international symbol; (c) shows the AND gate’s Truth Table, which indicates that the output goes to logic-1 only if inputs A and B are at logic-1.

Finally, Figure 1.7 shows the circuit, symbol, and Truth Table of a 2-input NAND (Negated-output AND) gate, in which the output is inverted (as indicated by the output circle) and goes to logic-0 only if both inputs are at logic-1.

Note that although the four basic types of logic gate circuit described above are each shown with only two input terminals, they can in fact be designed or used to accept any desired number of inputs, and can be used to perform a variety of simple ‘logic’ operations. In practice, many types of digital buffer and gate are readily available in IC form, as also are many other digital logic circuits, including flip-flops, latches, shift registers, counters, data selectors, encoders, and decoders, etc.

Practical ‘digital’ ICs may range from relatively simple ‘logic’ devices housing the equivalent of just a few basic gates or buffers, to incredibly complex devices housing the equivalent of tens of thousands of interconnected gates, etc. By convention, the following general terms are used to describe the relative density or complexity of integration:

• SSI (Small Scale Integration); complexity level between 1 and 10 gates.

• MSI (Medium Scale Integration); complexity level between 10 and 100 gates.

• LSI (Large Scale Integration); complexity level between 100 and 1000 gates.

• VLSI (Very Large Scale Integration); complexity level between 1000 and 10,000 gates.

• SLSI (Super Large Scale Integration); complexity level between 10,000 and 100,000 gates.

Note that most ‘logic’ ICs of the types described throughout this book have complexity levels ranging from 4 to 400 gates, and are thus SSI, MSI, or LSI devices. In general terms, most microprocessor ICs and moderately large memory ICs are VLSI devices, and large dynamic RAM (Random Access Memory) ICs are SLSI devices.

Digital Waveform Basics

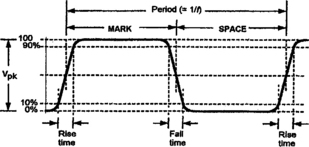

Digital logic ICs are invariably used to process digital waveforms. It is thus pertinent at this point to remind the reader of some basic facts and terms concerning digital waveforms, which are available in either square or pulse form. Figure 1.8 illustrates the basic parameters of a squarewave; in each cycle the wave first switches from zero to some peak voltage value (Vpk) for a fixed period, and then switches low again for a second fixed period, and so on. The time taken for the waveform to rise from 10% to 90% of Vpk is known as its rise time, and that taken for it to drop from 90% to 10% of Vpk is known as its fall time. In each squarewave cycle, the ‘high’ part is known as its mark and the ‘low’ part as its space. In a symmetrical squarewave such as that shown, the mark and space periods are equal and the waveform is said to have a 1:1 Mark–Space (or M–S) ratio, or a 50% duty cycle (since the mark duration forms 50% of the total cycle period). Squarewaves are not necessarily symmetrical, but are always free-running or repetitive, i.e. they cycle repeatedy, with sharply defined mark and space periods.

A pulse waveform can be roughly described as being a bit like a squarewave (complete with rise and fall times, etc.) but with only its mark or its space period sharply defined, the duration of the remaining period being unimportant. Figure 1.9(a) shows a basic ‘positive-going’ pulse waveform, which has a ‘rising’ or positive-going leading edge, and (b) shows a ‘negative-going’ pulse waveform, which has a ‘falling’ or negative-going leading edge. Note that many modern MSI digital ICs such as counter/dividers and shift registers, etc., can be selected or programmed to trigger on either the rising or the falling edge of an input pulse, as desired by the user.

If a near-perfect pulse waveform is fed to the input of a real-life amplifier or logic gate, etc., the resulting output waveform will be distorted both in form and time, as shown in Figure 1.10. Thus, not only will the output waveform’s rise and fall times be increased, but the arrival and termination of the output pulse will be time-delayed relative to that of the input pulse; the mean value of the delays is called the device’s propagation delay. Also, the peaks of the waveform’s rising and falling edges may suffer from various forms of ‘ringing’ or ‘overshoot’ or ‘undershoot’; the magnitudes of all of these distortions varies with the quality or structure of the amplifier or gate, etc.

Figure 1.10 A perfect pulse, fed to the input of a practical amplifier or gate, produces an output pulse that is distorted both in form and time; the output pulse’s time delay is called its ‘propagation delay’, and (in (b)) = (t1+t2)/2

In practice, pulse input waveforms may sometimes be so imperfect that they may need to be ‘conditioned’ before they are suitable for use by modern fast-acting digital ICs. Specifically, they may have such long rise or fall times that they may have to be sharpened up via a Schmitt trigger before they are suitable for use. Again, many mechanically derived ‘pulse’ waveforms such as those generated via switches or contact-breakers, etc., may suffer from severe multiple ‘contact bounce’ problems such as those shown in Figure 1.11(a), in which case they will have to be converted to the ‘clean’ form shown in (b) before they can be usefully used.

Basic Logic-IC Families

Practical digital logic circuits and ICs can be built by using various technologies. The first successful family of digital logic ICs appeared in the mid 1960s; these used a 3.6V supply and employed a simple technology that became known as Resistor–Transistor Logic, or RTL. Figure 1.12 shows the basic circuit of a 3-input RTL NOR gate. RTL was rather slow in operation, having a typical propagation delay (the time taken for a single pulse edge or transition to travel from input to output) of 40ns in a low-power gate, or 12ns in a medium-power gate. RTL is now obsolete.

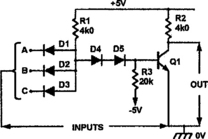

Another early type of IC logic technology, developed in the late 1960s, was based on simple developments of the discrete types of logic circuit shown in Figures 1.2 to 1.7, and was known as Diode–Transistor Logic, or DTL. Figure 1.13 shows the basic circuit of a 3-input DTL NAND gate. DTL used a dual 5 volt power supply, gave a typical propagation delay of 30ns, and gave an output of less than 0.4V in the ‘0’ state and greater than 3.5V in the ‘1’ state. DTL is now obsolete.

Between the late 1960s and mid 1970s, several other promising IC logic technologies appeared, most of them soon disappearing back into oblivion. Among those that came and either went or receded in importance were HTL (High Threshold Logic), ECL (Emitter Coupled Logic), and PML (P-type MOSFET Logic). The most durable of these technologies was ECL, which is still in production and gives very fast operation, but at the cost of very high current/power consumption.

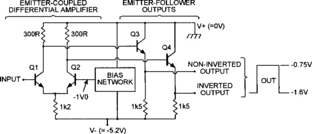

Figure 1.14 shows the basic circuit of the ECL digital amplifier, which is simply a non-saturating emitter–coupled differential amplifier (Q1 and Q2) with emitter–follower output stages (Q3 and Q4), and – because its transistors do not saturate when switched – gives typical propagation delays of only 4ns. Note that the circuit’s V+ line is normally grounded and the V-line is powered at −5.2V, and under this condition the circuit provides nominal digital output swings of only 0.85V, i.e. from a low state of −1.60V to a high state of −0.75V. The circuit’s digital input is applied to the base of Q1, and a non-inverted output is available on Q3 emitter, and an inverted output is available on Q4 emitter. Modern ECL ICs are used only when ultra-high-speed operation is required.

The basic aim of digital IC designers during the late 1960s to early 1970s period was that of devising a technology that was simple to use and which gave a good compromise between high operating speed and low power consumption. The problem here was that conventional transistor-type circuitry, using an output stage of the Figure 1.2 type (as in RTL and DTL systems, etc.) was simply not capable of meeting the last two of these design needs. The essence of this problem – and its ultimate solution – can be understood with the aid of Figure 1.15.

Figure 1.15(a) shows a simplified version of the basic Figure 1.2 circuit, with Q1 replaced by a simple mechanical switch. Remember here that all practical output loads inevitably contain capacitance (typically up to about 30pF in most digital circuits), so it can be seen that this basic circuit will charge (source current into) a capacitive load fairly slowly via R2 when S1 is open, but will discharge it (sink current from it) rapidly via S1 when S1 is closed; thus, circuits of this type produce digital outputs that tend to have long rise times and short fall times; the only way to reduce the rise time is to reduce the R2 value, and that increases S1’s (Q1’s) current consumption by a proportionate amount.

Note that one good way of describing the deficiency of the Figure 1.15(a) logic circuit is to say that its output gives an active pull-down action (via S1), but a passive pull-up action (via R2). Obviously, a far better digital output stage could be made by replacing R2 and S1 with a ganged pair of changeover switches, connected as shown in Figure 1.15(b), so that S2 gives active pull-up action and S1 gives active pull-down action, but so arranged that only one switch can be closed at a time (thus ensuring that the circuit consumes zero quiescent current); such a circuit – with one electronic switch placed above the other – is generally known as a ‘totem-pole’ output stage.

Throughout the late 1960s, digital engineers strove to design a cheap and reliable electronic version of the totem-pole output stage, and then – in the early 1970s – two such technologies hit the commercial market like a bombshell, and went on to form the basis of today’s two dominant digital IC families. The first of these based on bipolar transistor technology, is known as TTL (Transistor–Transistor Logic), and formed the basis of the so-called ‘74’ family of digital ICs that first arrived in 1972. The second based on FET technology, is known as CMOS (Complementary MOS-FET logic), and forms the basis of the rival ‘4000-series’ (and the similar ‘4500-series’) digital IC family that first arrived in about 1975. The TTL and CMOS technologies have vastly different characteristics, but both offer specific technical advantages that make them invaluable in particular applications.

The most significant differences between the technologies of CMOS and TTL ICs can be seen in their basic inverter/buffer networks, which are used (sometimes in slightly modified form) in virtually every IC within the family range of each type of device. Figures 1.16 and 1.17 show the two different basic designs.

The CMOS inverter of Figure 1.16 consists of a complementary pair of MOSFETs, wired in series, with p-channel MOSFET Q1 at the top and n-channel MOSFET Q2 below, and with both high-impedance gates joined together. The pair can be powered from any supply in the 3V to 15V range. When the circuit’s input is at logic-0, the basic action is such that Q1 is driven on and Q2 is cut off, and the output is actively pulled high (to logic-1); note that the output can source (drive) fairly high currents into an external load (via Q1) under this condition, but that the actual inverter stage consumes near-zero current, since Q2 is cut off. When the circuit’s input is at logic-1, the reverse of this action occurs, and Q1 is cut off and Q2 is driven on, and the output is actively pulled low (to logic-0); note that the output can sink (absorb) fairly high currents from an external load (via Q2) under this condition, but that the actual inverter stage consumes near-zero current, since Q1 is cut off.

Thus, the basic CMOS inverter can be used with any supply in the 3V to 15V range, has a very high input impedance, consumes near-zero quiescent current, has an output that switches almost fully between the two supply rails, and can source or sink fairly high output load currents. Typically, a single basic CMOS stage has a propagation delay of about 12 to 60ns, depending on supply voltage.

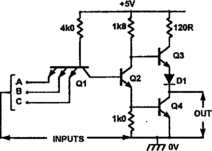

The TTL inverter of Figure 1.17 is split into three sections, consisting of an emitter-driven input (Q1), a phase-splitter (Q2), and a ‘totem-pole’ output stage (Q3–D1–Q4), and must be powered from a 5V supply. When the circuit’s input is pulled down to logic-0, the basic action is such that Q1 is saturated, thus depriving Q2 of base current and causing Q2 and Q4 to cut off, and at the same time causing emitter–follower Q3 to turn on via R2 and give an active pull-up action in which the output has (because of various volt-drops) a typical loaded value of about 3.5V and can source fairly high currents into an external load. Conversely, when the circuit’s input is at logic-1, Q1 is disabled, allowing Q2 to be driven on via R1 and the forward-biased base-collector junction of Q1, thus driving Q4 to saturation and simultaneously cutting off Q3; under this condition Q4 gives an active pull-down action and can sink fairly high currents, and the output takes up a typical loaded value of 400mV. Note that (ignoring external load currents) the circuit consumes a quiescent current of about 1 mA in the logic-1 output state, and 3mA in the logic-0 output state.

Thus, the basic TTL inverter can only be used with a 5V supply, has a very low input impedance, consumes up to 3mA of quiescent current, has an output that does not switch fully between the two supply rails, and can source or sink fairly high load currents. Typically, a single basic TTL stage has a propagation delay of about 12ns.

Basic TTL Circuit Variations

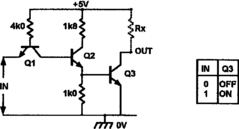

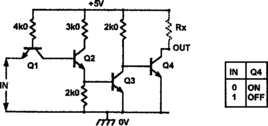

There are five very important variations of the basic Figure 1.17 TTL ‘inverter’ circuit. The simplest of these is the so-called ‘open collector’ TTL circuit, which is shown in basic form in Figure 1.18. Here, output transistor Q3 is cut off when the input is at logic-0, and is driven on when the input is at logic-1. Thus, by wiring an external load resistor between the ‘OUT’ and ‘+5V’ pins, the circuit can be used as a ‘passive pull-up’ voltage inverter that has an output that (when lightly loaded) switches almost fully between zero and the positive supply rail value. Alternatively, it can be used to drive an external load (such as an LED or relay, etc.) that is connected between ‘OUT’ and a positive supply rail, in which case the load activates when a logic-1 input is applied.

The second variation is the non-inverting amplifier or buffer. This is made by simply wiring an additional direct-coupled inverter stage between the phase-splitter and output stages of the standard inverter.

Figure 1.19 shows an ‘open collector’ version of such a circuit, which can be used with an external resistor or load; in this example, Q4 turns on when a logic-0 input is applied.

Figure 1.20 shows a major TTL design variation. Here, the basic inverter circuit is used with a triple-emitter input transistor, to make a 3-input NAND gate in which the output goes low (to logic-0) only when all three inputs are high (in the logic-1 state). In practice, multiple-emitter transistors are widely used within TTL ICs; some TTL gates use an input transistor with as many as a dozen emitters, to make a 12-input gate.

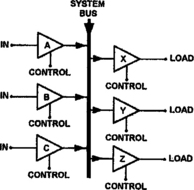

A further variation concerns the use of a ‘Tri-State’ or ‘3-state’ type of output that incorporates additional networks plus an external ENABLE control terminal, which in one state allows the totem-pole output stage to operate in its normal ‘logic-0 or logic-1’ mode, but in the other state disables (turns off) both totem-pole transistors and thus gives an open-circuit (high impedance) output. This facility is useful in allowing several outputs or inputs to be shorted to a common bus or line, as shown in Figure 1.21, and to communicate along that line by ENABLING only one output and one input device at a time.

Figure 1.21 ‘Tri-State’ logic enables several outputs or inputs to be connected to a common bus; only one output/input must be made active at any given moment

The final circuit variation is an ‘application’ one, and concerns the use of an external 2k2 ‘pull-up’ resistor on a totem-pole output stage, as shown in Figure 1.22. This resistor pulls the output (when lightly loaded) up to virtually the full +5V supply value when the output is in the logic-1 state, rather than to only +3.5V; this is sometimes useful when interfacing the output of a TTL IC to the input of a CMOS IC, etc.

The ‘74’-series of Digital ICs

TTL IC technology first hit the electronics engineering scene in a big way in about 1972, when it arrived in the form of an entire range of digital logic ICs that were exceptionally easy to use. The range was an instant international success, and quickly became the world’s leading IC logic system. Its ICs were produced in both commercial and military grades, and carried the prefixes of ‘74’ and ‘54’ respectively; the commercial product range soon became known simply as the ‘74’-series of ICs.

Over the years, the ‘74’-series of ICs has progressively expanded its range of devices and advanced its production technology, so that today the ‘74’-series is as popular and versatile as ever. When first introduced in the early 1970s, the series was based entirely on a simple type of TTL technology, but in later years new sub-families of TTL were introduced in the series, and then various types of CMOS technology were added to it, so that today’s ‘74-series’ incorporates a variety of TTL and CMOS sub-families. Chapter 2 takes a close look at the ‘74’ sub-families of ICs, and explains some basic TTL terminology.