Appendix D. Proof of Condition for Via Placement of Multi-terminal Nets

by E G. Friedman, Ioannis Savidis, Vasilis F. Pavlidis

Three-Dimensional Integrated Circuit Design, 2nd Edition

Appendix D. Proof of Condition for Via Placement of Multi-terminal Nets

by E G. Friedman, Ioannis Savidis, Vasilis F. Pavlidis

Three-Dimensional Integrated Circuit Design, 2nd Edition

- Cover image

- Title page

- Table of Contents

- Copyright

- Dedication

- List of Figures

- About the Authors

- Preface to the Second Edition

- Preface to the First Edition

- Acknowledgments

- Organization of the Book

- Chapter 1. Introduction

- Chapter 2. Manufacturing of Three-Dimensional Packaged Systems

- Chapter 3. Manufacturing Technologies for Three-Dimensional Integrated Circuits

- Chapter 4. Electrical Properties of Through Silicon Vias

- Abstract

- 4.1 Physical Characteristics of a Through Silicon Via

- 4.2 Electrical Model of Through Silicon Via

- 4.3 Modeling a Three-Dimensional Via as a Cylinder

- 4.4 Compact Models

- 4.5 Through Silicon Via Impedance Models

- 4.6 Electrical Characterization Through Numerical Simulation

- 4.7 Case Study—Through Silicon Via Characterization of the MITLL TSV process

- 4.8 Summary

- Chapter 5. Substrate Noise Coupling in Heterogeneous Three-Dimensional ICs

- Chapter 6. Three-Dimensional ICs with Inductive Links

- Chapter 7. Interconnect Prediction Models

- Chapter 8. Cost Considerations for Three-Dimensional Integration

- Chapter 9. Physical Design Techniques for Three-Dimensional ICs

- Chapter 10. Timing Optimization for Two-Terminal Interconnects

- Chapter 11. Timing Optimization for Multiterminal Interconnects

- Chapter 12. Thermal Modeling and Analysis

- Chapter 13. Thermal Management Strategies for Three-Dimensional ICs

- Chapter 14. Case Study: Thermal Coupling in 3-D Integrated Circuits

- Chapter 15. Synchronization in Three-Dimensional ICs

- Chapter 16. Case Study: Clock Distribution Networks for Three-Dimensional ICs

- Abstract

- 16.1 MIT Lincoln Laboratories Three-Dimensional IC Fabrication Technology

- 16.2 Three-Dimensional Test Circuit Architecture

- 16.3 Clock Distribution Network Structures Within the Test Circuit

- 16.4 Models of the Clock Distribution Network Topologies Incorporating Three-Dimensional Via Impedance

- 16.5 Experimental Results

- 16.6 Summary

- Chapter 17. Variability Issues in Three-Dimensional ICs

- Chapter 18. Power Delivery for Three-Dimensional ICs

- Abstract

- 18.1 The Power Delivery Challenge

- 18.2 Models for Three-Dimensional Power Distribution Networks

- 18.3 Through Silicon Via Technologies to Mitigate Power Supply Noise

- 18.4 Decoupling Capacitance for Three-Dimensional Power Distribution Networks

- 18.5 Wire Sizing Methods in Three-Dimensional Power Distribution Networks

- 18.6 Summary

- Chapter 19. Case Study: 3-D Power Distribution Topologies and Models

- Chapter 20. 3-D Circuit Architectures

- Chapter 21. Conclusions

- Appendix A. Enumeration of Gate Pairs in a 3-D IC

- Appendix B. Formal Proof of Optimum Single Via Placement

- Appendix C. Proof of the Two-Terminal Via Placement Heuristic

- Appendix D. Proof of Condition for Via Placement of Multi-terminal Nets

- Appendix E. Correlation of WID Variations for Intratier Buffers

- Appendix F. Extension of the Proposed Model to Include Variations of Wires

- Glossary of Terms

- References

- Index

Proof of Condition for Via Placement of Multi-terminal Nets

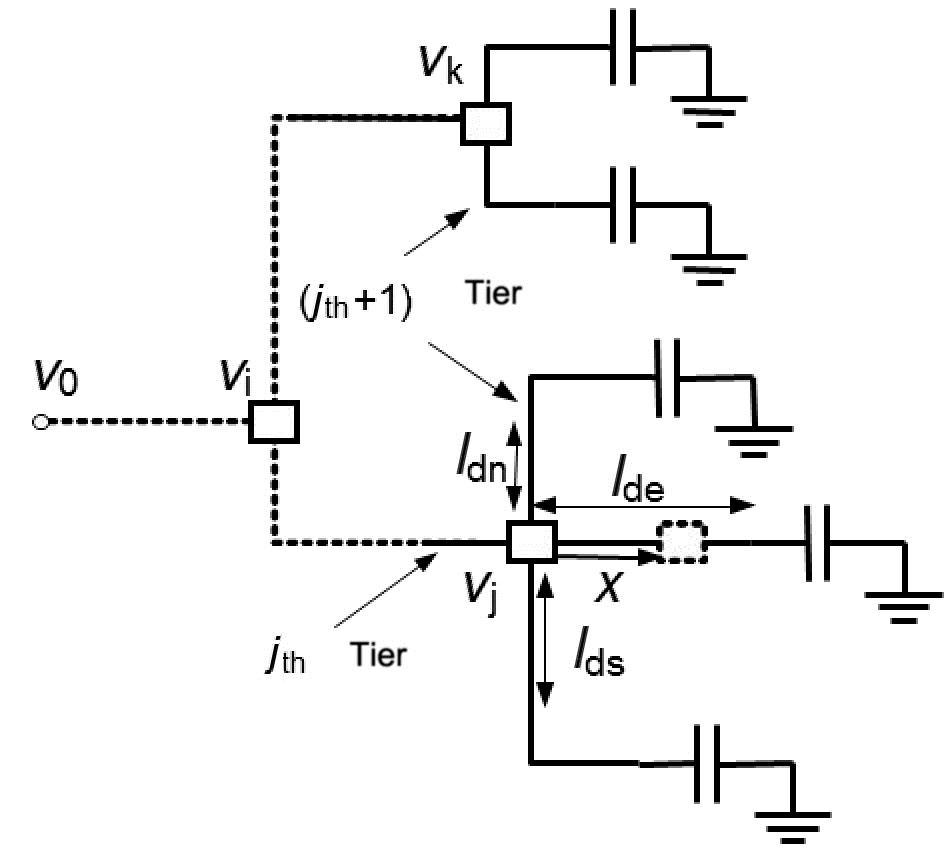

In this appendix, a proof for necessary condition 1 is provided (Fig. D.1).

Condition 1: If rj > rj+1, only a type-1 move for vj can reduce the delay of a tree.

Proof:

Consider Fig. D.1, where the intertier via vj (the solid square) can be placed in any direction de, ds, and dn within, respectively the interval ![]() ,

, ![]() , and

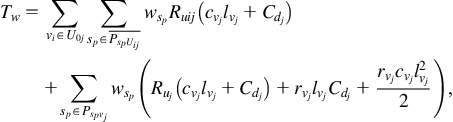

, and ![]() . For the tree shown in Fig. D.1 and removing the terms that are independent of vj, (11.1) is

. For the tree shown in Fig. D.1 and removing the terms that are independent of vj, (11.1) is

(D.1)

(D.1)

where

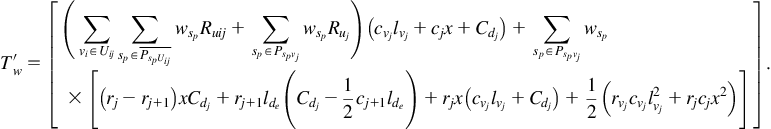

Suppose that a type-2 move is required, shifting vj by x toward the de direction (the dashed square). Expression (11.1) becomes

(D.3)

(D.3)

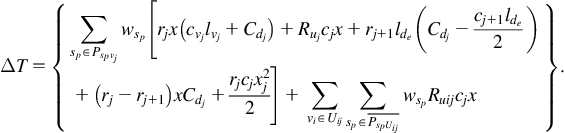

For a type-2 move to reduce the weighted delay of the tree, shifting vj should decrease Tw, or, equivalently, ![]() . Subtracting (D.1) from (D.3) yields

. Subtracting (D.1) from (D.3) yields

(D.4)

(D.4)

Since rj > rj+1 and ![]() from (D.2), (D.3) is always positive and a type-2 move cannot reduce the delay of a tree.

from (D.2), (D.3) is always positive and a type-2 move cannot reduce the delay of a tree.

-

No Comment