APPENDIX A

ANSWERS TO SELECTED PROBLEMS

| 2.1 | Microprocessor: CPU in a single chip.

Single-chip Microcomputer : microprocessor, memory, and I/O in a single chip. |

| 2.4(a)

(d) |

sign = 0, carry = 0, zero = 0, overflow = 0.

sign = 1, carry = 0, zero = 0, overflow = 1. |

| 2.6 (a)

(b) |

20BE

(20BE) = 05, (20BF) = 02. |

| 2.11 | Scalar microprocessor can execute one instruction per cycle. Intel 80486 is a scalar microprocessor.

Superscalar microprocessor can execute more than one instruction per cycle. Intel Pentium is a superscalar microprocessor. |

| 4.2 | Using standard I/O, the microprocessor uses an output pin such as Using memory-mapped I/O, the microprocessor uses an unused address pin to distinguish between memory and I/O. The ports are mapped as memory locations. Memory-oriented instructions are used for performing I/O operation. Intel microprocessors can use either standard or memory-mapped I/O while Motorola microprocessors can use only memory-mapped I/O. |

| 4.4 | Memory-mapping provides the physical addresses for the microcomputer's main memory while memory-mapped I/O maps port addresses into memory locations. |

| 4.7 | Interrupt address vector is the starting address of the service routine. |

| 4.10 | Internal interrupt is generated by exceptional conditions such as division by zero where external interrupts are initiated via microprocessor's interrupt pins. |

| 5.2 | Yes. |

| 5.3 | No. |

| 5.7 | Use the following identities:

|

| 5.8 | Product = 0000 0000 0000 01002 |

| 5.9 | Quotient = −8, Remainder = −1. The sign of the remainder is the same as the sign of the dividend unless remainder is zero. |

| 6.2 | Supervisor mode. |

| 6.7 | TRAP occurs since odd address. |

| 6.9(c) | Privileged |

| 6.13 | $0000 0000 |

| 6.14 |  |

| 6.23 |  |

| 7.2 |  |

| 7.12 | Memory map:

|

| 8.2 | (D1.W) = $4567 |

| 8.4 | CMP.L (0,A0,D5.L*2),D0 |

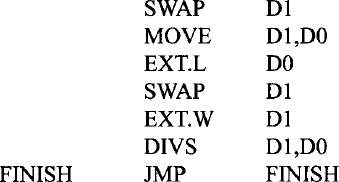

| 8.9 |

|

| 9.8 | *32-bit device: Byte data will be transferred via 68020 D15 - D8 pins.

*8-bit device: Byte data will be transferred via D31 - D24 pins. |

| 10.2 | 20642H |

| 10.4(a) | Implied |

| 10.6 (a) | (EAX) = 00000080H |

| 10.8 | (AL) = 05H, unpacked BCD for 5. |

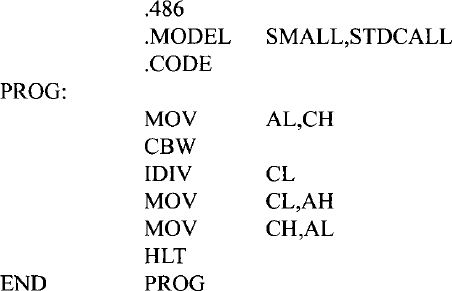

| 10.14 |

|

| 10.21 | (AX) = 1234H |

| 10.28 |

|

| 10.29 |

|

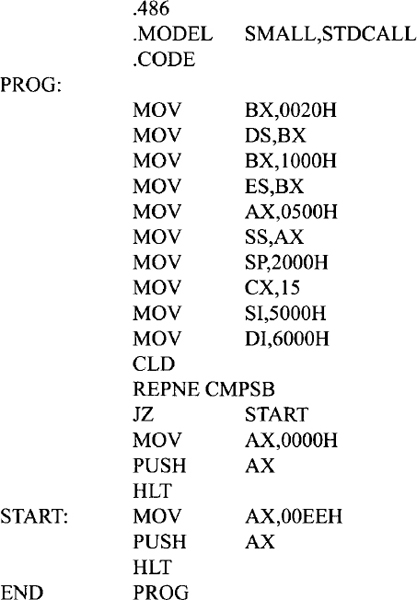

| 11.3 |

|

| 11.6 |

Assuming segment registers are already initialized

|

| 11.7 |

|

| 11.8 |

|

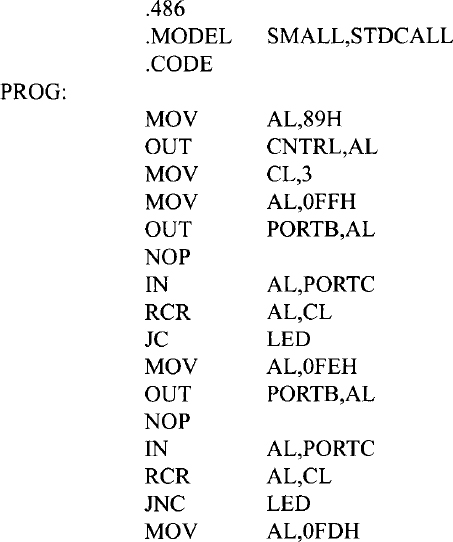

| 12.9 |

|

| 12.12 |

|

..................Content has been hidden....................

You can't read the all page of ebook, please click here login for view all page.