Amplifiers

2.1 AMPLIFIER FUNDAMENTALS

This chapter focuses on the analysis and design of several basic amplifier circuits. Not only is the amplifier circuit a fundamental building block in linear circuits, but the analytical techniques introduced in this chapter will greatly enhance your ability to analyze the circuits presented in subsequent chapters. Regardless of the specific circuit application (e.g., summing circuit, active filter, voltage regulator, and so forth), the op amp itself is simply an amplifier. Therefore, a thorough understanding of op amp behavior in circuits designed specifically as amplifiers will provide us analytical insight that is applicable to nearly all op amp circuits.

An amplifier generally accepts a small signal at its input and produces a larger, amplified version of the signal at its output. The gain (A) or amplification is expressed mathematically as

We may speak of voltage gain, current gain, or power gain. In each of these cases the above equation is valid. If, for example, a particular voltage amplifier produced a 5-volt RMS output when provided with a 2-volt RMS input, we would compute the voltage gain as

There are no units for gain; it is simply a ratio of two numbers. It is also convenient to express a gain ratio in its equivalent decibel (dB) form. The conversion equations are listed below:

The voltage gain of 2.5 on the amplifier discussed in the prior example could be expressed in decibels by applying Equation (2.2):

Thus, we see that an amplifier with a voltage gain of 2.5 also has a voltage gain of 7.96 dB. It should be noted that, technically, the equations cited previously for calculating voltage and current gains in their decibel form require that the input and output impedances be equal. In practice, this is rarely the case. Despite this known error, it is common in the industry to calculate and express the gains as described.

You should also be reminded that fractional gains (i.e., losses) are expressed as negative decibel values.

2.1.2 Frequency Response

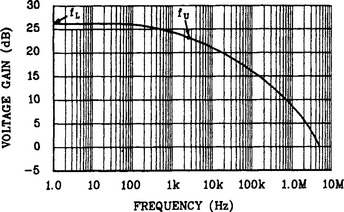

The frequency response of an amplifier describes how its amplification varies with changes in frequency. We often communicate the frequency response of an amplifier in graphical form. Figure 2.1 shows a typical frequency response curve.

FIGURE 2.1 The bandwidth of an amplifier is the range of frequencies between the upper (fU) and lower (fL) cutoff frequencies.

The vertical axis indicates the amplifier’s voltage gain expressed in decibels. The horizontal axis shows the input frequency range.

The frequency response curve shown in Figure 2.1 indicates that the amplifier provides greater gain for low frequencies. Once the input frequency exceeds a certain value, the amplification begins to reduce significantly. Frequencies that are amplified to within 3 dB of the maximum output voltage level are considered as having passed the amplifier. Any frequency whose output voltage is lower than the maximum output voltage by more than 3 dB is considered to have been rejected by the amplifier. The frequency that separates the passband frequencies from the stopband frequencies is called the cutoff frequency. And since -3 dB corresponds to a power ratio of 0.5, the cutoff frequency is also called the half-power point on the frequency response curve.

The bandwidth of an amplifier is measured between the two half-power points. If the frequency response of an amplifier extends to include 0 (i.e., DC), then the bandwidth of the amplifier is the same as the upper cutoff frequency. This is the case for the amplifier represented in Figure 2.1. Here the lower frequency range extends all the way to 0, but in many circuits there will be a lower cutoff frequency that is greater than DC. The bandwidth is expressed as

where fU and fL are the upper and lower cutoff frequencies, respectively.

2.1.3 Feedback

So far in our discussions of op amps, we have considered only the behavior of the op amp itself with no external components. The op amp has been examined only in its open-loop configuration. In most practical applications, a portion of the amplifier’s output is returned through external components to the input of the amplifier. The return signal, called feedback, is then mixed with the incoming signal to determine the effective signal applied to the input of the op amp.

The amplitude, frequency, and phase characteristics of the feedback signal can dramatically alter the behavior of the overall circuit. If the feedback signal has a phase relationship that is additive when mixed with the incoming signal, we refer to the return signal as positive feedback. On the other hand, if the feedback signal is out of phase (optimally 180 degrees) with the input signal, then the effective input signal is reduced and we label it negative feedback. Both forms of feedback are useful in certain op amp applications, but for the remainder of this chapter we will limit our attention to negative feedback.

The external components that provide the feedback path may be frequency selective. That is, if some frequencies pass through the feedback circuit with less attenuation than other frequencies, then we have frequency-selective feedback. This is a very useful form of feedback, but for the remainder of this chapter we will limit our discussion to nonselective feedback methods.

2.2 INVERTING AMPLIFIER

The first circuit we will examine in detail is the inverting amplifier, one of the most common op amp applications. Figure 2.2 shows the schematic diagram of the basic inverting amplifier.

2.2.1 Operation

Under normal operation, an amplified but inverted (i.e., 180° phase shifted) version of the input signal (vI) appears at the output (vO). If the input signal is too large or the amplifier’s gain is too high, then the output signal will be clipped at the positive and negative saturation levels (±VSAT).

Now let us understand how the negative feedback returned through RF affects the amplifier operation. To begin our discussion, let us momentarily freeze the input signal as it passes through 0 volts. At this instant, the op amp has no input voltage (i.e., vD = 0 volts). It is this differential input voltage that is amplified by the gain of the op amp to become the output voltage. In this case, the output voltage will be 0.

Now suppose the output voltage tried to drift in a positive direction. Can you see that this positive change would be felt through RF and would cause the inverting pin (−) of the op amp to become slightly positive? Since essentially no current flows in or out of the op amp input, there is no significant voltage drop across RB. Therefore the (+) input of the op amp is at ground potential. This causes vD to be greater than 0 with the (−) terminal being the most positive. When vD is amplified by the op amp it appears in the output as a negative voltage (inverting amplifier action). This forces the output, which had initially tried to drift in a positive direction, to return to its 0 state. A similar, but opposite, action would occur if the output tried to drift in the negative direction. Thus, as long as the input is held at 0 volts, the output is forced to stay at 0 volts.

Now suppose we allow the input signal to rise to a +2 volt instantaneous level and freeze it for purposes of the following discussion. With +2 volts applied to RI and 0 at the output of the op amp, the voltage divider made up of RF and RI will have two volts across it. Since the (−) terminal of the op amp does not draw any significant current, the voltage divider is essentially unloaded. We can see, even without calculating values, that the (−) input will now be positive. Its value will be somewhat less than 2 volts because of the voltage divider action, but it will definitely be positive. The op amp will now amplify this voltage (vD) to produce a negative-going output. As the output starts increasing in the negative direction, the voltage divider now has a positive voltage (+2 volts) on one end and a negative voltage (increasing output) on the other end. Therefore the (−) input may still be positive, but it will be decreasing as the output gets more negative. If the output goes sufficiently negative, then the (−) pin (vD) will become negative. If, however, this pin ever becomes negative then the voltage would be amplified and appear at the output as a positive going signal. So, you see, for a given instantaneous voltage at the input, the output will quickly ramp up or down until the output voltage is large enough to cause vD to return to its near-0 state. All of this action happens nearly instantaneously so that the output appears to be immediately affected by changes at the input.

We can also see from Figure 2.2 that changes in the output voltage receive greater attenuation than equivalent changes in the input. This is because the output is fed back through a 10-kilohm resistor, but the input is applied to the 1.0-kilohm end of the voltage divider. Thus, if the input makes a 1-volt change, the output will have to make a bigger change in order to compensate and force vD back to its near-0 value. How much the output must change for a given input change is strictly determined by the ratio of the voltage divider resistors. Therefore, since the ratio of output change to input change is actually the gain of the amplifier, we can say that the gain of the circuit is determined by the ratio of RF to RI.

Recall that the internal gain (open-loop gain) of the op amp is not a constant. It varies with different devices (even with the same part number), it is affected by temperature, and it is different for different input frequencies. Now that we have added feedback to our op amp, the overall circuit gain is determined by external components (RF and RI). These can be quite stable and relatively unaffected by temperature, frequency, and so on.

If the input signal is too large or the ratio of RF to RI is too great, then the output voltage will not be able to go high enough (positive or negative) to compensate for the input voltage. When this occurs, we say the amplifier has reached saturation, and the output is clipped or limited at the ±VSAT levels. Under these conditions the output is unable to rise enough to force vD back to its near-0 level. From this you can safely conclude the following important rules regarding negative feedback amplifiers:

1. If the output is below +VSAT and above −VSAT, then vD will be very near 0 volts.

2. If vD is anything other than near 0 volts, then the amplifier will be at one of the two saturation voltages (±VSAT).

When the feedback and input resistor combination in Figure 2.2 are viewed as an unloaded voltage divider, it is easy to determine current flow. Since we know that no significant current is allowed to enter or leave the (−) pin of the op amp, we can conclude that any current flowing through RI must also pass through RF. The polarity of the input and output voltages will determine the direction of this current, but it is important to realize that the value of current through RI is the same as the current through RF.

Since very little current flows in or out of the input terminals of the op amp, we saw that there was essentially no voltage drop across RB which caused the (+) input terminal to remain at ground potential. Since vD is always near 0 as long as the amplifier remains unsaturated, this means that the (−) input terminal must also remain very near to ground potential. This is an important concept. Although the (−) input is not actually grounded, it remains very near ground potential. We commonly refer to this point in the circuit as virtual ground.

RB is included to compensate for errors caused by the fact that some bias current does flow in or out of the op amp terminals. Even though this bias current is small, it can cause a slight voltage drop across RF and RI. This voltage drop is then amplified and appears at the output of the op amp as an error voltage. By including RB in series with the (+) terminal and making its value equal to the parallel combination of RF and RI, we can generate a voltage that is roughly equal, but the opposite polarity from that caused by the drop across RF and RI. The error is generally reduced substantially but will be reduced to 0 only if the bias currents in the two input terminals happen to be equal. We will discuss this in greater detail in Chapter 10.

2.2.2 Numerical Analysis

Let us now learn to analyze the performance of the inverting amplifier circuit. We will calculate all of the following:

4. Slew-rate limiting frequency

5. Maximum output voltage swing

6. Maximum input voltage swing

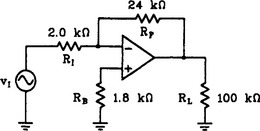

For purposes of our first numerical analysis exercise, let us evaluate the performance of the circuit in Figure 2.3.

Voltage Gain.

You will recall that the voltage gain for this circuit is determined by the ratio of RF to RI or simply

The minus sign is used to remind us of the phase inversion since this is an inverting amplifier. Do not interpret the minus as a loss or a reduction in signal strength. For the circuit in Figure 2.3 the voltage gain will be

We can express this as a decibel gain by applying Equation (2.2):

In this conversion, we must be particularly careful not to include the minus sign as part of the voltage gain. First, we will be unable to compute the logarithm. Second, if we tried to put the minus sign in after the calculation the resulting negative decibel answer would be misinterpreted as a loss.

It is important to note that the voltage gain computed in this section is the ideal closed-loop voltage gain of the circuit. The actual circuit gain will roll off as the input frequency is increased. This effect is discussed below as part of the discussion on bandwidth.

Input Impedance.

The input impedance of the amplifier shown in Figure 2.3 is that resistance (or impedance) as seen by the source (vI). You will recall that the voltage between the (+) and (−) terminals of the op amp (vD) will always be about 0 unless the amplifier is saturated. Since the (+) terminal is connected to ground (via RB) in the inverting amplifier circuit, it is reasonable to assume that the (−) pin will always be near ground potential even though it is not and cannot be connected directly to ground. But, since the (−) input is essentially at ground potential we call this point in the circuit a virtual ground.

Considering that the (−) pin is a virtual ground, it becomes apparent that the input impedance seen by the source is simply RI. That is, as far as current demand is concerned, resistor RI is effectively connected across the signal source. The equation for input impedance then is given by Equation (2.7).

For the case of the inverting amplifier shown in Figure 2.3, the input impedance is computed as follows:

In general, as long as the (−) pin remains at a virtual ground potential, the input impedance will be equal to the impedance between this pin and the source. If the impedance is more complex (e.g., resistor capacitor combination), then you must use complex numbers to represent the impedance. The basic method, however, remains the same.

Input Current Requirement.

Ohm’s Law can be used to calculate the amount of current that must be supplied by the source. Recall that essentially no current flows into or out of the (−) terminal of the op amp. Therefore the only current supplied by the source is that drawn by RI. Since RI is effectively in parallel with the source due to the effect of the virtual ground, the input current can be computed as follows:

Since this is a sinusoidal waveform, we could easily convert this to an RMS value if desired as shown:

In our present case, the RMS value is found as follows:

As long as the input source can supply at least this much current without reducing its output, the op amp circuit will not load the source.

Maximum Output Voltage Swing.

The output voltage of an op amp is limited by the positive and negative saturation voltages. These can both be approximated as 2 volts less than the DC supply voltage. Since the DC supply in Figure 2.3 is ±15 volts, the saturation voltages will be +13 volts and -13 volts for the positive and negative limits, respectively. Thus, the maximum output voltage swing is computed as follows:

For the circuit in Figure 2.3, the maximum output voltage swing is found as shown:

Since both DC supplies are equal, the output can swing equally above and below 0. This is the normal condition.

If you desire to be more accurate in the estimation of output saturation voltage, you may refer to the manufacture’s data sheet in Appendix 1. The manufacturer lists minimum and typical output voltage swings for different values of load resistance.

Slew-Rate Limiting Frequency.

It should also be noted that the above maximum output is only obtainable for frequencies below the point where slew rate limiting occurs. This frequency can be estimated with the following equation:

In the case of the circuit being considered, the highest frequency that can produce a full output swing without distortion caused by slew rate limiting is computed as

If we attempt to amplify frequencies higher than 6.12 kilohertz (and full amplitude) with the circuit shown in Figure 2.3, then the output will be nonsinusoidal. Once the input frequency goes higher than a certain frequency (about 9 kilohertz in this case), then the output amplitude begins to drop in addition to the distorted shape.

Maximum Input Voltage Swing.

We have computed the voltage gain of the circuit, and we know the maximum output voltage swing. We, therefore, have enough information to compute the largest input signal that can be applied without driving the amplifier into saturation.

Calculations for the present case are shown below:

Since we are working with sinusoidal waveforms, we might choose to express this value as peak or RMS as shown below:

For our present circuit, we have

So, for the amplifier circuit presented in Figure 2.3, input signals as great as 756.5 millivolts RMS can be amplified without saturation clipping. If you attempt to amplify larger signals, then the peaks on the output waveform will be flattened at the output saturation voltage limits.

Output Impedance.

You will recall from Chapter 1 that the output impedance of an op amp is generally quite low. The data sheet in Appendix 1 lists 75 ohms as a typical output resistance for a 741 op amp. This value, however, is the open-loop output resistance. When negative feedback is added to the amplifier (as in Figure 2.3) the effective output impedance decreases sharply. The value of effective output impedance can be approximated as shown:

where AOL is the open loop gain of the op amp at the specified frequency. This can be read from the manufacturer’s graphical data (see Appendix 1) showing open-loop gain as a function of frequency. Alternatively, you may estimate it as

where fIN is the specific input frequency being considered.

For the circuit in Figure 2.3, the closed-loop output impedance can be estimated at 1000 hertz as follows. First we compute the open-loop gain at 1000 hertz by applying Equation (2.16):

Next compute the effective output impedance with Equation (2.15):

This low value approaches our ideal value of 0 ohms. Now, as an illustration, recompute the value of output impedance at a higher frequency of 5 kilohertz.

First compute AOL with Equation (2.16).

Next compute the effective output impedance with Equation (2.15).

This value is significantly higher than our first estimate and clearly shows the increase in output resistance as the input frequency is increased.

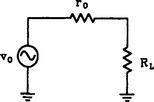

How does a particular value of output impedance affect the performance of the amplifier circuit? To understand the effects, we can examine the equivalent circuit shown in Figure 2.4. Here we see a voltage source labeled vO driving a series circuit.

FIGURE 2.4 The equivalent output circuit of an op amp can be used to judge the effects of output impedance (rO).

The vO source is that voltage that would be present at the output of the op amp if the output impedance were truly 0 ohms. You can see that this ideal voltage (vO) is divided between the output impedance (rO), which is internal to the op amp, and RL, which is the op amp load. The voltage reaching the load can be computed with the voltage divider equation.

Let us compute the actual load voltage in Figure 2.3 at a frequency of 5 kilohertz. First we compute the ideal output voltage Equation (2.1):

We have found the value of rO at 5 kilohertz to be 4.96 ohms. Using the method shown in Figure 2.4, we can now determine the actual load voltage with Equation (2.17).

At a frequency of 5 kilohertz when the output resistance has increased to nearly 5 ohms, the effect of nonideal output resistance is minimal. Problems could be anticipated when the output resistance exceeds 1 percent of the value of load resistance.

Although the preceding calculation illustrates the effects of output resistance, it is valid only if we are below the frequency that causes slew rate limiting (fSRL). If fSRL is exceeded, we can expect the actual output to be much lower than the value computed with Equation (2.17), and the output will be nonsinusoidal in shape. Additionally, this method is inappropriate if the output drive capability of the op amp is exceeded.

Output Current Capability.

The output of the op amp in Figure 2.3 must supply two currents: the current through the feedback resistor (iF) and the current to the load resistor (iL). It is the sum of these currents that flows into or out of the output of the op amp.

The output of many (but not all) op amps is short circuit protected. That is, the output may be shorted directly to ground or to either DC supply voltage without damaging the op amp. For a protected op amp (such as the 741), the output current capability is not determined by the maximum allowable current before damage, but rather depends on the amount of reduced output voltage the application can tolerate.

With no output current being supplied to the load, the output voltage stays at the expected vO level, and the total output current is equal to iF. As the load current is increased (load resistance decreased), the actual output voltage begins to drop as shown in the previous section. Finally, if the load resistance is reduced all the way to 0 ohms, the output current will be limited to a safe value. This value can be found in the data sheet (Appendix 1), and is 20 milliamps for the 741 device.

As the load resistance varies from infinity (open) to zero (short), the output current from the op amp varies from iF to 20 milliamps. The limiting factor is the amount of reduction that can be tolerated on the output voltage.

The amount of current (iF) flowing through the feedback resistor is easily computed with Ohm’s Law as

On an unprotected op amp, the value of load current plus the value of feedback current must be kept below the stated output current rating. If this value is not supplied in the data sheet, then it can be estimated by using the maximum power dissipation data; recall that power = voltage × current.

Minimum Value of Load Resistance.

The minimum value of load resistance is determined by the maximum value of output current (determined in the previous section). The actual computation is essentially Ohm’s Law:

where iL is the maximum allowable output current of the op amp minus the current (if) flowing through the feedback circuit, and vL is the minimum acceptable output voltage.

Note that in many, if not most, applications, the value of output current needed for the load is substantially below the limiting value, so no significant loading occurs.

Let us assume that the application shown in Figure 2.3 requires us to have at least 1.19 volts across the load when 100 millivolts is applied to the input terminal. Let us further assume that the frequency of interest is 5 kilohertz. From previous calculations we know that the voltage gain (AV) is 12.2 (ignoring the effects of bandwidth described in the next section) and that the output resistance at 5 kilohertz is 4.96 ohms.

Figure 2.5 shows the equivalent circuit at this point. The value of iO can be computed with Ohm’s Law.

The value of iF can also be computed using Ohm’s Law, Equation (2.18).

Kirchhoff’s Current Law can now be used to determine the value of load current (iL).

Calculations for the present example are shown below:

Using Ohm’s Law, Equation (2.19), we can now compute the value of RL.

With this small value of load resistance, we would not be able to provide full-range voltage swings on the output because of excessive loading.

In the foregoing calculations (as with most calculations presented in this book), it is not important to remember all of the equations. Rather, strive to understand the concept and realize that most of what we are discussing is centered on basic electronics principles that you learned when you studied introductory AC and DC circuits.

Bandwidth.

Although the bandwidth of an ideal op amp is considered to be infinite, the bandwidth of real op amps and the associate amplifier circuit are definitely restricted. In the case of the circuit shown in Figure 2.3, the lower cutoff frequency is essentially 0. That is, since the op amp responds all the way down to DC, and since there are no reactive components to reject the lower frequencies, the amplifier circuit will operate with frequencies as low as DC.

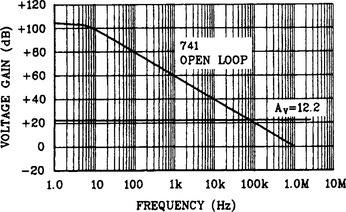

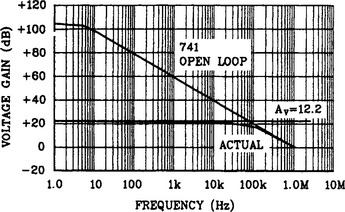

The upper cutoff frequency is quite a different story. Figure 2.6 shows the open-loop frequency response (upper curve) for a 741 op amp. This is the same curve presented in the manufacturer’s data sheet as open-loop voltage gain as a function of frequency. Also drawn on the graph in Figure 2.6 is a line showing a voltage gain of 12.2. This is the ideal closed-loop gain that we calculated for the circuit in Figure 2.3.

Notice that the difference between the open- and closed-loop gain curves is maximum at low frequencies. As the frequency increases, the difference between the two curves becomes less. Near the right side of the graph, the two curves actually intersect. What really happens to the overall circuit gain as the frequency increases?

The derivation of the formula for amplifier voltage gain (AV = −RF/RI) was based on the assumption that the op amp had an infinite (or at least a very high) voltage gain. This allowed us to make the assumption that the differential input voltage (vD) was 0. As you can see from the graph in Figure 2.6, our assumptions are reasonable for low frequencies. That is, the open-loop voltage gain is very high. But as the frequency increases and the open-loop gain rolls off, our assumptions begin to lose their validity. The most obvious proof of this exists beyond the point of intersection of the open- and closed-loop curves. In the region to the right of the intersection point, the open-loop gain is actually lower than our calculated closed-loop gain, thus making it impossible for our circuit to deliver the desired amplification.

It is common to compute bandwidth in a circuit like that shown in Figure 2.3 by applying the following equation:

where fUG is the unity gain frequency of the op amp. Substituting values and computing gives us the following:

The actual frequency response for the circuit shown in Figure 2.3 is plotted in Figure 2.7. This represents the circuit’s real behavior. Two additional lines are superimposed on the plot for reference: the open-loop frequency response curve of the 741 op amp and the ideal gain curve of the circuit in Figure 2.3.

FIGURE 2.7 Actual frequency response of the circuit shown in Figure 2.3.

Power Supply Rejection Ratio.

If the DC supply lines (V+ and V−) have noise, particularly high-frequency noise, these noise signals may affect the output signal. The degree to which the op amp is affected by the power supply noise is called the power supply rejection ratio (PSRR). The manufacturer’s data sheet normally expresses this parameter in microvolts per volt. To determine the magnitude of the noise signal on the output for a given amplitude of noise signal on the supply lines, we can use the following calculation:

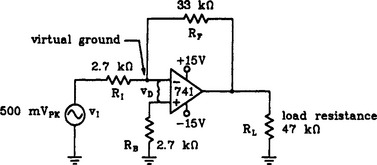

where vNO, vN, RF, RI, and PSRR are the values of the output noise signal, the noise signal on the DC supply lines, the feedback resistor, the input resistor, and the power supply rejection ratio, respectively. For example, refer to Figure 2.8.

FIGURE 2.8 An inverting amplifier circuit used to demonstrate the effects of the power supply rejection ratio.

The manufacturer’s data sheet in Appendix 1 for a 741 op amp lists the power supply rejection ratio as ranging from 30 to 150 microvolts per volt. Thus, the worst-case effect on the output voltage for the circuit in Figure 2.8 is computed with Equation (2.23) as

In other words, the amplitude of the power line noise (vN) will be reduced by a factor of 0.003525. This means, for example, that if the DC supply lines have noise signals of 100 millivolts peak-to-peak, then we can anticipate a similar signal in the output with an amplitude of about

2.2.3 Practical Design Techniques

The following design procedures will enable you to design inverting op amp circuits for many applications. Although certain nonideal considerations are included in the design method, additional nonideal characteristics are described in Chapter 10.

To begin the design process, you must determine the following requirements based on the intended application:

As an example of the design process, let us design an inverting amplifier with the following characteristics:

| 1. Voltage gain | 12 |

| 2. Maximum input current | 250 microamperes RMS |

| 3. Frequency range | 20 hertz to 2.5 kilohertz |

| 4. Load resistance | 100 kilohms |

| 5. Maximum input voltage | 500 millivolts RMS, 0-volt reference |

Determine an Initial Value for RI.

The minimum value for RI is determined by the maximum input voltage and the maximum input current and is computed with Ohm’s Law as follows:

In this case, the calculations are

As a general rule, you should avoid designing amplifiers with input resistances of less than 1000 ohms unless you have a specific need for them. In our present case, the computed minimum (2.0 kilohms) is greater than 1000 ohms, so we will use the computed value. It should also be noted that the minimum input impedance is often determined by the needs of the application.

Determine the Value of RF.

RF can be computed from the voltage gain equation, Equation (2.6):

Note that the inversion sign is omitted from the equation when computing a resistance value. For the present example, we compute RF as follows:

Determine the Required Unity Gain Frequency.

The minimum unity gain frequency for the op amp can be estimated by applying Equation (2.22). For the present case, we have

Since this is well below the 1.0-megahertz unity gain frequency of the 741, we should be able to use the 741 in this application (with regard to bandwidth).

Determine the Minimum Supply Voltages.

The minimum supply voltages are computed by simply ensuring that the maximum expected output voltage swing is no greater than the ±VSAT values. The maximum output swing can be found by using the basic equation, Equation (2.1), for voltage gain:

In our particular example, the maximum output voltage will be

Notice the multiplying factor 1.414 to convert our input voltage (given in RMS) to a peak or worst-case value. The manufacturer’s data sheet in Appendix 1 indicates that the 741 op amp will produce at least a ±12-volt output swing with a ±15-volt supply voltage as long as the load resistor is at least 10 kilohms. Thus, we can infer that we have a worst-case internal voltage drop of 15 – 12, or 3 volts. This means that the minimum power supply voltage for our circuit must be higher than the maximum output voltage by the amount of the internal voltage drop (VINT). That is,

For our particular case, the minimum power supply voltages will be

Anything greater than ±11.48 volts for the DC supply will be adequate; therefore, let us choose the standard values of ±15 volts for our application.

Determine the Required Slew Rate.

The required slew rate of the op amp is affected by the highest operating frequency and the maximum output voltage swing. In our present case, the highest input frequency has been specified as 2.5 kilohertz. The maximum peak-to-peak output voltage swing (vO(max)) was previously computed as 16.96 volts. The minimum required slew rate for the op amp is determined by rearranging Equation (2.11) to yield

Since the slew rate of the 741 exceeds this minimum value, we can continue with our initial op amp selection. If the above calculation indicates a higher requirement than our preliminary op amp selection can deliver, then another op amp must be selected that has a higher slew rate.

Calculate the Value of Compensation Resistor (RB).

The compensation resistor (RB) reduces the error in the output voltage caused by the voltage drops that result from the op amp’s input bias currents. To achieve maximum error reduction, we try to place equal resistances between both op amp input terminals and ground. If we were to apply Thevenin’s Theorem to the inverting input circuit, we would see that resistors RF and RI are effectively in parallel. This means that the optimum value for RB is simply the combined value of RF and RI in parallel.

For the present example, we compute RB as follows:

The final schematic is shown in Figure 2.9.

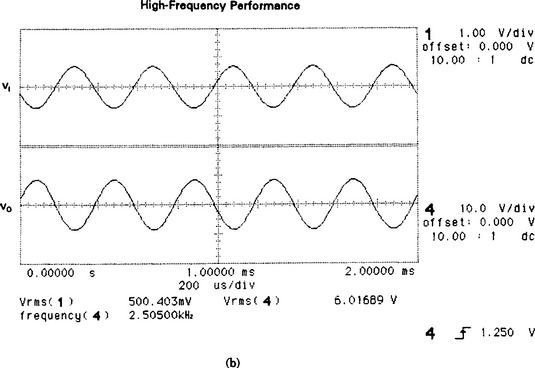

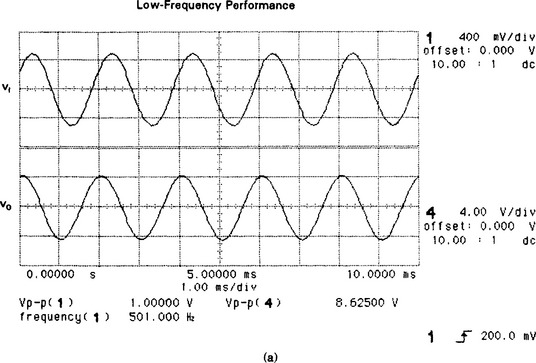

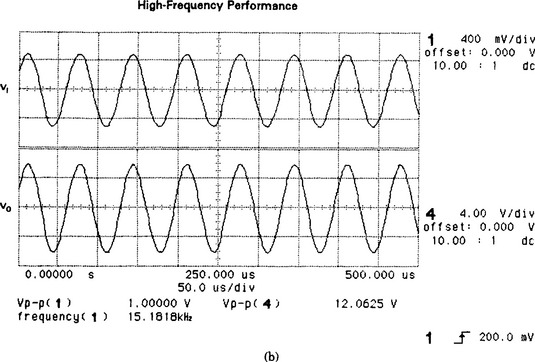

The actual behavior of the circuit is indicated in Figure 2.10 by an oscilloscope display. The measured performance is compared to the design goals in Table 2.1.

TABLE 2.1

| Parameter | Design Goal | Measured Value |

| Voltage gain | 12 | 11.7–12 |

| Frequency range | 20 Hz–2.5 kHz | <20 Hz to 2.5 kHz |

FIGURE 2.10 Oscilloscope displays showing the performance of the inverting amplifier shown in Figure 2.9. (Test equipment courtesy of Hewlett-Packard Company.)

2.3 NONINVERTING AMPLIFIER

Figure 2.11 shows the schematic diagram of a basic noninverting amplifier. As you might expect, the input signal is applied to the (+), or noninverting, input. Resistor RB is a compensation resistor similar to that described for the inverting amplifier. Because it has such a tiny current through it, we will ignore its effects for the immediate discussion.

Resistor RF and resistor RI form a voltage divider between the output terminal and ground. That portion of the output that appears across RI will provide the input to the (−) input terminal. The input signal (vI) supplies the voltage to the (+) input terminal. The difference between these two voltages (vD) is amplified by the open-loop gain of the op amp. Recall that as long as the output of the op amp is in the linear range (i.e., not saturated), the magnitude of vD will be very near 0 volts. Since the (+) input terminal is equal to vI, and since vD is approximately 0, we can conclude that the voltage on the (−) input terminal must also be nearly equal to vI. Recall that the source for the (−) input voltage is the output of the op amp. Now we see that the output will go as high as necessary in order to develop enough voltage drop across RI to equal vI.

Suppose, for example, that the input voltage (vI) made a sudden increase from 0 volts to some positive level. At this first instant, the (+) input of the op amp would be positive and the (−) input would still be at its previous 0-volt level. The voltage vD would now be amplified. Since the (+) input is more positive, the output rises as quickly as possible in the positive direction. As the output goes positive, a portion is fed back through the RF and RI voltage divider to the (−) input. Since the (−) input is becoming more positive, the value of vD is decreasing. That is, the two input terminal voltages are getting closer together. Finally, the output of the amplifier will stop going in the positive direction whenever the (−) input has come to within a few microvolts of the (+) input.

Now consider how high the output voltage had to go in order to bring the (−) input up to the same voltage as the (+) input. You can see that it is strictly the values of the voltage divider RF and RI that determine the amount of output voltage change required. Thus, for a given input voltage change, the output will make a corresponding change. The magnitude of the change is the gain of the amplifier and is largely determined by the ratio of RF to RI. This action is explained with mathematics in the following section.

Additionally note that as the input went positive, the output went positive. That is, the amplifier configuration is noninverting.

2.3.2 Numerical Analysis

Much of our analysis for the inverting amplifier is applicable to the noninverting amplifier circuit. We will determine a method to enable us to compute the following circuit characteristics:

For purposes of this discussion, let us analyze the noninverting amplifier circuit shown in Figure 2.12.

Voltage Gain.

We know by inspection of the circuit in Figure 2.12 that the voltage on the (+) input is approximately equal to vI. That is, there is no significant voltage drop across RB because the only current allowed to flow through RB is the op amp bias current (ideally 0). We also know from previous discussions that the voltage between the (+) and (−) input terminals (vD) is very near 0 volts. Thus, we may rightly conclude that the voltage on the (−) pin is approximately equal to the value of VI.

Ohm’s Law can be used to compute the current through RI as follows:

For the circuit in Figure 2.12, we have

Since negligible current flows into or out of the input of the op amp, we will assume that all of the current flowing through RI continues through RF, according to Kirchhoff’s Current Law. The voltage drop across RF can be computed by applying Ohm’s Law.

The output voltage can be determined through application of Kirchhoff’s Voltage Law. That is, we know the voltage on the (−) input is 2.0 volts peak. The output voltage will be greater than this by the amount of voltage drop across RF. It is computed as

The voltage gain can be computed by the basic gain equation, Equation (2.1), as shown:

Recall from an earlier discussion that the voltage gain of the circuit is largely determined by the ratio of RF to RI. More specifically, the low-frequency or ideal voltage gain of the circuit can also be calculated with the following equation:

In our case, the calculations are

This latter method is the most common, but the former provides additional insight into circuit operation and the application of basic electronics principles.

The voltage can be expressed in decibels if desired, as we did with inverting amplifiers. In our present example, the equivalent voltage gain expressed in decibels is:

Note that the voltage gain computed in this section is the ideal closed-loop voltage gain of the circuit. The actual circuit gain will roll off as the input frequency is increased, just as it did with inverting amplifiers. This effect is discussed below as part of the discussion on bandwidth.

Input Impedance.

The input impedance of the noninverting amplifier circuit (refer to Figure 2.12) is essentially equal to the input impedance of the (+) input terminal of the op amp modified by the feedback effects. That is, the only current leaving the source must flow into or out of the op amp as bias current for the (+) input. The manufacturer’s data sheet for a 741 is shown in Appendix 1. It indicates that the input resistance is at least 0.3 megohms and is typically about 2.0 megohms. Recall that this is the effective resistance between the two op amp inputs. By considering the output impedance to be near 0, we can sketch the equivalent circuit shown in Figure 2.13(a).

FIGURE 2.13 An equivalent circuit used to estimate the input impedance of the noninverting amplifier shown in Figure 2.12.

Let us make the following substitution for the value of vO:

This, of course, comes from Equation (2.1) and Equation (2.28). If we now apply Thevenin’s Theorem to the portion of the circuit to the right of the dotted line, we obtain the equivalent circuit shown in Figure 2.13(b). Notice that the resistance in our equivalent circuit has the same voltage (2 VPK) on both ends, which produces a net voltage of 0. If there is no voltage, there will be no current, so the effective input impedance is infinite. This represents the ideal condition.

In a real op amp circuit, the differential input voltage (vD) is greater than 0 and increases as the frequency increases. With reference to Figure 2.13(b), as the input frequency increases, the two voltage sources become more and more unequal. This causes a difference in potential across the resistance in the circuit, which in turn produces a current flow. The increasing current corresponds to a decreasing input impedance. Although the actual input impedance is quite high and can normally be assumed to be infinite, it can be approximated by the following equation:

where ROP is the value of input resistance provided by the manufacturer and AV is the open-loop voltage gain of the op amp. For the circuit shown in Figure 2.12, we can estimate input resistance at low frequencies as

If we had used the more typical value of 2.0 megohms for the op amp resistance (ROP), we would have gotten a much higher value for input resistance. In either case, the actual effective input resistance is extremely high. This high input resistance is one of the primary advantages of the noninverting amplifier in many applications.

Input Current Requirement.

The input current can be estimated by applying Ohm’s Law to the input circuit as follows:

Even this is a worst-case value. If we had used the higher typical value for input resistance, we would have computed an even smaller value. For many, if not most, applications, this input current can be considered negligible. If it becomes necessary to consider this current, then additional considerations must be made because the exact value of input resistance varies considerably with temperature and frequency.

Maximum Output Voltage Swing.

As we found with the inverting amplifier, the output voltage of an op amp is limited by the ±VSAT levels. For most applications utilizing a bipolar op amp, the saturation voltages can be estimated at about 2 volts less than the DC supply voltage. In the case of Figure 2.12, we compute the maximum output swing, Equation (2.10), as

If a more accurate value is desired, the manufacturer’s data sheet can be used to find a more precise value for the worst-case saturation voltage.

Slew-Rate Limiting Frequency.

The highest frequency that can be amplified without distorting the waveform, because of the slew rate limitation of the op amp, is given by Equation 2.11.

If it is known for certain that the actual output swing will never be required to reach its limits, then the lower actual output swing can be used in place of vO(max) in the above calculation.

Maximum Input Voltage Swing.

The maximum input voltage swing is simply the highest input voltage that can be applied without driving the output past the saturation point. It is computed in the same manner as that for the inverting amplifier.

Since we are working with sinusoidal waveforms, we might choose to express this value as peak, as in Equation (2.13), or RMS, as in Equation (2.14), as shown:

If you attempt to amplify signals larger than 1.425 volts RMS, then the peaks on the output waveform will be flattened at the output saturation voltage limits.

Output Impedance.

You will recall from the analysis of the inverting amplifier that the effective output impedance decreases sharply from the open-loop value stated in the manufacturer’s data sheets. The value of effective output impedance can be approximated by applying Equation (2.15).

where AOL is the open-loop gain of the op amp at a particular frequency. For the circuit in Figure 2.12, the open-loop gain at 2500 hertz is computed with Equation (2.16) as

The output impedance at 2500 hertz can then be estimated as

In most cases, the output impedance is so low relative to the value of load resistance that the output voltage is essentially unaffected, but you can always be sure by performing the voltage divider calculation outlined in Section 2.2.2.

Output Current Capability.

If the output of the op amp is short-circuit protected (as in the 741), then the output current capability is limited by the maximum allowable drop in output voltage for the given application. This can be estimated with Ohm’s Law as discussed in the preceding section. Recall from our discussion of inverting amplifiers that the output must supply both load resistor current and the current through the feedback resistor. The feedback current is computed using Ohm’s Law. For this particular circuit, the calculations are

With no output current being supplied to the load, the output voltage stays at the expected vO level and the total output current is equal to iF. As the load current is increased (load resistance is decreased), the actual output voltage begins to drop because of the voltage divider action described in the previous section. Finally, if the load resistance is reduced all the way to 0 ohms, the output current will be limited to the short circuit value. This value can be found in the data sheet (Appendix 1) and is 20 milliamperes for the 741 device.

As the load resistance varies from infinity (open) to 0 (short), the output current from the op amp varies from iF to 20 milliamperes. The limiting factor is the amount of reduction that can be tolerated on the output voltage.

On an unprotected op amp, the value of load current plus the value of feedback current must be kept below the stated output current rating. If this value is not supplied in the data sheet, it can be estimated by using the maximum power dissipation data; recall that power = voltage × current.

Bandwidth.

The discussion of bandwidth presented for the inverting amplifier circuit is also applicable to the noninverting configuration. That is, as long as the circuit has no reactive components, the frequency response will extend all the way down to DC on the low-frequency end. We can estimate the high-frequency end of the frequency response by applying Equation (2.22):

Recall that the open-loop gain of the op amp falls off rapidly as the input frequency is increased above a few hertz. As the open-loop gain value approaches the computed closed-loop gain value, the actual circuit gain also begins to drop. Thus, we begin to experience increased errors in our gain calculations as the frequency is increased.

For these equations to be valid, it is important that the op amp output voltage swing be small enough to avoid the effects of slew rate limiting. The highest amplitude that can be amplified at a given frequency without the effects of slew rate limiting is given as

The slew rate is determined by the particular amplifier, f is the frequency of interest, and vO(max) is the highest peak-to-peak amplitude in the output before slew rate limiting begins to distort the signal. In the present case, if we try to operate at the upper cutoff frequency (155 kHz), we have to keep the output voltage below the value computed:

Power Supply Rejection Ratio.

The power supply rejection ratio provides us with an indication of the degree of immunity the circuit has to noise voltages on the DC power lines. The change in output voltage (vO) for a given change in DC power line noise voltage (vN) is computed with Equation (2.23):

where vO, vN, RF, RI, and PSRR are the values of the output noise signal, the noise signal on the DC supply lines, the feedback resistor, the input resistor, and the power supply rejection ratio (PSRR), respectively. The manufacturer’s data sheet in Appendix 1 lists the PSRR as ranging from 30 to 150 microvolts per volt. The worst-case effect on the output voltage for the circuit in Figure 2.12 is then

In other words, the amplitude of the power line noise (vN) will be reduced by a factor of 0.000968. This means, for example, that if the DC supply lines had noise signals of 100 millivolts peak-to-peak, we could anticipate a similar signal in the output with an amplitude of about

2.3.3 Practical Design Techniques

The following design procedures will enable you to design noninverting op amp circuits for many applications. Although certain nonideal considerations are included in the design method, additional nonideal characteristics are described in Chapter 10.

To begin the design process, you must determine the following requirements based on the intended application:

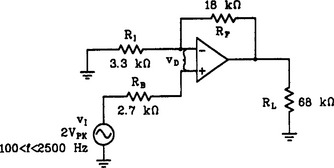

As an example of the design procedure, let us design a noninverting amplifier with the following characteristics:

| 1. Voltage gain | 8 |

| 2. Frequency range | DC to 5 kilohertz |

| 3. Load resistance | 27 kilohms |

| 4. Maximum input voltage | 800 millivolts RMS |

Determine an Initial Value for RI.

There are endless combinations of RF and RI that will produce the desired circuit voltage gain. The smaller the values of RF and RI, the higher the value of feedback current. The feedback current subtracts from the maximum available output current. Thus, we want to avoid extremely small values.

The larger we make RF and RI, the more the circuit operation is affected by certain nonideal characteristics. In general, neither resistor should be less than 1.0 kilohms nor more than 680 kilohms unless there is a compelling reason for them to be so. With this rule of thumb in mind, we select RI as 4.7 kilohms.

Determine the Value of RF.

RF can be computed from the voltage gain equation, Equation (2.28):

For the present design example, we compute RF as follows:

We select the nearest standard value of 33 kilohms to use as RF.

Determine the Required Unity Gain Frequency.

You will recall from our discussions on bandwidth that the error between the calculated or ideal gain and the actual gain increases as frequency increases. We can, however, estimate the required unity gain frequency by applying Equation (2.22).

Thus, we must select an op amp that has minimum unity gain frequency of at least 40.1 kilohertz. Since the 741 has a 1.0-megahertz unity gain frequency, it should be adequate for this application with respect to bandwidth.

Determine the Minimum Supply Voltages.

The minimum supply voltages are computed simply by ensuring that the maximum expected output voltage swing is no greater than the ±VSAT values. The maximum output swing can be found by using the basic equation for voltage gain, Equation (2.1).

In our particular example, the maximum output voltage will be

Notice the multiplying factor 1.414 to convert our input voltage (given in RMS) to a peak or worst-case value. The manufacturer’s data sheet in Appendix 1 indicates that the 741 op amp will produce at least a ±12-volt output swing with a ±15-volt supply voltage and a load resistance of at least 10 kilohms. Thus, we can infer that we have a worst-case internal voltage drop of 15 – 12, or 3 volts. The minimum power supply voltage can be determined with Equation (2.25):

Anything greater than ±12.05 volts for the DC supply will be adequate, so we choose the standard values of ±15 volts for our application. Realize that this is a worst-case calculation; a more typical internal drop would be 2 volts rather than 3 volts.

Determine the Required Slew Rate.

The minimum slew rate for the op amp is computed by transposing Equation (2.11).

Since the slew rate of the 741 exceeds this minimum value, we can continue with our initial op amp selection. If the above calculation indicates a higher requirement than our preliminary op amp selection can deliver, then another op amp must be selected that has a higher slew rate.

Calculate the Value of Compensation Resistor (RB).

The compensation resistor (RB) reduces the error in the output voltage caused by the voltage drops that result from the op amp’s input bias currents. As with the inverting configuration, we achieve maximum error reduction by inserting equal resistances between both op amp input terminals and ground. The resistance between the inverting input to ground is essentially equal to the parallel combination of RI and RF. This is easier to appreciate if you remember that the output impedance of an op amp is very low. For purposes of this analysis, assume that the output impedance is actually 0 ohms. In this condition, one end of both RI and RF connect to ground and the other ends connect to the inverting input terminal. Thus, they are effectively in parallel. The value of RB is calculated as in Equation (2.26):

We will choose a standard value of 4.3 kilohms. The final schematic is shown in Figure 2.14.

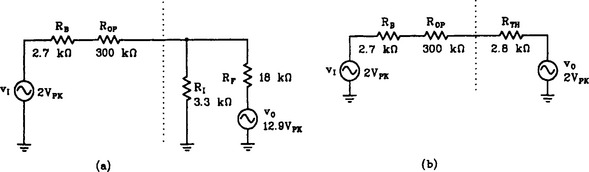

The actual performance of the circuit is indicated by the oscilloscope plots in Figure 2.15. Additionally, Table 2.2 contrasts the measured performance with the original design goals.

TABLE 2.2

| Parameter | Design Goal | Measured Values |

| Voltage gain | 8 | 7.9–8.01 |

| Frequency range | DC–5 kHz | DC–>5 kHz |

FIGURE 2.15 Oscilloscope displays showing the actual performance of the noninverting amplifier shown in Figure 2.14. (Test equipment courtesy of Hewlett-Packard Company.)

A slight phase shift can be seen between input and output waveforms in Figure 2.15. The effect is more pronounced as the input frequency is increased. For many applications, input/output phase relations are not important; in other applications they are critical. Chapter 10 discusses this issue in more detail.

2.4 VOLTAGE FOLLOWER

A voltage follower circuit using an op amp is shown in Figure 2.16. This is a very simple, but very useful, op amp configuration.

If you compare the voltage follower circuit to the noninverting amplifier previously discussed, you will see that RI and RF in the noninverting circuit have become respectively, infinity and 0 to form the follower circuit. Since there is no significant impedance in the path of the (−) input terminal, there is no need for the compensating resistor in the (+) terminal.

The voltage on the (+) input is equal to VI because of the direct connection. Recall that vD is approximately 0 volts as long as the amplifier is not saturated. This means that the (−) input terminal will also be approximately equal to VI. And, since the (−) pin is connected directly to the output, the output must also be equal to vI. Because the output is essentially equal to the input at all times, the voltage gain is unity (i.e., 1). The circuit is called a voltage follower because the output appears to follow or track the input voltage.

So, what is the value of a circuit that gives us an output voltage that is equal to the input? Well, although the voltage gain is only 1, there are other very important reasons for using a voltage follower. One of the most important uses for the circuit is for impedance transformation. By inspection, you can see that the input impedance is very high, as the only current drawn from the source is the bias current for the (+) terminal. The output impedance, on the other hand, is quite low. As with the other configurations previously studied, the output impedance approaches an ideal value of 0, so the voltage follower circuit can interface a high impedance device or circuit to a lower impedance device or circuit. Although very little current is drawn from the source, a substantial current may be supplied to the load.

2.4.2 Numerical Analysis

The numerical analysis for the voltage follower is simpler than for previous circuits because of the lack of circuit complexity. Let us analyze the circuit shown in Figure 2.16 and determine the following values:

For purposes of the following analyses, let us assume that the op amp in Figure 2.16 is a 741.

Voltage Gain.

The ideal voltage gain of a voltage follower circuit is always unity, or 1. This can be further demonstrated by applying the voltage gain equation, Equation (2.28), presented for the noninverting amplifier circuit. Since RF is now 0 and RI is infinity, our calculations become

As with other amplifier configurations, the actual gain of the circuit falls off at high frequencies. This is further discussed, along with bandwidth, in a later section.

Input Impedance.

The input impedance of the voltage follower is ideally infinite because it is essentially the input resistance of the (+) input of the op amp modified by the effects of feedback. The value may be estimated by applying Equation (2.29) with the quantity RI/(RF + RI) considered to be unity. Thus, for low frequencies (i.e., near DC) the circuit in Figure 2.16 will have a minimum input impedance of

If we had used typical values for ROP, we would have gotten an even higher value for ZIN. In any case, the value is so high that we can consider it as infinite for most applications.

Input Current Requirement.

The input current for the circuit in Figure 2.16 is only the bias current for the (+) input terminal. This is ideally 0 and for most applications may be neglected. If more precision is desired, then the manufacturer’s data sheet in Appendix 1 can be referenced. The data sheet indicates that the input bias current will be no higher than 500 nanoamperes, with a more typical value listed as 80 nanoamperes. Even though this current is temperature dependent, the absolute values are so small that they may be neglected in many applications.

Maximum Output Voltage Swing.

The maximum output voltage swing for the follower circuit is determined in the same manner, Equation (2.10), as that used with preceding amplifiers. That is,

If a more accurate value is desired, the manufacturer’s data sheet can be used to find a more precise value for the worst-case saturation voltage.

Slew-Rate Limiting Frequency.

As with the amplifier configurations discussed previously, the highest frequency that can be amplified with a full output voltage swing and no slew-rate limited distortion is computed as in Equation (2.11):

If it is known for certain that the actual output swing will never be required to reach its limits, then the lower actual output swing can be used to compute the slew-rate limiting frequency.

Maximum Input Voltage Swing.

Since the amplifier has a voltage gain of 1, the maximum input voltage swing is equal to the maximum output voltage swing. Thus, in the case of Figure 2.16, we could have an input signal as large as ±13 volts without causing the amplifier to saturate. Again, if you plan to push the amplifier to its limits, you should refer to the manufacturer’s data sheet and select the worst-case output saturation voltage at the worst-case temperature. The computations, however, remain similar.

Output Impedance.

The output impedance of the voltage follower can be computed as follows:

where AOL is the open-loop gain of the op amp at the specified frequency. You can determine the value of AOL at the desired operating frequency as in Equation (2.16):

where fIN is the specific input frequency being considered.

For the circuit in Figure 2.16, the open-loop gain at 5 kilohertz, for example, is

The output impedance then becomes Equation (2.31).

As with most op amp circuits, the output impedance is so low relative to any practical load resistance that its effects may be ignored.

Output Current Capability.

The total current flowing in or out of the output terminal of the op amp in Figure 2.16 may be delivered directly to the load. That is, the feedback current is extremely small and can be disregarded in nearly all cases. As the load resistance varies from infinity (open) to 0 (short), the output current from the op amp varies from 0 to the short-circuit value of 20 milliamps (given in the data sheet). The limiting factor is the amount of reduction that can be tolerated on the output voltage swing.

On an unprotected op amp, the value of load current must be kept below the stated output current rating. If this value is not supplied in the data sheet, it can be estimated by using the maximum power dissipation data; recall that power = voltage × current.

Bandwidth.

The bandwidth (i.e., the upper cutoff frequency) of a voltage follower circuit may be estimated by the following equation:

For the circuit shown in Figure 2.16, we can compute the upper cutoff frequency and/or bandwidth as follows:

At lower frequencies, the voltage gain will be nearly equal to the calculated value of unity. As the frequency approaches the upper cutoff, the voltage gain begins to decrease. Once the input frequency exceeds 1.0 megahertz (for a 741), the overall circuit gain will decrease dramatically.

Power Supply Rejection Ratio.

The change in output voltage (vO) for a given change in DC power line noise voltage (vN) is computed for the voltage follower with the following equation:

where vO, vN, and PSRR are the values of the output noise signal, the noise signal on the DC supply lines, and the power supply rejection ratio, respectively. The manufacturer’s data sheet in Appendix 1 lists the power supply rejection ratio (PSRR) as ranging from 30 to 150 microvolts per volt. The worst-case effect on the output voltage for the circuit in Figure 2.16 is then

In other words, the amplitude of the power line noise (vN) will be reduced by a factor of 0.000150. This means, for example, that if the DC supply lines had noise signals of 100 millivolts peak-to-peak, we could anticipate a similar signal in the output with an amplitude of about

2.4.3 Practical Design Techniques

The design of a voltage follower circuit is fairly straightforward because of the lack of circuit complexity. Let us examine the design procedure by designing a voltage follower with the following characteristics:

| 1. Input voltage range | 100 to 500 millivolts RMS |

| 2. Frequency range | DC to 75 kilohertz |

| 3. Load resistance | 4.7 kilohms |

| 4. Input resistance | greater than 100 kilohms |

| 5. Source impedance | 1.8 kilohms |

Select the Op Amp.

First, we must select an op amp that can provide unity gain up to the maximum input frequency. That means we will need an op amp with a unity gain bandwidth of at least Equation (2.32):

Second, the slew rate of the op amp must be adequate to allow the required output voltage swing at the highest input frequency. The required slew rate is given by Equation (2.11):

Since both the unity gain frequency and the slew rate requirements are within the limits of the 741 (see Appendix 1), let us choose this device for our design.

Select the Power Supply Voltages.

Now we must select a power supply voltage that is high enough to prevent saturation on the highest input voltage. The worst-case internal voltage drop on the output for a 741 is listed as 5 volts in Appendix 1 for load resistances between 2 and 10 kilohms. A more typical value is 2 volts. The minimum required power supply voltage can be determined as in Equation (2.25):

We will choose a more standard value of ±15 volts for our power supply voltages. The complete schematic of our voltage follower circuit is shown in Figure 2.17.

Now let us check to be sure the 741 can supply the required current to our load without causing an appreciable voltage loss in our output. When the output voltage reaches its maximum level, the load current can be computed with Ohm’s Law as

This should have negligible effect on the output voltage of the op amp because the 741 can supply significantly higher currents.

Figure 2.17 also illustrates the use of a compensating resistor RB. Recall from the previous amplifier designs that bias current in the op amp can cause output offsets because of the voltage drops across any resistances in line with the bias current. We minimize this offset by providing equal resistances in both (+) and (−) inputs. The resistance in the (+) input is simply the source resistance that was given as 1.8 kilohms. To minimize output errors, we insert an equal value RB in the feedback loop. Note that no significant signal current flows through RB. Therefore, the voltage gain is unaffected by the addition of RB, and it remains constant at unity.

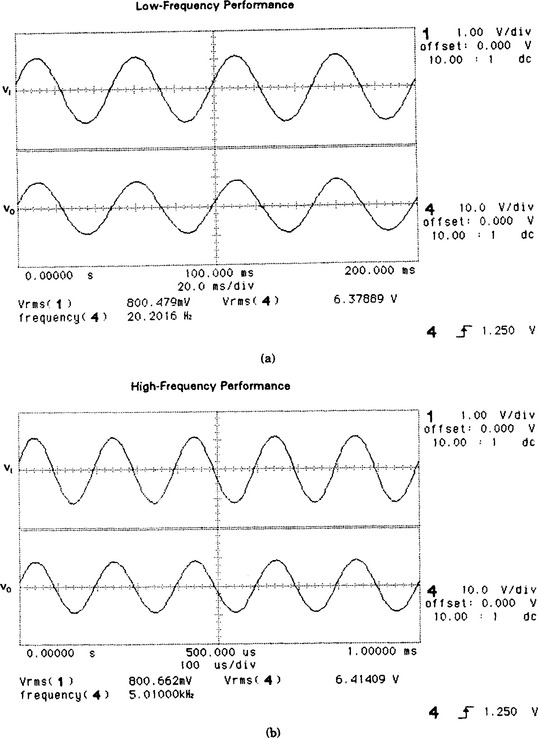

The actual performance of our voltage follower circuit is shown in Figure 2.18 through the use of an oscilloscope plot. The measured performance is compared to the design goals in Table 2.3.

TABLE 2.3

| Parameter | Design Goal | Measured Values |

| Input resistance | >100 kΩ | >100 kΩ |

| Voltage gain | 1.0 | 0.97–0.99 |

| Frequency range | DC–75 kHz | DC–>75 kHz |

FIGURE 2.18 Oscilloscope displays showing the performance of the voltage follower circuit shown in Figure 2.17. (Test equipment courtesy of Hewlett-Packard Company.)

2.5 INVERTING SUMMING AMPLIFIER

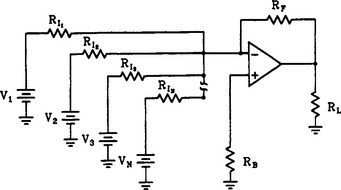

Figure 2.19 shows the schematic diagram for an inverting summing amplifier. The summing amplifier has several inputs—the circuit in Figure 2.19 shows four with the possibility of others indicated. Although the input sources are shown as DC signals (i.e., batteries) the circuit works equally well for AC signals or even a combination of AC and DC signals.

There are several ways to understand the operation of the inverting summing amplifier circuit. One simple method is an application of the Superposition Theorem. In this case, we consider the effects of each input signal one at a time with all other sources being set to 0. We know from our discussion of the basic inverting amplifier that the (−) input terminal is a virtual ground point. That is, unless the amplifier’s output is saturated, the voltage on the (−) input will be within a few microvolts of ground potential. Thus, when we replace all but one source with a short (i.e., set them to 0 volts), the associated input resistors essentially have a ground connection on both ends. In other words, one end of each resistor is connected to ground through the temporary short that we inserted across the battery as part of the application of the Superposition Theorem. The opposite end of each input resistor is connected to the (−) input, which we know is a virtual ground point. As all input resistors but one have ground potential on both sides, there will be no current flow through them and they can be totally disregarded for the remainder of our analysis.

By disregarding all input resistors and sources but one, we are left with a simple single-input inverting amplifier circuit. We already know how this circuit works, so we can now compute voltage gain, input current, output voltage, and so on, for this single input. We can then perform a similar analysis for each of the other inputs one at a time. The actual output voltage of the circuit is the combination or sum of the effects of the individual inputs.

One important point that should be recognized about the circuit shown in Figure 2.19 is that the gains for each input signal are independent. That is, the ratio of RF to RI1 will determine the voltage gain that signal V1 receives. V2, on the other hand, is amplified by a factor established by the ratio of RF and RI2. Thus, we can quickly conclude that the individual gains can be varied by changing the values of the input resistors, while the gains of all signals can be changed simultaneously by varying the value of RF. Consider, for example, that the circuit is being used as a microphone mixer. The signals from several microphones provide the inputs to the circuit. If the individual input resistors are variable, then they adjust the amplitude (i.e., volume) of one microphone relative to another. If the feedback resistor is also variable, it serves as a master volume control because it varies the amplification of all microphone signals but does not change the strength of one relative to another.

Resistor RB is a compensating resistor and ensures that both inputs of the op amp have similar resistances to ground. You will recall that this helps minimize problems caused by the op amp’s bias currents.

2.5.2 Numerical Analysis

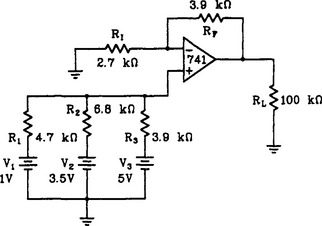

We will now analyze the numerical performance of an inverting summing amplifier circuit. The circuit to be analyzed is shown in Figure 2.20. Compute the following characteristics of the circuit:

1. Voltage gain of each input signal

2. Input impedance of each input signal

3. Input current requirement for each input signal

4. Maximum output voltage swing (total)

Voltage Gain.

The voltage gain for each input signal in Figure 2.20 must be computed separately. Each gain, however, is computed in the same manner, Equation (2.6), as a simple inverting amplifier circuit. That is,

where the minus sign is used to remind us of the phase inversion given to each signal.

The individual voltage gains for the circuit in Figure 2.20 are computed:

Observe that each of these calculations is similar to our analysis on a single-input inverting amplifier and that the gains are independent of each other.

Input Impedance.

The input impedance seen by each input is equal to the value of the input resistor on that particular input. That is, since each input resistor connects to a virtual ground point, its respective source sees it as the total input impedance. No calculations are required to determine the input impedance; we simply inspect the input resistors’ individual values.

Input Current Requirement.

Each source must supply the current for its own input. The amount of current can be determined by Ohm’s Law and is simply the input voltage divided by the input resistance, Equation (2.8). For the circuit shown in Figure 2.20, we can compute the following values:

In the case of V1, a variable DC source, we computed the worst-case input current by using the maximum input voltage (3 volts). Similarly, for the alternating voltage sources v2 and v3, we used peak values of input voltage. In each of these cases, the source must be capable of supplying the required current.

Maximum Output Voltage Swing.

The output voltage of the summing amplifier is limited by the ±VSAT values. For the purposes of this analysis, we will estimate the values of ±VSAT to be 2 volts below the DC power supply values. The calculations, Equation (2.10), to determine the maximum output voltage swing are

As with previous circuits, we can utilize the data sheet supplied by the manufacturer if it becomes necessary to have a more accurate, or perhaps worst-case, value.

Maximum Input Voltage Swing.

The maximum input voltage swing of an amplifier is the voltage that causes the amplifier’s output to reach saturation. Input voltages that exceed this limit will produce distorted (i.e., clipped) output signals. In the case of the summing amplifier, the situation is more complex than with previous, single-input amplifiers. That is, the instantaneous level of output is determined by the instantaneous values of input voltage on all inputs. First we will consider each input separately to determine the maximum levels of an isolated input. The calculations, from Equation (2.1), are similar to those used with previous circuits.

where AV is the voltage gain received by a particular input. The individual calculations are

Note that the negative and positive saturation limits were used as the maximum output “swing” for V1 and V4, respectively, since these two inputs are DC and will only be limited by one saturation barrier.

With reference to v2 and v3, we may want to express them in their peak and RMS forms to better compare them with the signals shown in Figure 2.20. These conversions are

Since the maximum limits on all inputs (both DC and AC) are greater than the values listed on the schematic, we will assume that no single input can cause the amplifier output to saturate. However, two or more input signals may combine at some instant to drive the output to its saturation limit. Let us determine if this situation can occur in the circuit shown in Figure 2.20. To perform this calculation, we want to determine the worst-case combination of input signals. First observe that V1 and V4 are of opposite polarity and thus tend to reduce each other’s effect in the output. A worst case would be when V1 is zero or when V1 is maximum (3 volts DC). Let us evaluate them with Equation (2.1) to determine the worst-case combination.

From these calculations we can see that if V1 were reduced to zero, V4 would produce +1.7 volts in the output. On the other hand, if V1 were set for maximum (3 volts DC), the net output voltage would be the difference between the V1-produced and V4-produced outputs. This worst-case output voltage is simply -7.8 + 1.7, or -6.1 volts.

Now we must consider the effects of the AC signals v2 and v3. The worst-case output condition will occur when these two inputs hit their peak values simultaneously and have the same polarity as V1. The output voltages produced individually by v2 and v3 are

The net effect of V1, v2, v3, and V4 can be found by adding the individual output values (Superposition Theorem).

Since this worst-case value is less than our maximum output voltage limit (±13 volts typically), we should not have a problem. In extreme cases, however, we may have a potential problem. Recall that the output limits of ±13 volts were obtained by using typical performance values for the 741. If worst-case values are used, we will find that the limits fall to ±10 volts under worst-case conditions. If this situation were to occur at the same time our inputs were all at their maximum values, we would drive the amplifier into saturation and produce a clipped output. If this is a serious concern for our particular application, we can reduce RF slightly to prevent the combined signals from driving the output to saturation.

Output Impedance.

The output impedance of the summing amplifier can be estimated as follows:

where AOL is the open-loop gain of the op amp at the specified frequency and Y is computed as follows:

Now let us compute the output impedance for the circuit in Figure 2.20. First we compute the value of the parallel combination of input resistors (RX):

Then we use this value to compute the factor Y, Equation (2.35):

Next we determine the value of AOL at the frequency of interest, using Equation (2.16). We will use the worst-case value that occurs at the highest input frequency (10 kilohertz):

Finally we compute the estimated value of output resistance, from Equation (2.35):

Since this value was computed at the highest input frequency (worst case), and since it is very low compared to the value of the load resistor, its effects on output voltage can be safely ignored.

Output Current Capability.

The maximum value of load current occurs when the output reaches its highest instantaneous value. The maximum voltage was previously computed as 12.2 volts. The worst-case load current can be computed with Ohm’s Law:

The output of the op amp must also supply the feedback current. In most applications, this current can be ignored because it is generally much smaller than the load current. Our present circuit is no exception. That is, we can see by inspection that the feedback path has over 10 times as much resistance as the load.

The data sheet in Appendix 1 indicates that even under worst-case conditions, the output can maintain at least 10 volts across a 2000-ohm load. By Ohm’s Law, we can conclude that this corresponds to an output current of

Of course, the typical value of current is even higher. In any case, the current capability of the output clearly exceeds our requirements and therefore poses no problem. If our load resistor were smaller, we could anticipate a reduced output voltage.

Bandwidth.

For a meaningful discussion on bandwidth, we must consider the response of each input individually. When the responses are considered separately, we can estimate the bandwidth of any given input by applying the bandwidth equation, Equation (2.22), used in previous analyses:

We know from earlier calculations that the bandwidth will decrease as the closed-loop gain is increased. Let us calculate the bandwidth for the input in Figure 2.20 that has the highest gain. We have already determined the individual gains to be 2.6, 10, 2.1, and 1.7 for inputs V1 through V4. We will compute the bandwidth for the v2 input because its gain is the highest. Incidentally, there would be very little point in computing the bandwidth for inputs V1 and V4 because these have DC signals applied. The bandwidth for the v2 input is

A similar analysis could be made for input v3, which has a computed gain of 2.1 and a maximum input frequency of 10 kilohertz. For large amplitude output signals, the slew rate will tend to restrict the operation to even lower frequencies. This is discussed in the following section.

Slew-Rate Limiting Frequency.

As discussed for previous amplifier configurations, the slew rate also limits the highest operating frequency for larger output voltage excursions. The slew-rate limiting frequency is found as follows, Equation (2.11):

Thus, although the v2 input was shown to have a 90.9-kilohertz bandwidth as established by the unity gain frequency, the full-power upper limit is only 6.12 kilohertz. In the given application, however, the applied signal is only 5000 hertz, so this should not hamper the operation of the circuit with respect to the v2 input.

The v3 input, on the other hand, operates at 10 kilohertz. This means that we can never get the full 26-volt swing in the output as a result of v3 signals. The schematic indicates that the highest input voltage is 1.2 volts RMS. The gain for v3 was previously computed as 2.1. The largest normal output swing from v3 can be found by applying Equation (2.1):

The actual slew-rate limiting frequency for this input is then estimated with Equation (2.11) as

In the given circuit, the slew rate should not interfere with the expected operation.

2.5.3 Practical Design Techniques

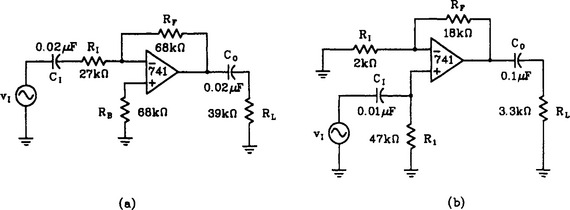

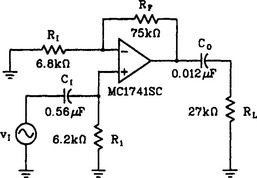

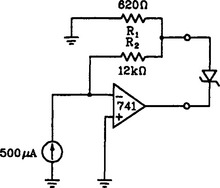

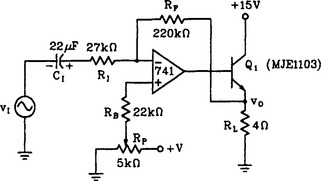

To illustrate the design method for an inverting summing amplifier circuit, let us design a 3-input circuit with the following performance characteristics: