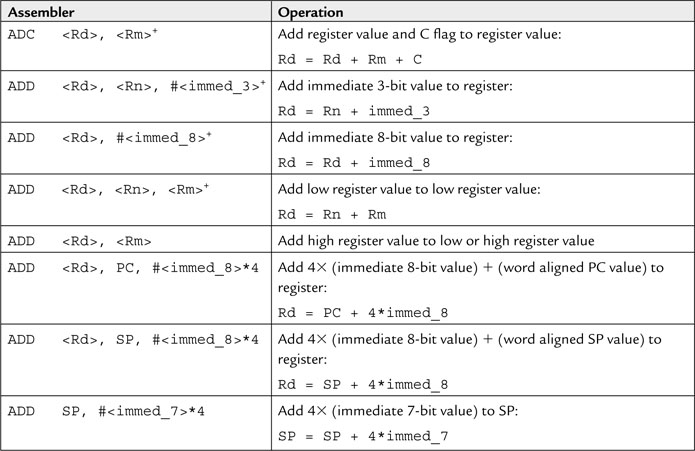

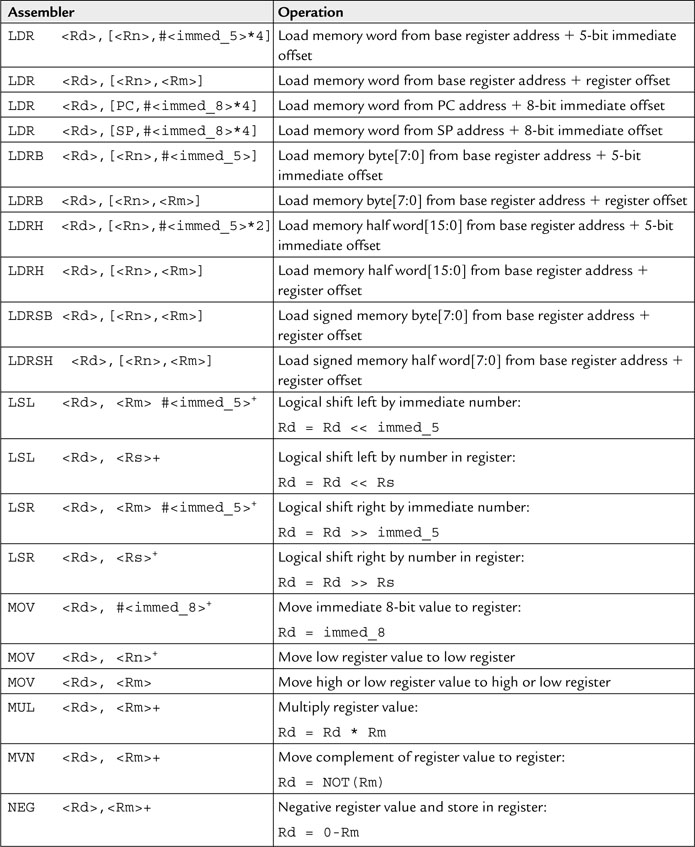

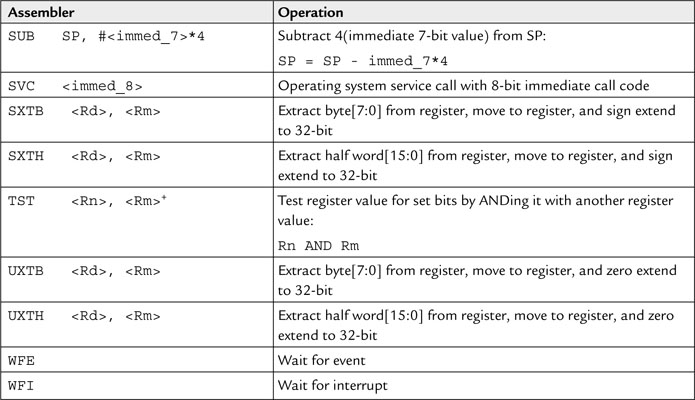

APPENDIX A Cortex-M3 Instructions Summary

This material is reproduced from the Cortex-M3 Technical Reference Manual with permission from ARM Limited. Instructions marked with a plus sign (+) indicate that the flag (APSR) gets updated.

Supported 16-Bit Thumb Instructions

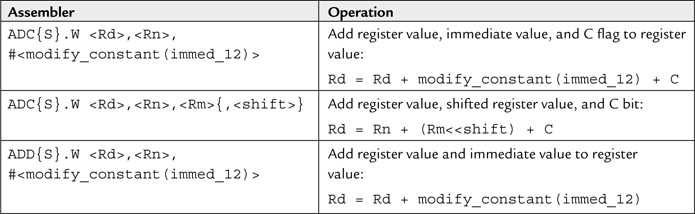

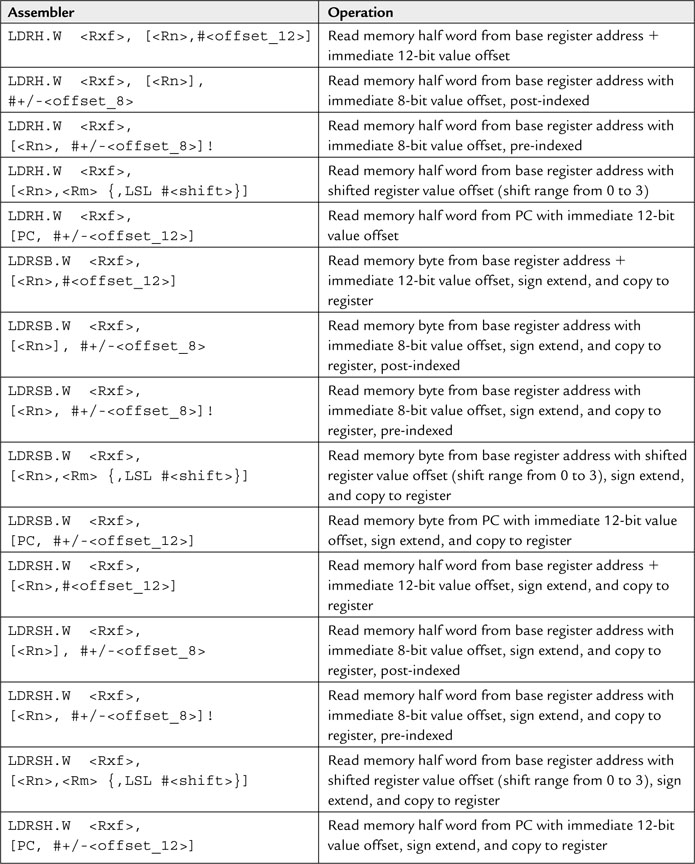

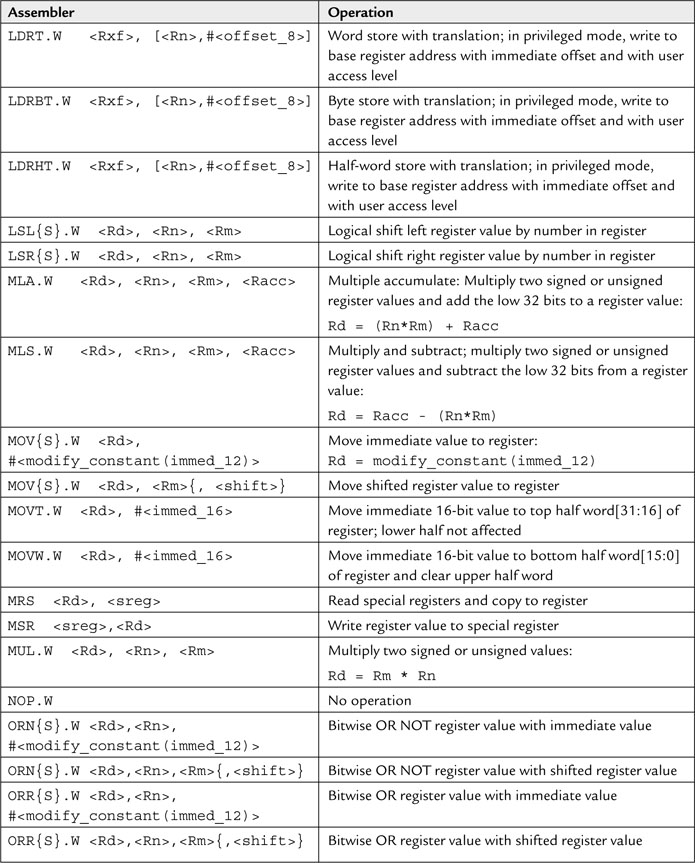

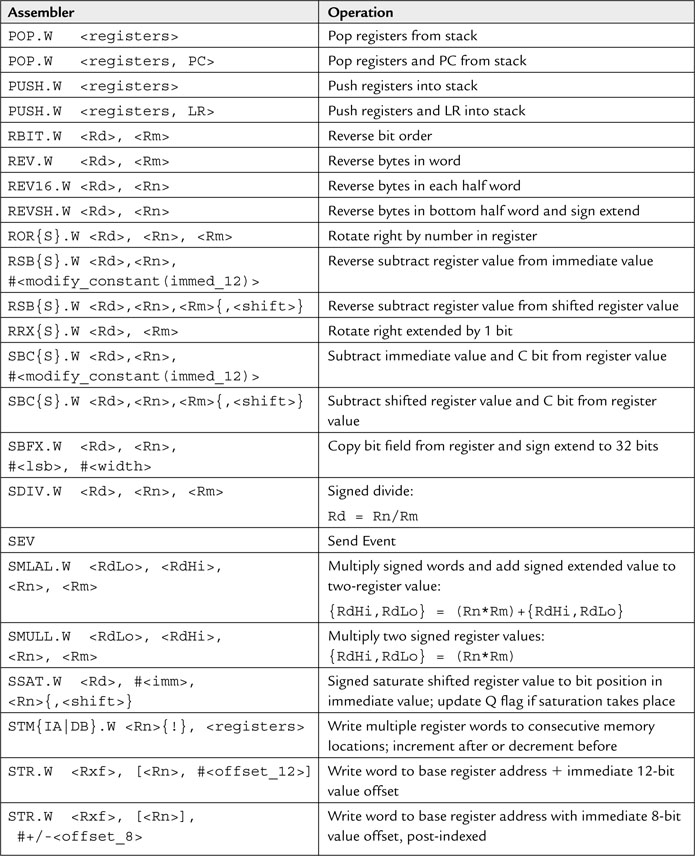

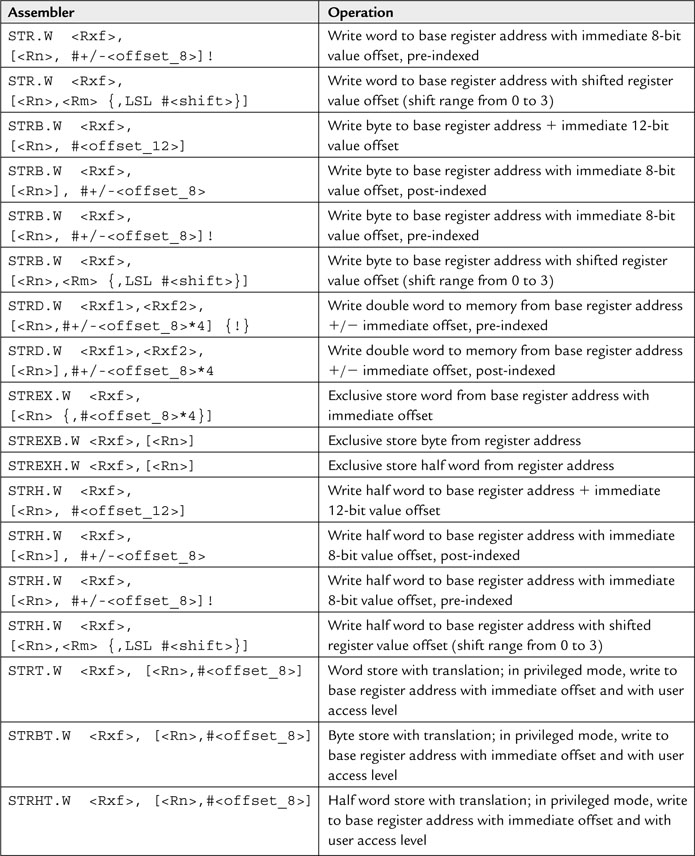

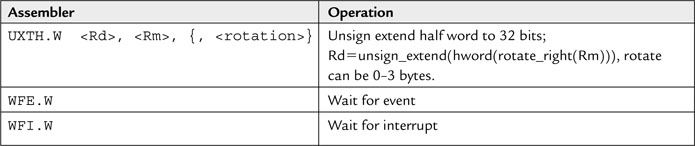

Supported 32-Bit Thumb-2 Instructions

Instructions with {S} update flags (APSR) only if the S suffix is used. Instructions marked with a plus sign (+) indicate that the flag (APSR) gets updated.

Note: To support immediate data of commonly required value ranges, many Thumb-2 instructions use an immediate data-encoding scheme, labeled modify_constant in Table A.2. The details of this encoding scheme are documented in the ARM Architecture Application Level Reference Manual, Section A5.2, “Immediate Constants.”

..................Content has been hidden....................

You can't read the all page of ebook, please click here login for view all page.