. . . the uniformity of the world, that everything which happens is connected, that the great and the small things are all encompassed by the same forces of time . . . this unity and necessary sequence of all things is nevertheless broken in one place, through a small gap, this world of unity is invaded by something alien, something new . . .

This chapter takes a look at Digital Signal Processors , or DSPs, which are special-purpose processors designed for executing mathematically intensive algorithms. They first appeared in the early 1980s and since then have expanded into a wide range of devices used in a variety of applications. These processors are characterized by their ability to quickly move data in and out of memory (or a peripheral), and their architectures are optimized for mathematical processing of that data.

The basic purpose of a DSP is to rapidly read in some data, perform a

complex algorithm on it, then move the result out. Many DSPs have

dual data spaces, known as X and

Y. They are able to access both data spaces

simultaneously, retrieving two operands at once for processing. As

well, many DSPs are also Harvard architecture, and so have three

separate address spaces, one for code and two for data, all of which

can be accessed concurrently. That ability, combined with very

sophisticated ALUs, gives DSPs their advanced data-processing

prowess.

DSPs are commonly used in audio processing, video or image processing, communications, radar and sonar systems, and biomedical applications. Your cell phone has a DSP in it. So does your DVD player and the surround-sound (AV) amplifier in your home theater system. The so-called bionic ear, made by Cochlear, uses a DSP.

Some example applications of DSPs are:

Engine control and antiskid brakes in cars

Digital radios and TVs

DVD players and home theater systems

Music synthesizers

GPS navigation

Radar and sonar processing

Aircraft navigation and guidance, spacecraft avionics, missile guidance systems

Industrial motor control

Robotics

Virtual-reality systems

Image processing, compression, and enhancement

Pattern recognition and machine vision

Adaptive filtering, Fast Fourier Transforms (FFTs), Hilbert transforms

Scientific data processing

Medical diagnostic equipment, ultrasound, and medical imaging systems

Cell phones, pagers, modems, cell phone base stations, digital fax machines

Data encryption

Digital PABXs, ADSL

Echo cancellation

Spread-spectrum processing in communications

Videoconferencing systems

Speaker verification

Speech enhancement and recognition

Speech synthesis and coding

Voice mail systems

And that’s just for starters.

The three big manufacturers of DSPs are Texas Instruments (http://www.ti.com) with the TMS320 series, Analog Devices (http://www.analogdevices.com) with the 21xx and SHARC (21xxx) processors, and Motorola (http://e-www.motorola.com) with the DSP56xxx processors and the high-end MSC8100 StarCore processors designed for communications and network processing. Many other manufacturers are starting to add DSP functionality into their embedded controllers. An example of this is the dsPIC processor by Microchip (http://www.microchip.com).

TI’s DSPs range from small, low-cost units to supercomputers on a chip. The TMS320C6000 series makes your average PC look like a rusty abacus in comparison. They are 128-bit VLIW (Very Long Instruction Word) processors and can execute up to eight instructions every clock cycle. They can run at up to 2000MIPS and 900MFLOPS, and TI is working to make them even faster. These are processors designed for serious number crunching. (And if you want to play with one, you’ll need serious dollars.)

Both the TI and Analog Devices DSPs are designed for use as building blocks in parallel DSP computers. The Analog Devices SHARC supports both message-passing MIMD and shared-memory MIMD in the one machine. You can have six SHARCs as a shared-memory parallel computing node, and you can have six of these nodes message passing with one another. When you consider that each SHARC has more processing power than a CRAY-1 supercomputer, well, let’s just say that a parallel SHARC machine is an awful lot of grunt sitting on your desk. (Before you get too excited, we won’t be designing a machine like that. It’s far too complex and far too expensive for you to consider and well and truly out of the context of this book!)

The Motorola DSP56000 models are 24-bit processors, primarily intended for audio applications, although they are used in other fields as well. The 24-bit architecture is specifically chosen because 24 bits is a common word size in audio processing. Cochlear uses a DSP56000 in its bionic ear.

Now, although DSPs are beautiful in their intended applications of signal processing, they’re also pretty good in general control applications too. An embedded system with a DSP is able to execute sophisticated software and perform advanced algorithms far more efficiently than a conventional processor. Early implementations of embedded DSP systems tended to use the DSP for data processing and include a microcontroller for its ubiquitous functionality. While DSPs are ideal for number crunching, they just weren’t particularly good at conventional processor stuff. Having two processors in the one system is not the most efficient design, and so the logical step was a hybrid processor, combining a DSP core with microcontroller functionality.

To this end, the makers of DSPs have developed variants of their DSP architectures specifically intended for embedded applications. They incorporate a DSP core with the type of subsystems normally found in microcontrollers, such as UARTs, SPI, ADCs, and so on. Their instruction sets are also a mixture, incorporating both DSP (data movement and arithmetic) instructions and conventional microprocessor instructions. They are ideal for such applications as motor control (especially in robotics), neural networks and fuzzy control, data compression, digital communications, digital cameras, or any application that is mathematically intensive yet requires small (and relatively cheap) hardware.

In this chapter, we’re going to look at the Motorola DSP56800 series of DSP controllers and specifically the DSP56805 processor. We’ll see how you design and build a computer based on this chip. DSP56800 processors are specifically designed for implementing advanced digital control and processing in small-scale and low-cost embedded systems. TI and Analog Devices produce comparable processors, and while their architectures may vary, the basic techniques involved in building a computer based upon them are fundamentally the same.

Unlike the conventional DSP56000 with its 24-bit architecture, the DSP56800s have a 16-bit architecture better suited to small-scale control applications. They are fixed point (integer) only, which is fine for most control applications. If necessary, floating point arithmetic can be synthesized in software.

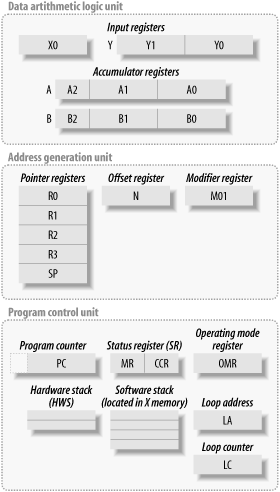

The architecture is based upon four functional units, each with its

own registers, operating independently and in parallel with the other

units. These functional units are the Program

Controller

, which is responsible for software

execution; the Address Generation Unit

(AGU), which handles bus accesses; the

Data ALU, which performs the arithmetic

operations; and the Bit-Manipulation Unit for

efficient and rapid bit-based operations.

The independent operation of these units allows for very efficient and fast software execution. While the Data ALU or Bit-Manipulation unit is performing an operation specified by an instruction, the AGU can be generating addresses for the execution of another instruction, while the program controller can be fetching yet another instruction for execution. The instruction set directly supports this parallelism. To accomplish this high internal throughput, the processor has not one, but three internal address buses and four internal data buses (three data buses for the core and one for peripherals). Two operands may be sourced from the internal memory and operated upon in a single instruction. The result is that the architecture achieves a throughput of 40MIPS on an 80MHz clock. That’s RISC-like performance with a CISC-like instruction set. In other words, that’s a lot of punch.

There’s more. It has hardware looping using the

DO and REP instructions.

DO allows you to specify a block of code (of any

size) and have the processor execute it as a loop in hardware. You

don’t need a counter test and conditional branch

instruction at each iteration, saving processor execution overhead.

REP allows the repetition of a single instruction

and REPs can be nested inside

DO loops. As such, you have very versatile looping

capability with no overhead. Loops on a DSP are fast!

The programmer’s model for the DSP56800 core is shown in Figure 8-1.

The processor has two 36-bit accumulators, a 16x16-bit

Multiply and

Accumulate

(MAC)

unit and a 16-bit barrel shifter. The MAC allows

you to multiply two numbers and then add the result to a growing

total, all with a single instruction. MACs allow for efficient

execution of many signal-processing algorithms, as well as

neuro-fuzzy code. The barrel shifter allows you to shift up to 16

bits in either direction in a single cycle. So, if you want to shift

an operand 15 bits to the left, a conventional processor would

require 15 separate shift-left instructions (or one shift-left, a

loop, a counter variable, and a conditional test for the loop). The

DSP56800, like many DSPs, can perform this operation in just one

cycle.

In short, the DSP56800 has very tight and efficient code with high functionality that it executes exceptionally quickly. It is a fast processor around which you can easily design a powerful embedded computer system.

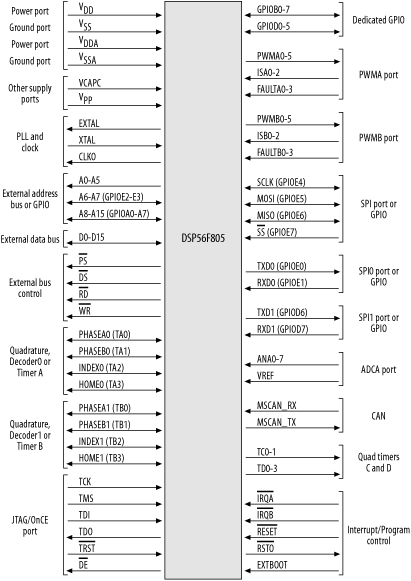

We’ll look at how you design a system based upon the DSP56805 processor, a member of the DSP56800 family specifically designed for industrial control. The DSP56805 has an internal 1K program RAM, 4K of bootstrap ROM (for loading boot software from an external memory or peripheral), 63K of program flash, 8K of data flash, and 4K of data RAM. The processors also have external data and address buses, so the processor’s memory can be expanded well beyond its internal resources. It has a 64K x 16-bit address space, giving access to 128K (bytes) of external memory. (Some DSP568xx processors have significantly larger address spaces than this.) The DSP5685x series can support up to 2M of program memory and up to 8M of data memory. The DSP56800 processors also provide the ability to separate data and program spaces, thereby doubling the external address space. The processor also has a programmable wait-state generator, simplifying interfacing to external devices. The generator may be programmed to provide 0, 4, 8, or 12 wait states for accesses to a given device.

DSP56800s in general come with a range of built-in peripherals, including SPI ports (sometimes two), several 16-bit general-purpose timers, a watchdog timer (called a Computer Operating Properly, or COP, timer by Motorola), a timer for real-time operation, a Synchronous Serial Interface (SSI) for accessing audio codecs (combined ADCs and DACs) and other DSPs, and general-purpose I/O lines. The DSP56805 adds two six-channel Pulse Width Modulation (PWM) units (Chapter 12) for motor control and other uses, two four-channel ADCs at a resolution of 12 bits per channel, and two quadrature decoders for measuring motor positions (covered in Chapter 12). It also has a CAN networking module (discussed in Chapter 11), two serial ports (called Serial Communication Interfaces, or SCIs, by Motorola), and 14 dedicated and 18 shared I/O lines.

The processors operate from a supply voltage of between 3.0V and 3.6V but have 5V-tolerant inputs, making interfacing to a wide variety of devices easy. (Other DSP56800s may operate on a supply voltage of between 4.57V and 5.5V, depending on the particular chip.) The processor has several low-power and sleep modes, making it ideal for battery-powered systems.

All DSP56800 processors incorporate a JTAG (Joint Test Action Group) port for interfacing to specialized debugging instruments. The JTAG port also allows direct access to the processor’s onboard flash program memory, making the job of downloading new code simple and fast.

Tip

The JTAG port allows for real-time debugging of hardware and

software. It allows you to single-step or multi-step through code

running directly on the target system. You can individually (and

manually) toggle signal lines of the processor to test external

subsystems in the computer (also known as boundary

scan). You can set breakpoints both at locations in code

or for when a particular address (or device) is accessed. The JTAG

port allows you to examine and modify registers and memory locations.

To utilize the JTAG interface, you need to have support tools that

are JTAG compliant. For more information, refer to IEEE

standard 1149.1a.

A block diagram of the DSP56805 is shown in Figure 8-2.

All in all, quite a nice processor. So, let’s look at how you build a system based upon one. For simplicity, I’ll look at each subsystem in turn.