6

Conclusions Part I

In Chapter 2 models of metastability in a latch are described which enable an estimate of the MTBF of a synchronizer to be made

and the shape of a typical histogram of events against synchronization time to be predicted,

Refinements to the model also allow effects in the deterministic region, and after the back edge of the clock to be estimated.

Chapter 3 describes metastability in simple NAND gate latch circuits, how the nonstandard levels characteristic of metastability can be filtered out, and the design of commonly used synchronizer flip-flops such as the Jamb latch. Versions of the Jamb latch can be designed which show better performance, or are more robust towards supply voltage, process and temperature variation. Circuits useful in asynchronous situations, where metastability may also occur, are the MUTEX and the Q-flop.

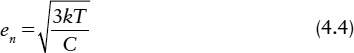

In Chapter 4 the noise level in a latch is shown both theoretically and experimentally to be approximately:

In a normal system where the probability of all time differences between data and clock signals is constant, noise has little effect on synchronization times, however in the case of a malicious input, it reduces the probability of very long metastability so that adding only a relatively small additional time can return reliability to acceptable levels, in this case:

Simulation provides a reliable guide to the nondeterministic part of the MTBF curve, but unless it is augmented by other methods, as in Sections 5.1.2 and 5.1.3 it is insufficiently accurate to predict long term MTBF. The actual reliability of a synchronizer can only be established by measurement of on chip circuits. In Chapter 5 the two-oscillator method provides a simple means to establish the parameters τ and Tw characteristic of synchronizers. Practical measurement schemes include the late transient detector, and the delay-based measurement method.

For measurement in the region of deep metastability where synchronizers normally operate a delay locked loop is necessary to provide sufficient inputs close to the balance point. Difficulties in measuring the distribution of input times in the presence of picosecond level noise in the measuring equipment can be overcome by the technique of measuring the shift in the input distribution as a function of the proportion of high and low outputs. Limitations in the repetition rate of the measuring equipment can reduce the rate of collection of useful output data to as little as 1 data point collected in 1000 generated. This can be overcome by generating only events in the region of interest (deep metastability) so that the repetition rate required is low and normal propagation time events do not obscure the others. Thus a total of seven orders of magnitude improvement over conventional methods of measuring metastability is possible using the methods described.

Measurement of on-chip values for τ can be a valuable tool for optimizing performance or minimizing variability since it is possible to select the best performing circuit from a number, thereby reducing the effects of the variation.

Synchronization and Arbitration in Digital Systems D. Kinniment

© 2007 John Wiley & Sons, Ltd