APPENDIX B. The 16-Bit Thumb Instructions and Architecture Versions

by Joseph Yiu

The Definitive Guide to the ARM Cortex-M3, 2nd Edition

APPENDIX B. The 16-Bit Thumb Instructions and Architecture Versions

by Joseph Yiu

The Definitive Guide to the ARM Cortex-M3, 2nd Edition

- Cover image

- Title page

- Table of Contents

- Copyright

- Foreword

- Foreword

- Preface

- Conventions

- Terms and Abbreviations

- CHAPTER 1. Introduction

- CHAPTER 2. Overview of the Cortex-M3

- CHAPTER 3. Cortex-M3 Basics

- CHAPTER 4. Instruction Sets

- CHAPTER 5. Memory Systems

- CHAPTER 6. Cortex-M3 Implementation Overview

- CHAPTER 7. Exceptions

- CHAPTER 8. The Nested Vectored Interrupt Controller and Interrupt Control

- CHAPTER 9. Interrupt Behavior

- CHAPTER 10. Cortex-M3 Programming

- CHAPTER 11. Exception Programming

- CHAPTER 12. Advanced Programming Features and System Behavior

- CHAPTER 13. The Memory Protection Unit

- CHAPTER 14. Other Cortex-M3 Features

- CHAPTER 15. Debug Architecture

- CHAPTER 16. Debugging Components

- CHAPTER 17. Getting Started with the Cortex-M3 Processor

- Publisher Summary

- 17.1 Choosing a Cortex-M3 Product

- 17.2 Development Tools

- 17.3 Differences between the Cortex-M3 Revision 0 and Revision 1

- 17.4 Differences between the Cortex-M3 Revision 1 and Revision 2

- 17.5 Benefits and Effects of the Revision 2 New Features

- 17.6 Differences between the Cortex-M3 and Cortex-M0

- CHAPTER 18. Porting Applications from the ARM7 to the Cortex-M3

- CHAPTER 19. Starting Cortex-M3 Development Using the GNU Tool Chain

- CHAPTER 20. Getting Started with the Keil RealView Microcontroller Development Kit

- Publisher Summary

- 20.1 Overview

- 20.2 Getting Started with μVision

- 20.3 Outputting the “Hello World” Message Via Universal Asynchronous Receiver/Transmitter

- 20.4 Testing the Software

- 20.5 Using the Debugger

- 20.6 The Instruction Set Simulator

- 20.7 Modifying the Vector Table

- 20.8 Stopwatch Example with Interrupts with CMSIS

- 20.9 Porting Existing Applications to Use CMSIS

- CHAPTER 21. Programming the Cortex-M3 Microcontrollers in NI LabVIEW

- APPENDIX A. The Cortex-M3 Instruction Set, Reference Material

- APPENDIX B. The 16-Bit Thumb Instructions and Architecture Versions

- APPENDIX C. Cortex-M3 Exceptions Quick Reference

- APPENDIX D. Nested Vectored Interrupt Controller and System Control Block Registers Quick Reference

- APPENDIX E. Cortex-M3 Troubleshooting Guide

- APPENDIX F. Example Linker Script for CodeSourcery G++

- APPENDIX G. CMSIS Core Access Functions Reference

- APPENDIX H. Connectors for Debug and Tracers

- References

- Index

The 16-Bit Thumb Instructions and Architecture Versions

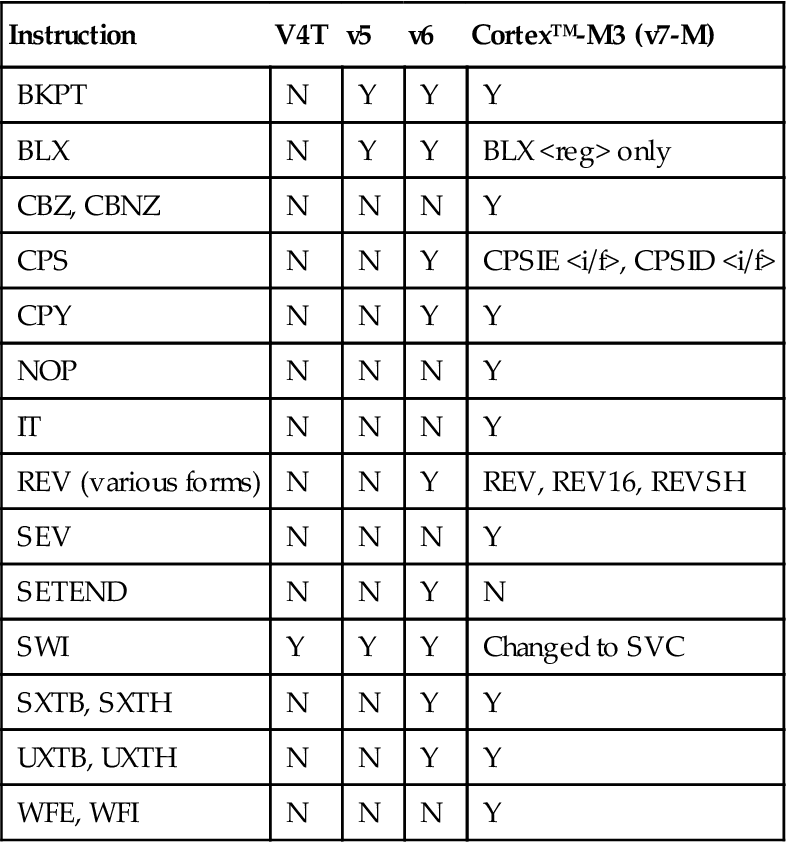

Most of the 16-bit Thumb® instructions are available in architecture v4T (ARM7TDMI). However, a number of them are added in architecture v5, v6, and v7. Table B.1 lists these instructions.

Table B.1

Change of 16-bit Instruction Support in Various Recent ARM Architecture Versions

| Instruction | V4T | v5 | v6 | Cortex™-M3 (v7-M) |

| BKPT | N | Y | Y | Y |

| BLX | N | Y | Y | BLX <reg> only |

| CBZ, CBNZ | N | N | N | Y |

| CPS | N | N | Y | CPSIE <i/f>, CPSID <i/f> |

| CPY | N | N | Y | Y |

| NOP | N | N | N | Y |

| IT | N | N | N | Y |

| REV (various forms) | N | N | Y | REV, REV16, REVSH |

| SEV | N | N | N | Y |

| SETEND | N | N | Y | N |

| SWI | Y | Y | Y | Changed to SVC |

| SXTB, SXTH | N | N | Y | Y |

| UXTB, UXTH | N | N | Y | Y |

| WFE, WFI | N | N | N | Y |

-

No Comment

..................Content has been hidden....................

You can't read the all page of ebook, please click here login for view all page.