16.3 DATA BUFFERING REQUIREMENTS

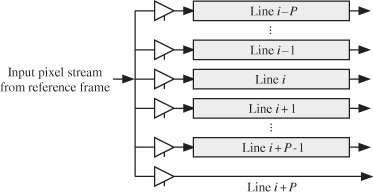

Due to the raster scan nature of the arriving frames, buffering will always be required whether to store incoming lines or to store intermediate results. Thus, no matter which approach is taken, output latency will always be encountered. We choose to buffer incoming data since this will result in separation of major buffer and hardware processing space. This will also limit the amount of chip I/O since all intermediate data will be fed directly to neighboring processing elements (PEs) without having to access distant memory modules. Figure 16.2 shows a shift-register buffer arrangement to simultaneously access all the 2P + 1 pixels of the search area that lie in one column (fixed i). Each shift-register buffer accepts incoming data through a tristate buffer that is controlled by the select signal from the system controller. The number of shift-register buffers required will be 2P only. The length of each shift register is equal to the frame width W.

Figure 16.2 Shift-register buffer arrangement to simultaneously access all 2P + 1 pixels of the search area that lie on one column.

A similar arrangement could be employed for the current frame to simultaneously obtain all the pixels of the current block that lie on one column. The number of shift-register buffers required in that case will be B − 1 only.