Static Induction Devices

Bogdan M. Wilamowski Auburn University, Auburn, AL, United States

Abstract

Several devices from the static induction family such as static induction transistor, static induction diode, static induction thyristor, lateral punch-through transistor, static induction transistor logic, static induction MOS transistor, and space charge limiting load are described. The theory of operation of static induction devices is given for both a current controlled by a potential barrier and a current controlled by space charge. The new concept of a punch-through emitter, which operates with majority carrier transport, is presented.

Keywords:

Junction field effect transistor; Lateral punch-through transistor; Transconductance; Static induction; Classical thyristor; Silicon control rectifier; Power MOS; Space charge; Gate turn off

4.1 Introduction

Static induction devices were invented in 1975 by Nishizawa [1], and for many years, Japan was the only country where static induction family devices were successfully fabricated. Static induction transistor (SIT) can be considered as a short channel junction field effect transistor (JFET) device operating in prepunch-through region. The number of devices in this family is growing with time. The SIT can operate with the power over 100 kW at 100 kHz and above 150 W at 3 GHz [2]. These devices may operate up to THz frequencies [3,4]. Static induction transistor logic (SITL) had 100 times smaller switching energy than its I2L competitor [5,6]. Static induction thyristor has many advantages over the traditional silicon-controlled rectifier (SCR), and static induction diod (SID) exhibits high switching speed, large reverse voltage, and low forward voltage drops [7].

4.2 Theory of Static Induction Devices

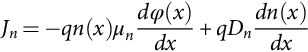

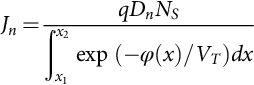

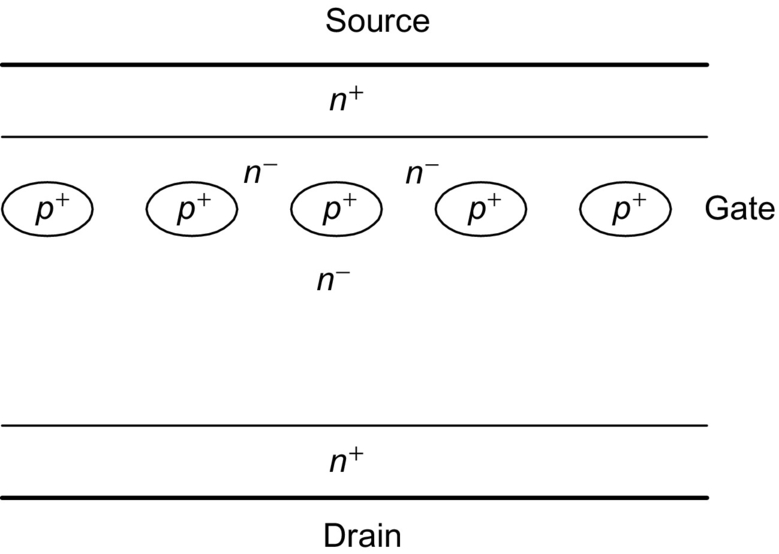

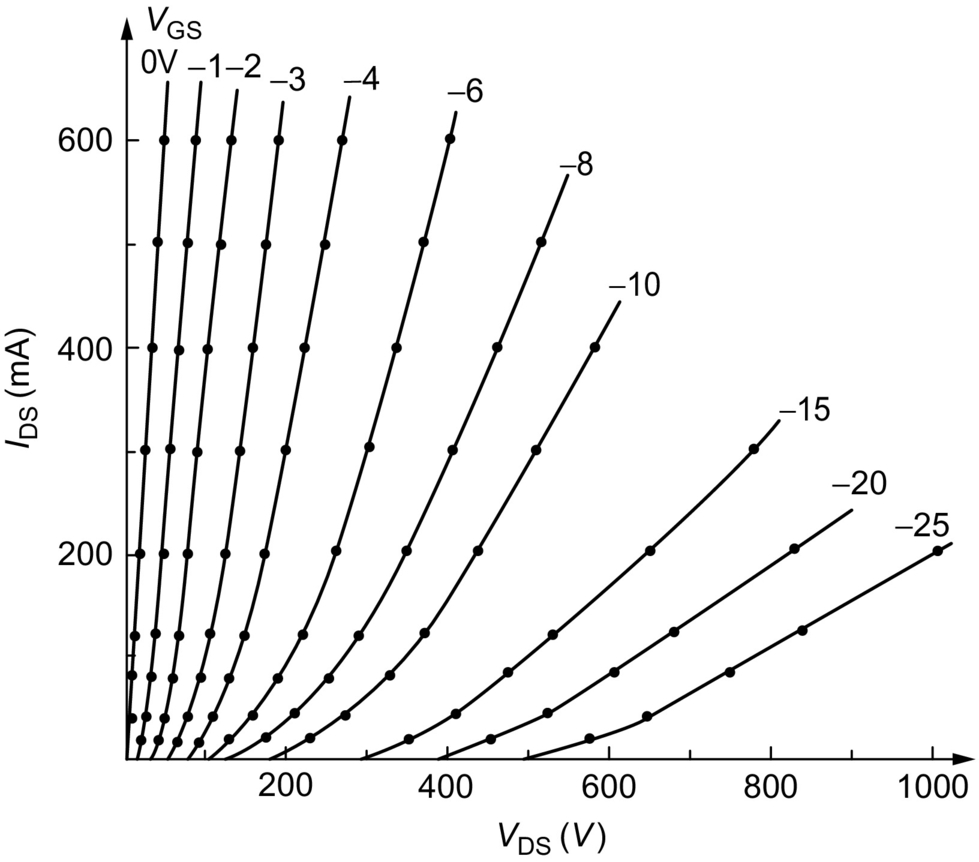

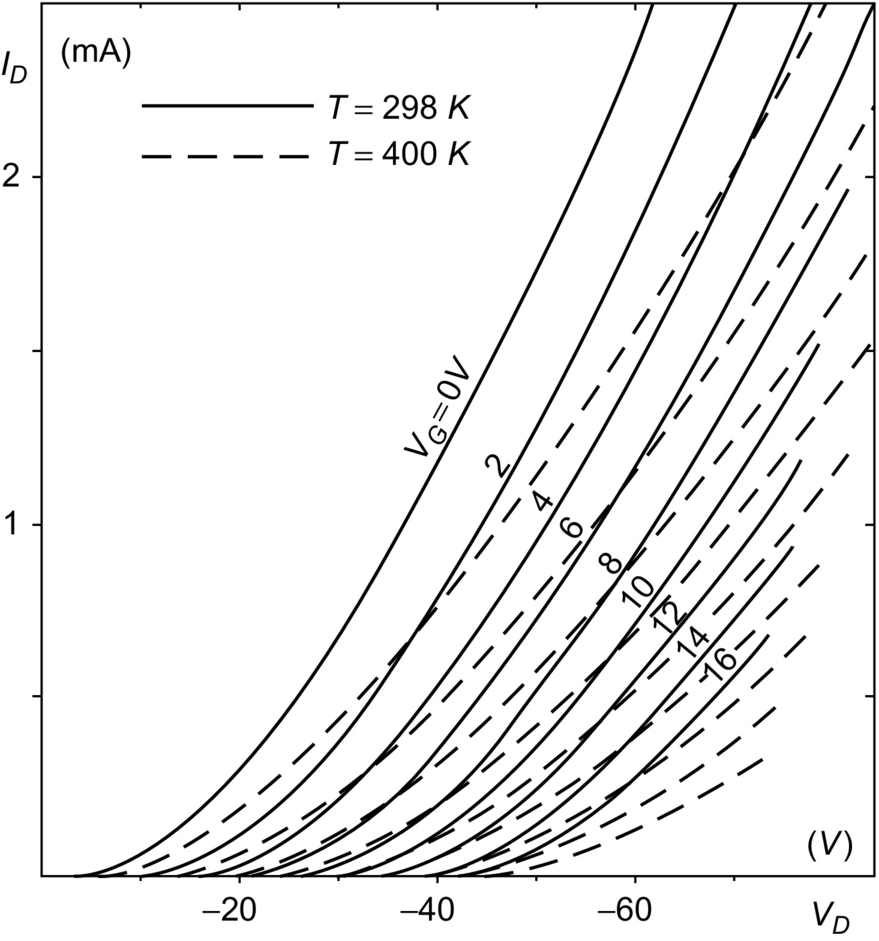

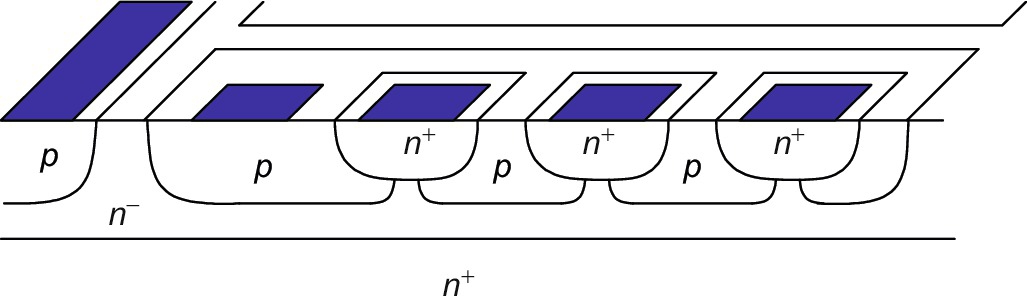

The cross section of the SIT is shown in Fig. 4.1, while its characteristics are shown in Fig. 4.2. An induced electrostatically potential barrier controls the current in static induction devices. The derivations of formulas will be done for an n-channel device, but the obtained results, with a little modification, can also be applied to p-channel devices. For a small electric field existing in the vicinity of the potential barrier, the drift and diffusion current can be approximated by

where Dn=μnVT and VT=kT/q. By multiplying both sides of the equation by exp (−φ (x)/VT) and rearranging

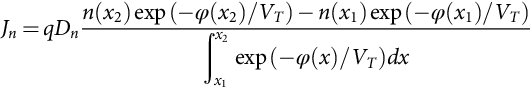

Integrating from x1 to x2, one can obtain

With the following boundary conditions

Eq. (4.3) reduces to

Note that the above equations derived for SIT can also be used to find current in any devices controlled by a potential barrier, such as a bipolar transistor, an MOS transistor operation in subthreshold mode, or a Schottky diode.

4.3 Characteristics of SIT

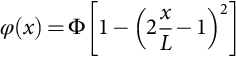

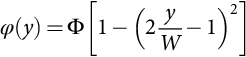

Samples of the potential distribution in the SI devices are shown in Fig. 4.3 [7]. The vicinity of the potential barrier can be approximated using parabolic formulas (Fig. 4.4) along and across the channel [8,9].

Integrating Eq. (4.5) first along the channel and then across the channel yields a very simple formula for drain currents in n-channel SITs:

where Φ is the potential barrier height in reference to the source potential, NS is the electron concentration at the source, W/L ratio describes the shape of the potential saddle in vicinity of the barrier, and Z is the length of the source strip.

Since barrier height Φ can be a linear function of gate and drain voltages, therefore,

The above equation describes characteristics of SIT for small current range. For large current levels, the device current is controlled by the space charge of moving carriers. In the one-dimensional case, the potential distribution is described by the Poisson equation:

where A is the effective device cross section and v(x) is carrier velocity. For a small electric field, v(x)=μE(x), and the solution of Eq. (4.10) is

and for a large electric field, v(x)=const, and Eq. (4.10) results in

where L is the channel length and vsat≈1011 μm/s is the carrier saturation velocity. In practical devices, the current-voltage relationship is described by an exponential relationship, Eq. (4.9); for small currents, a quadratic relationship, Eq. (4.11); and finally for large voltages by an almost linear relationship, Eq. (4.12). SIT characteristics drawn in linear and logarithmic scales are shown in Figs. 4.5 and 4.6, respectively.

4.4 Bipolar Mode Operation of SI devices (BSIT)

The bipolar mode of operation of SIT was first reported in 1976 by Nishizawa and Wilamowski [5,6]. Several complex theories for the bipolar mode of operation were developed [10–14], but actually, the simple formula given by Eq. (4.5) works well not only for the typical mode of the SIT operation but also for the bipolar mode of the SIT operation. Furthermore, the same formula works very well for the classical bipolar transistors. Typical characteristics of the SI transistor operating in normal and in bipolar modes are shown in Figs. 4.7 and 4.8.

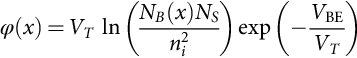

A potential barrier controls the current in the SIT, and it is given by

where ϕ(x) is the profile of the potential barrier along the channel.

For example, in the case of npn bipolar transistors, the potential distribution across the base in reference to emitter potential at the reference impurity level NE=NS is described by

After inserting Eq. (4.14) into Eq. (4.13), one can obtain the well-known equation for electron current injected into the base:

If Eq. (4.13) is valid for SIT and BJT, then one may assume that it is also valid for the bipolar mode of operation of the SIT transistor. This is a well-known equation for the collector current in the bipolar transistor, but this time, it was derived using the concept of the current flow through the potential barrier.

4.5 Emitters for Static Induction Devices

One of the disadvantages of the SIT is the relatively flat shape of the potential barrier (Fig. 4.9A). This leads to slow, diffusion-based transport of carriers in the vicinity of the potential barrier. The carrier transit time can be estimated using the formula

where leff is the effective length of the channel and D=μVT is the diffusion constant. In the case of a traditional SIT transistor, this channel length is about 2 μm, while in the case of SIT transistors with sharper barriers (Fig. 4.9B), the channel length is reduced to about 0.2 μm. The corresponding transient times are 2 ns and 20 ps, respectively.

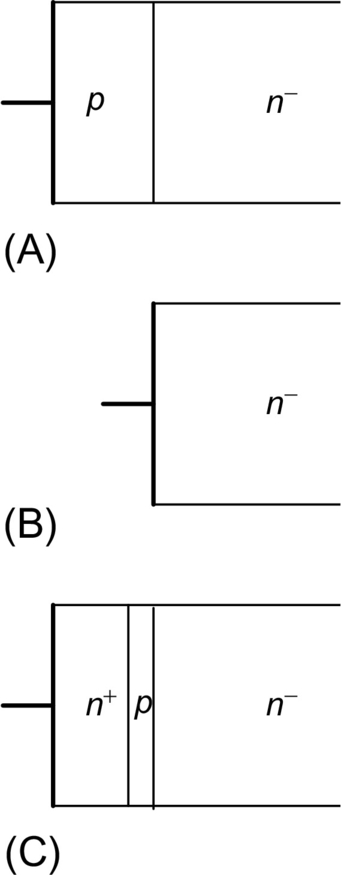

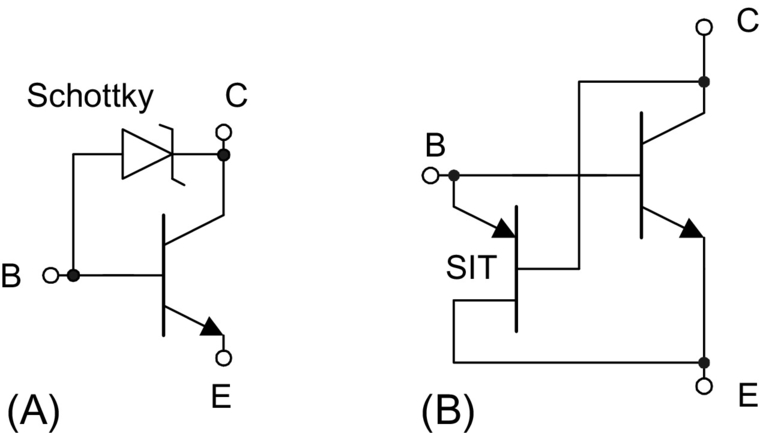

Potential distributions shown in Fig. 4.3 are valid for SIT with an emitter made of a traditional p-n junction. A much narrower potential barrier can be obtained when the other type of emitter is being used. There are two well-known emitters, (1) p-n junction (Fig. 4.10A) and (2) Schottky junction (Fig. 4.10B). For silicon devices, p-n junctions have a forward voltage drop of 0.7–0.8 V, while Schottky emitters have 0.2–0.3 V only. Since the Schottky diode is a majority carrier device, the carrier storage effect is negligible.

Another interesting emitter structure is shown in Fig. 4.10C. This emitter has all the advantages of the Schottky diode, with majority carrier injection, even though it is fabricated out of p-n junctions.

The concept of static induction devices can be used independently of the type of emitter shown in Fig. 4.10. With Schottky-type and punch-through-type emitters, the potential barrier is much narrower, and this results in faster response time and larger current gain in the bipolar mode of operation.

4.6 Static Induction Diode

The bipolar mode of operation of SIT can also be used to obtain diodes with low forward voltage drop and negligible carrier storage effect [10,11,13,15]. A SID can be obtained by shorting a gate to the emitter of the SIT [16,17]. Such diode has all the advantages of the SIT such as thermal stability and short switching time. The cross section of such diode is shown in Fig. 4.11.

The quality of the SID can be further improved with more sophisticated emitters (Fig. 4.10B and C). The SI diode with Schottky emitter was described by Wilamowski in 1983 [18] (Fig. 4.12). A similar structure was later published by Baliga [19].

4.7 Lateral Punch-Through Transistor

Fabrications of SI transistors usually require very sophisticated technology. It is much simpler to fabricate a lateral punch-through transistor (LPTT), which operates on the same principle and has similar characteristics [20] (Fig. 4.13). The cross section of the LPTT is shown in Fig. 4.14.

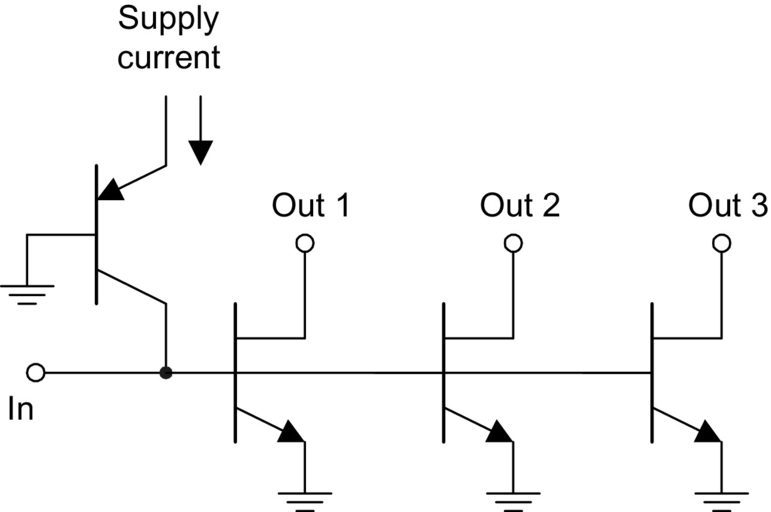

4.8 Static Induction Transistor Logic

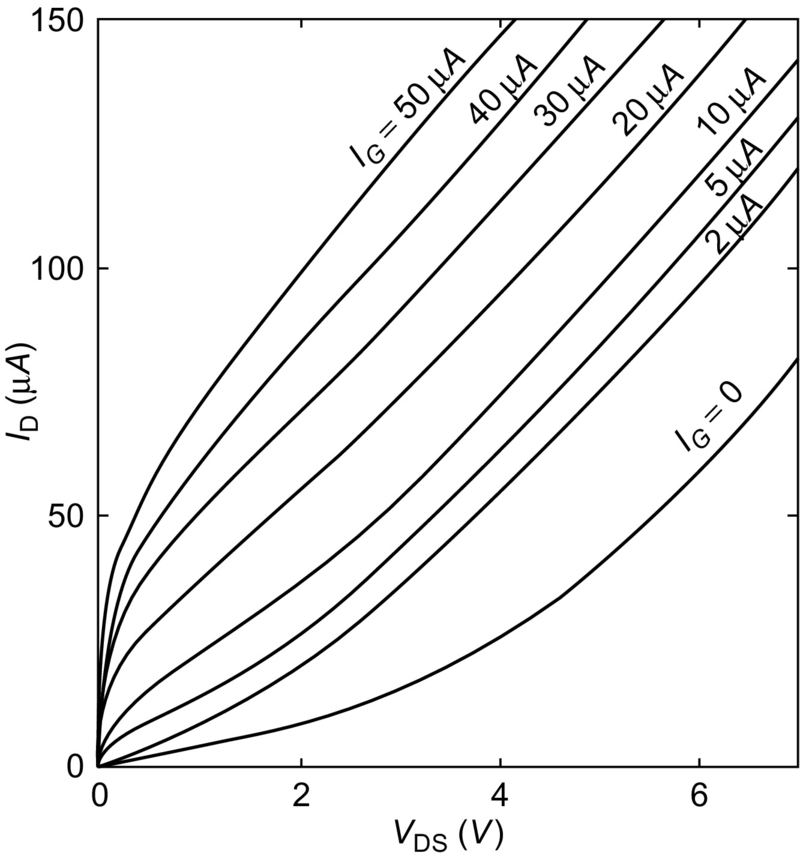

The SITL was proposed by Nishizawa and Wilamowski [5,6]. This logic circuit has almost 100 times better power-delay product than its I2L competitor. Such drastic improvement of the power-delay product is possible because the SITL structure has a significantly smaller junction parasitic capacitance and also the voltage swing is reduced. Figs. 4.15 and 4.16 illustrate the concept of SITL. Measured characteristics of n-channel transistor of the static induction logic are shown in Fig. 4.17.

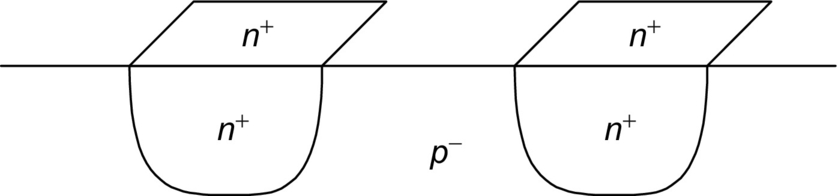

4.9 BJT Saturation Protected by SIT

The SI transistor can also be used instead of a Schottky diode to protect a bipolar junction transistor against saturation [21]. This leads to faster switching time. The concept is shown in Figs. 4.13 and 4.18. Note that this approach is advantageous to the solution with Schottky diode, since it does not require additional area on a chip and it does not introduce additional capacitance between the base and the collector. The base-collector capacitance is always enlarged by the Miller effect, and this leads to slower switching in the case of the solution with the Schottky diode.

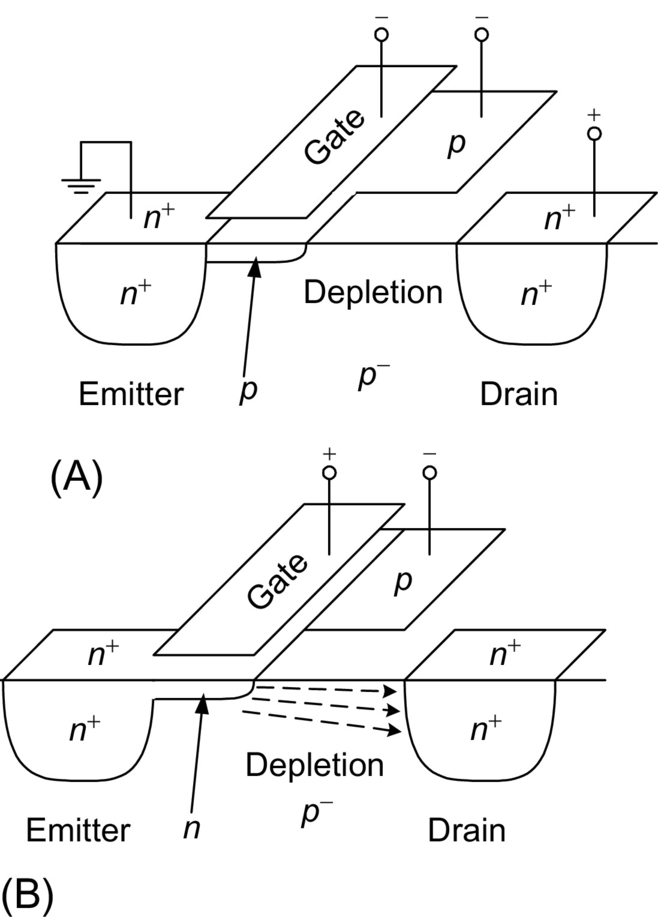

4.10 Static Induction MOS Transistor

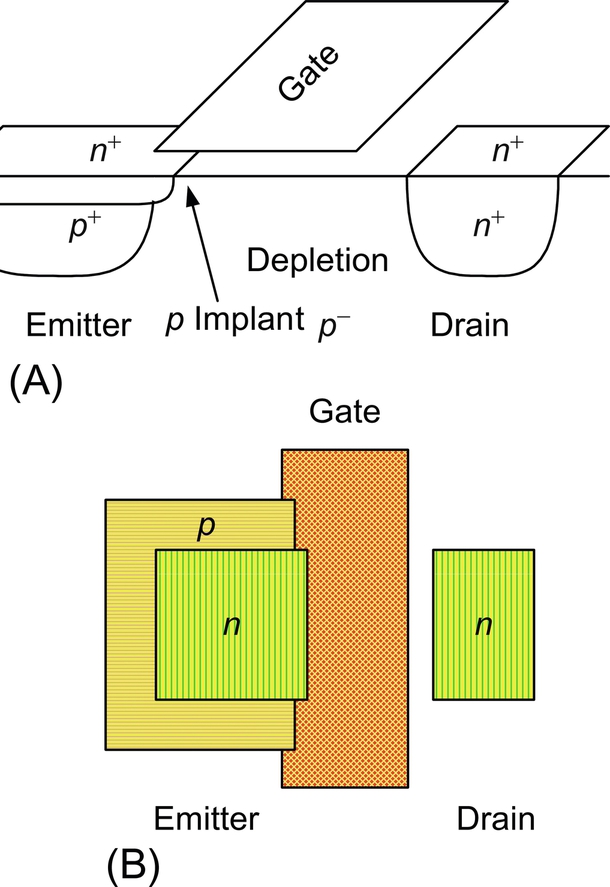

The punch-through transistor with MOS-controlled gate was described in 1983 [22,23]. In the structure in Fig. 4.19A, current can flow in a similar fashion as in the LPTT [20]. In this mode of operation, carriers are moving far from the surface with a velocity close to the saturation velocity. The real advantage of such structure is the very low gate capacitance.

Another implementation of static induction MOS transistor (SIMOS) is shown in Fig. 4.20. The buried p+ layer is connected to the substrate, which has a large negative potential. As a result, the potential barrier is high, and the emitter-drain current cannot flow. The punch-through current may start to flow when the positive voltage is applied to the gate, and in this way, the potential barrier is lowered. The p-implant layer is depleted, and due to the high horizontal electric field under the gate, there is no charge accumulation under this gate. Such a transistor has several advantages over the traditional MOS transistor (Fig. 4.21).

1. The gate capacitance is very small, since there is no accumulation layer under the gate.

2. Carriers are moving with a velocity close to saturation velocity.

3. Much lower substrate doping and the existing depletion layer lead to much smaller drain capacitance.

The device operates in a similar fashion as MOS transistor in subthreshold conditions, but this process occurs at much higher current levels. Such “bipolar mode” of operation may have many advantages in VLSI applications.

4.11 Space Charge Limiting Load (SCLL)

Using the concept of the space charge-limited current flow, it is possible to fabricate very large resistors on a very small area. Moreover, these resistors have a very small parasitic capacitance. For example, a 50 kΩ resistor requires only several square μm when a 2 μm feature size technology is used [7].

Depending on the value of the electric field, the device current is described by the following two equations. For a small electric field, v(x)=μE(x):

For a large electric field, v(x)=const:

Moreover, these resistors, which are based on the space charge limit flow, have a very small parasitic capacitance (Fig. 4.22).

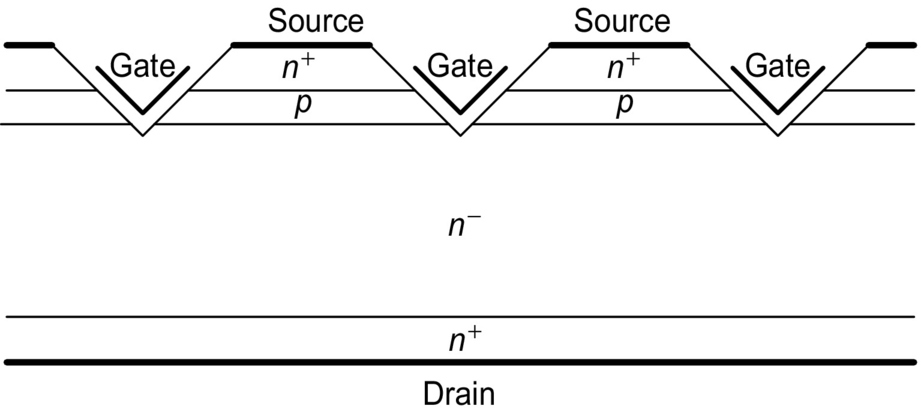

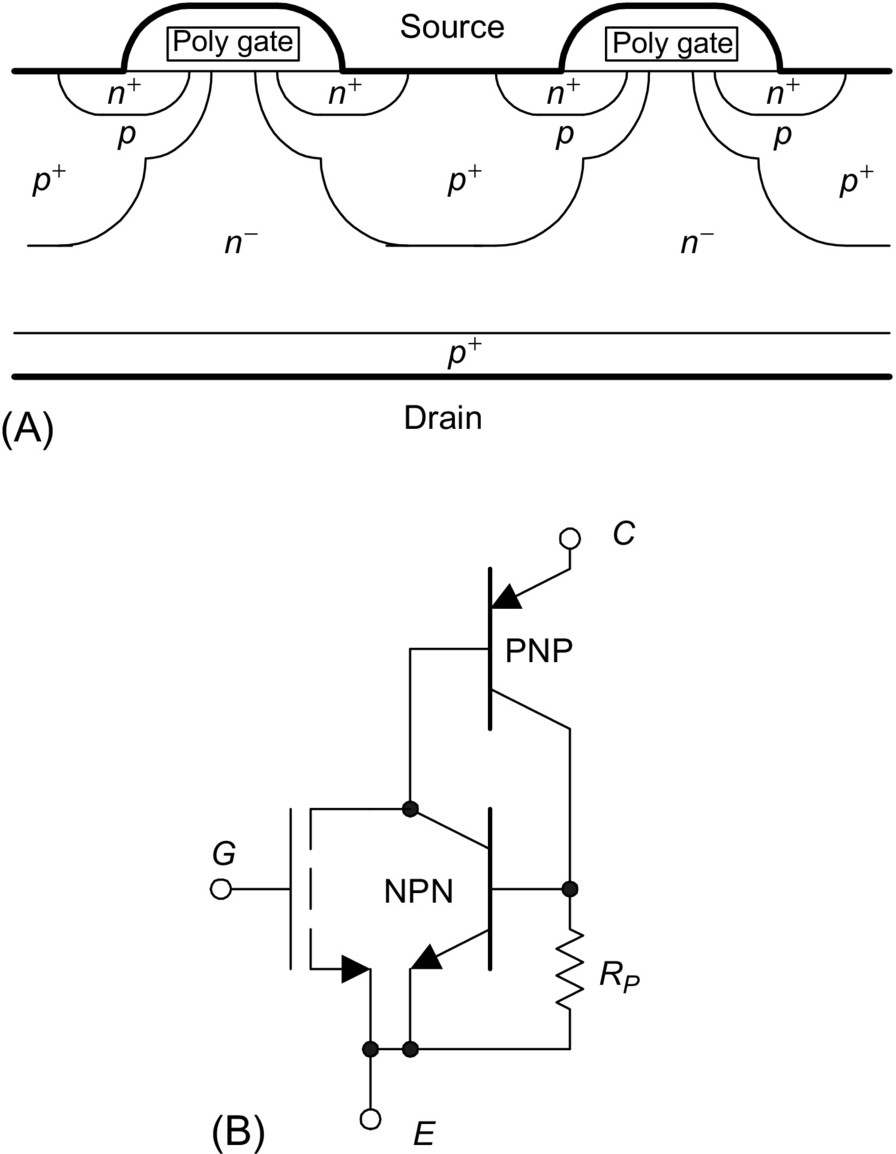

4.12 Power MOS Transistors

Power MOS transistors are being used for fast switching power supplies and for switching power converters. They can be driven with relatively small power, and switching frequencies could be very high. High switching frequencies lead to compact circuit implementations with small inductors and small capacitances. Basically, only two technologies, DMOS and VMOS, are used for power MOS devices as shown in Figs. 4.23 and 4.24.

A more popular structure is the DMOS shown in Fig. 4.24. This structure also uses the SIT concept. Note that for large drain voltages, the n-region is depleted from carriers, and statically induced electric field in the vicinity of the virtual drain is significantly reduced. As a result, this transistor may withstand much larger drain voltages, and also the effect of channel length modulation is significantly reduced. The later effect leads to larger output resistances of the transistor. Therefore, the drain current is less sensitive to drain voltage variations. The structure in Fig. 4.24 can be considered as a composition of the MOS transistor and the SIT transistor as is shown in Fig. 4.25.

The major disadvantage of power MOS transistors is relatively large drain series resistance and much smaller transconductance in comparison with bipolar transistors. Both of these parameters can be improved dramatically by a simple change of the type of drain, in the case of n-channel device from n-type to p-type drain. This way, the integrated structure is being built where its equivalent diagram consists of MOS transistor integrated with bipolar transistor. Such structure has β times larger transconductance (β is the current gain of bipolar transistor) and much smaller series resistance due to the conductivity modulation effect caused by holes injected into lightly doped drain region. Such device is known as insulated-gate bipolar transistors (IGBT) as shown in Fig. 4.26. Their main disadvantage is large switching time limited primarily by poor switching performance of bipolar transistor. Another difficulty is related to a possible latch-up action of a four-layer n+pn−p+ structure. This undesired effect could be suppressed by using heavily doped p+ region in the base of NPN structure, which leads to significant reduction of the current gain of this parasitic transistor. The gain of other PNP transistor must be kept large, so the transconductance of the entire device is large too. The IGBT transistor has breakdown voltages up to 1500 V; turn off times are in range 0.1–0.5 μs. They may operate with currents above 100 A with a forward voltage drop about 3 V.

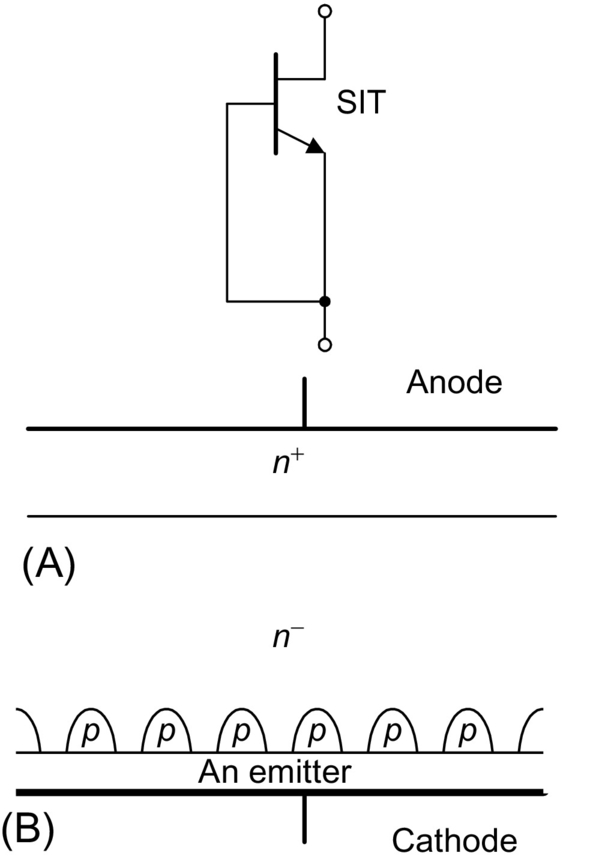

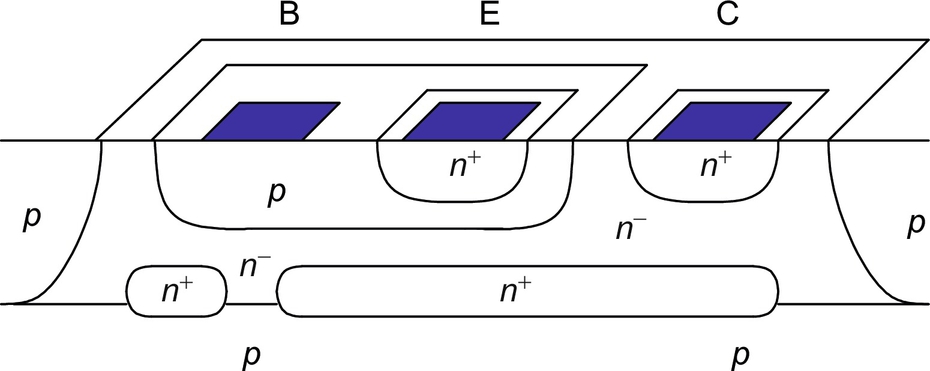

4.13 Static Induction Thyristor

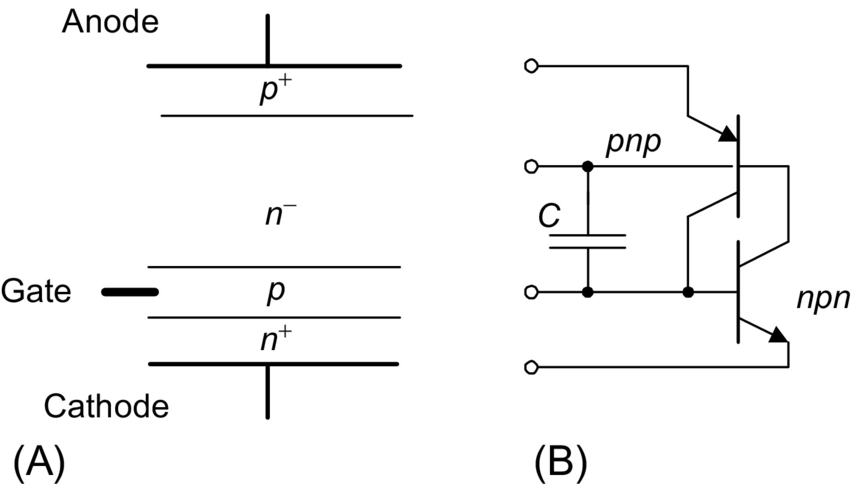

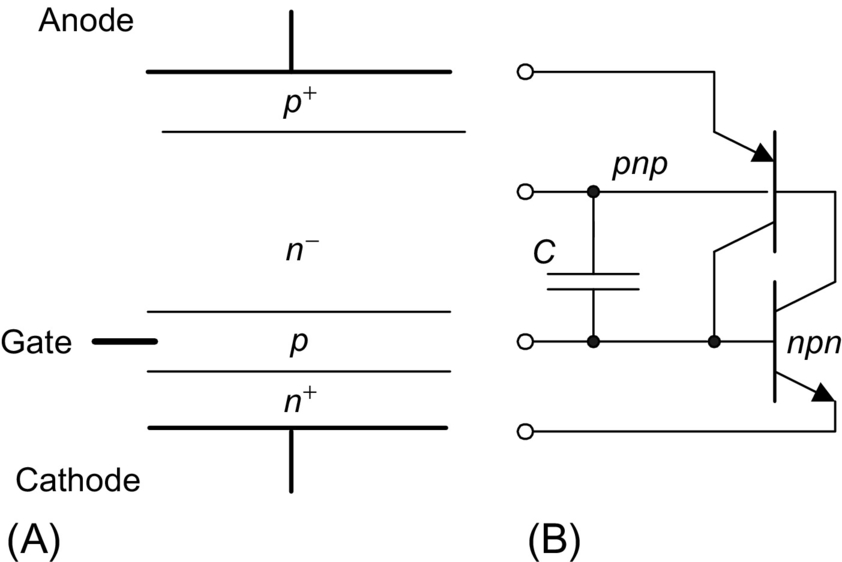

There are several special semiconductor devices dedicated to high power applications. The most popular is thyristor known also as silicon control rectifier (SCR). This device has a four-layer structure as shown in Fig. 4.27A, and it can be considered as two transistors npn and pnp connected as shown in Fig. 4.27B.

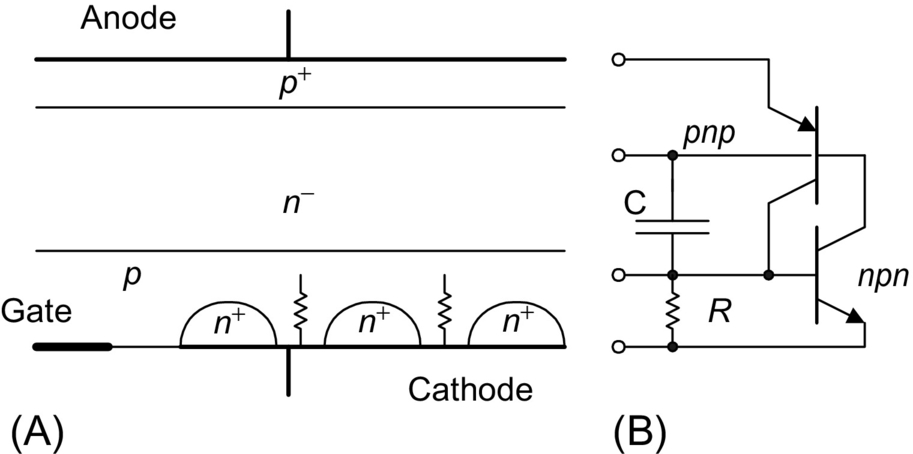

In normal mode of operation (anode has positive potential), only one junction is reverse-biased, and it can be represented by capacitance C. A spike of anode voltage can therefore get through capacitor C, and it can trigger SCR. This behavior is not acceptable in practical application, and therefore, a different device structure is being used as is shown in Fig. 4.28. Note that by shorting gate to cathode by resistor R, it is much more difficult to trigger the npn transistor by spike of anode voltage. This way, rapid change of anode voltages is not able to trigger thyristor. Therefore, this structure has a very large dv/dt parameter.

When NPN transistor is replaced with SI transistor, parameters of a thyristor can be significantly improved. For example, with breaking voltage in the range of 5 kV and current of 600 A, the switching on time can be as short as 100 ns, and dv/dt parameter can be as large as 50 kV/s [15,24].

Most of the SCRs sold in the market comprise an integrated structure composed of two or more thyristors. This structure has both large dv/dt and di/dt parameters. This structure consists of internal thyristor that significantly amplifies the gate signal.

One can notice that the classical thyristor as shown in Fig. 4.27 can be turned off by the gate voltage, while integrated SCR shown in Fig. 4.29 can be only turned off by reducing anode current to zero. Most of the SCRs sold in the market have an integrated structure composed of two or more thyristors. This structure has both large dv/dt and di/dt parameters.

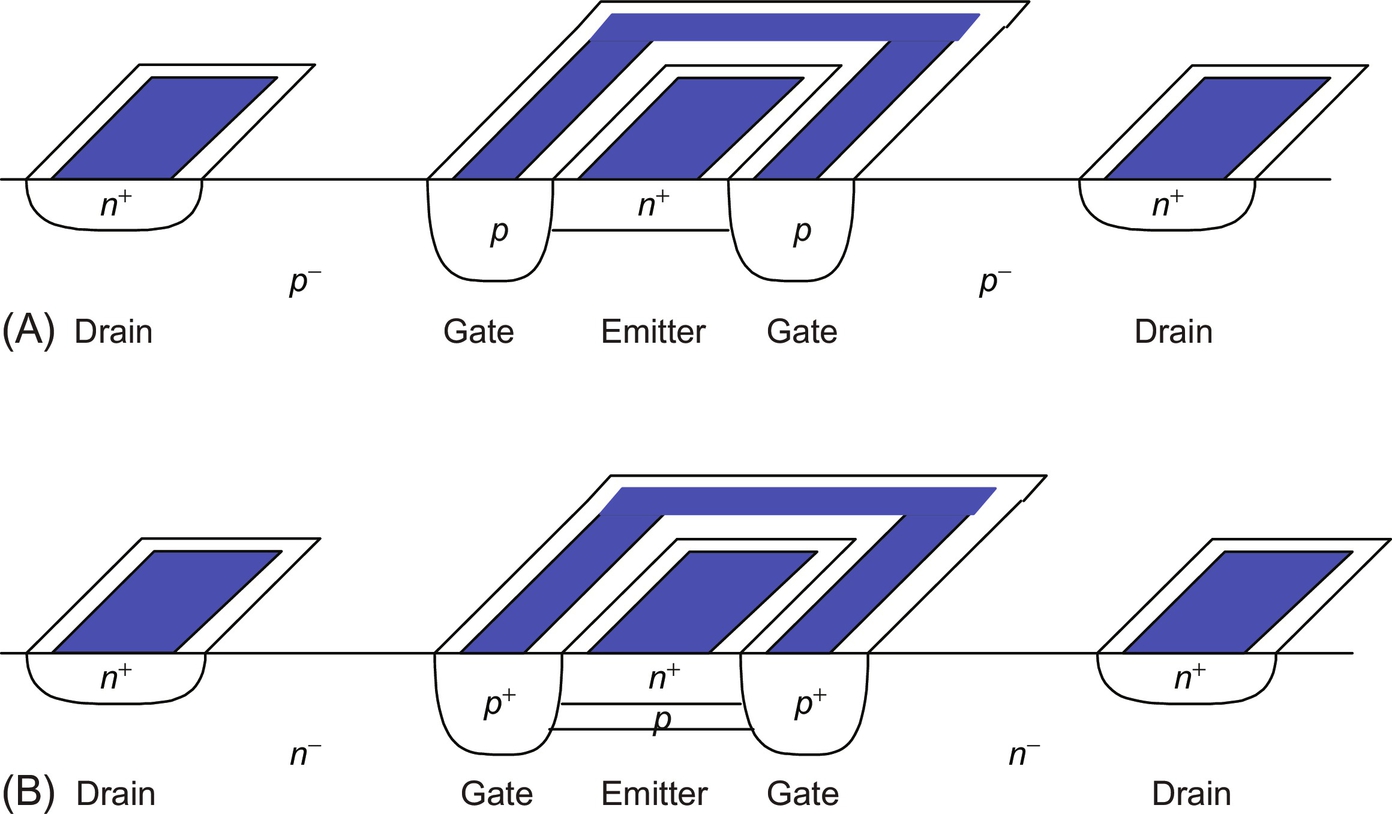

4.14 Gate Turn Off Thyristor

For the dc operation, it is important to have a thyristor that can be turned off by the gate voltage. Such thyristor has a structure similar to the one shown in Fig. 4.27. It is important, however, to have significantly different current gains β for pnp and npn transistors. The current gain of npn transistor should be as large as possible, and the current gain of pnp transistor should be small. The product of βnpn and βpnp should be larger than one. This can be easily implemented using SI structure as shown in Fig. 4.30.