2.2 SEQUENTIAL CIRCUITS

Combinational logic produces outputs that are strictly functions of the inputs. But many computations and digital systems require the storage and reuse of information as part of a sequence of operations. The behavior of a sequential circuit depends on its initial state and the sequence of inputs it has experienced. Sequential circuits have state memory as well as combinational logic. For the most part, we only consider synchronous sequential circuit examples, that is, in which they are clocked by a regular clock, and whose inputs must be stable at the time of a clock edge transition. This method or discipline is much easier to implement and check out in practice, but we must be aware that externally applied signals may not always conform. We take up this point later in the chapter.

2.2.1 Latches and Flip-Flops

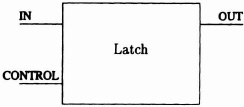

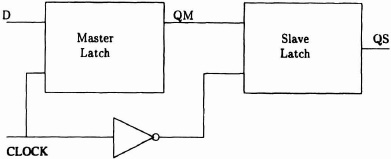

Sequential machines require memory to hold their current state. The latch is the most elementary form of memory, and is illustrated in Figure 2–2. If the CONTROL input is true, the output OUT becomes the same as input IN. If CONTROL goes false, OUT retains its previous value. This is often referred to as a transparent latch, because of the direct connection between input and output, and is level-sensitive. It is in fact a basic element in the Algotronix architecture, but limited in utility, because the transparency allows signals to pass through. If we take two latches in cascade, we can form an edge-triggered D-type flip-flop, as shown in Figure 2–3. While CLOCK is true, the master latch is transparent, and keeps note of the latest D input. As soon as CLOCK goes false and propagates through the inverter, the mater latch value is asserted as the output of the slave latch, which maintains this value until the next time CLOCK goes from FALSE to TRUE. Changing state takes time, and there is a minimum time—setup time for an input to be stable prior to the CLOCK going false. Edge triggering allows us to guarantee single actions following an event. The D (delayed) flip-flop is a basic element of a number of FPGA architectures, including the Xilinx family.

It is very straightforward to construct other types of flip-flops from these primitive types. For example, a toggle flip-flop changes state every time it is clocked, and this can be arranged simply by feeding the inverted output of a D flip-flop back to its D input. Some flip-flops can be cleared or set at any time, independent of the clock, and such facilities are referred to as asynchronous clear or set. Other forms for memory include static serial- or random-access memory (RAM) used to hold configuration information. This is referred to in the next chapter.

Figure 2–2. Transparent latch.

Figure 2–3. D-type flip-flop.