4MB Pages

The 4MB feature was first implemented in the Pentium® processor. It was migrated backwards into the later versions of the 486 and is present in all IA32 processor subsequent to the Pentium®.

Enabling 4MB page capability is accomplished by setting CR4[PSE] = 1 (PSE = Page Size Extension; see Figure 21-6 on page 497). 4MB page capability is detected by executing a CPUID request type 1. Bit 3 in EDX = 1 indicates that it is supported (see Figure 21-2 on page 491).

The Problem

Assume that a task will be accessing a large buffer in memory and that it is the OS's intention that the processor should follow the same rules of conduct when accessing any location(s) in this buffer. As an example, assume it is a 2MB video frame buffer in memory. Using 386-compatible Paging, the OS would have to set up 512 PTE's, each one associated with a 4KB page within the buffer and each one with identical attribute bit settings (i.e., the attribute bits that define the processor rules of conduct within the page). Setting up and maintaining 512 PTEs is a lot of housekeeping.

How To Set Up a 4MB Page

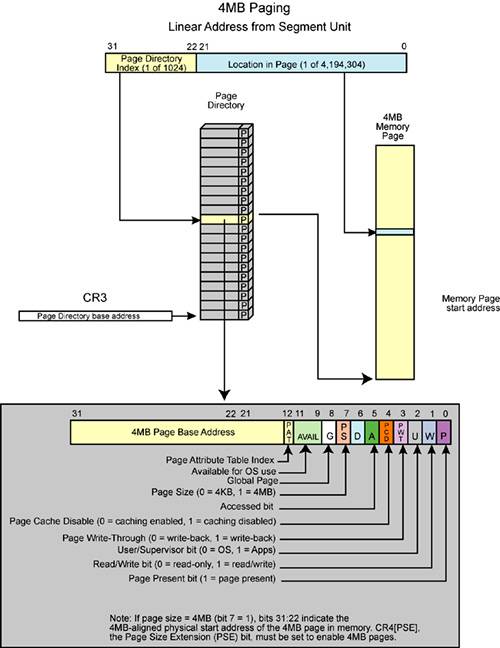

Assuming that CR4[PSE] = 1, the OS sets up a 4MB page by creating a PDE (a Page Directory Entry) with the format shown in Figure 21-9 on page 503:

PDE[31:22] contains the upper 10 bits of a 4MB page in physical memory. The processor assumes that the lower 22 bits are all zero.

The OS can set up any number of PDEs (up to the 1024 entry maximum size of the Page Directory) as 4MB page entries.

Other PDEs Can Point to Page Tables

It should also be stressed that PDEs may have the PS bit = 0 and therefore contain the pointer to a Page Table that tracks the location of 4KB pages (see Figure 12-7 on page 225).

The Address Translation

When a 32-bit linear memory address is submitted to the Paging Unit for translation, the upper 10 bits selects one of the PDEs in the Page Directory. If PDE[PS] = 1, this PDE contains the 4MB-aligned base address of a 4MB physical page in memory and the PDE attribute bits defines the processor's rules of conduct when performing a read or write access anywhere within the 4MB region of memory.