Priority Agent Arbitration

Example Priority Agents

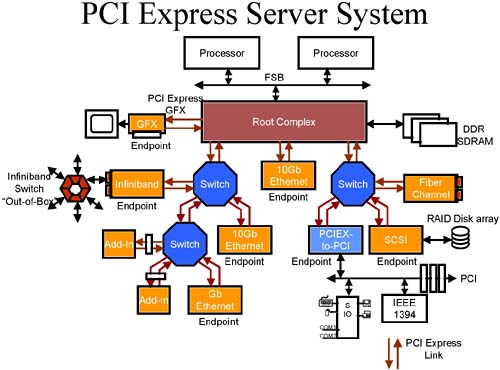

While the physical processors are very polite to each other, the system may include one or more agents that play by different rules. They are referred to as Priority Agents. In Figure 46-1 on page 1167, whenever a PCI Express device adapter initiates a read from or write to system memory, the Root Complex must arbitrate for ownership of the FSB to initiate a snoop transaction. To do so, it uses the BPRI# signal (Bus Priority agent request; note that there is only one BPRI# signal). The Root Complex acts as the surrogate FSB Request Agent when a PCI Express device adapter requires access to system memory. BPRI# is an input to each processor's arbiter and, when asserted, it informs the processors that the Priority Agent would like to break into the rotation in order to initiate a transaction.

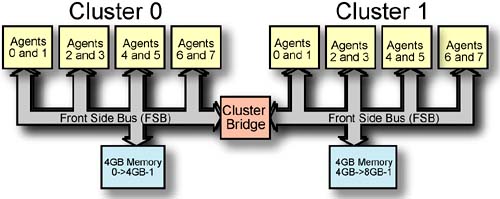

Figure 46-2 on page 1167 illustrates two Xeon MP clusters interconnected via an Cluster Bridge. When a processor on one FSB initiates an access to cacheable memory on the other FSB, the Cluster Bridge must arbitrate for ownership of the other FSB and it does so by asserting BPRI# to the array of processors on the target FSB.

Only one device is permitted to assert BPRI# at a time. In the case where multiple Priority Agents reside on the FSB, there must therefore be some method for the Priority Agents to arbitrate amongst themselves to determine which of them gets to use BPRI# to request ownership (if more than one of them needs to issue a transaction request at the same time).

Priority Agent Beats Symmetric Agents, Unless...

When a Priority Agent is requesting ownership at the same time that one or more of the symmetric agents are also requesting ownership, the Priority Agent normally wins.

The only case where the Priority Agent will be unsuccessful in winning ownership of the FSB is the case where a physical processor has already acquired ownership and has asserted the LOCK# signal (because it has initiated a locked transaction series when performing a locked read/modify/write operation). This prevents the Priority Agent from acquiring ownership until the physical processor completes the locked transaction series and deasserts the LOCK# signal. The reasons why a symmetric agent might assert LOCK# are covered in the section entitled “Pentium® 4 Locked Transaction Series” on page 1177. The Priority Agent must deal with the cases described in Table 46-1 on page 1168.

| Case | Resulting Actions |

|---|---|

| A physical processor initiates a transaction request in the same clock that the Priority Agent asserts BPRI#, but does not assert LOCK#. | In this case, the Priority Agent assumes ownership after the physical processor finishes delivery of its transaction request. This will be 3 clocks after BPRI# assertion. |

| A physical processor initiates a transaction request and asserts LOCK# in the same clock that the Priority Agent is asserting BPRI#. | The Priority Agent cannot assume ownership until the physical processor deasserts LOCK#. |

| A physical processor has acquired ownership on the same rising-edge of the clock that BPRI# is sampled asserted. In this case, the physical processor proceeds with its transaction request and may or may not assert LOCK#. |

|

Using Simple Approach, Priority Agent Suffers Penalty

Refer to Figure 46-3 on page 1171. A Priority Agent may be designed in such a manner that it doesn't check to see if a physical processor has started a transaction request (in other words, it doesn't check the state of the ADS# signal) in order to determine when (and if) it can take ownership of the Request Phase signal group. Rather, it checks in the two clocks immediately following its assertion of BPRI# to see if LOCK# is asserted. If LOCK# is sampled asserted on the rising-edge of BCLK0 in either of the two clocks immediately after BPRI# is asserted, then a physical processor had already asserted LOCK# and the Priority Agent can't take ownership until LOCK# is deasserted. If LOCK# is sampled deasserted during both of these two clocks, however, one of three conditions is true (but the Priority Agent doesn't know which):

No physical processor has initiated a transaction request during these two clocks and LOCK# is not being held asserted by a physical processor that issued an earlier transaction request.

A physical processor started a transaction request on the same clock that BPRI# was driven asserted, but it did not assert LOCK#.

A physical processor started a transaction request on the clock after BPRI# was asserted, but it did not assert LOCK#.

In any of these cases, the Priority Agent has gained ownership. However, because it doesn't check ADS# to determine which of the three cases is true, it must assume the worst case—case number 3. In this case, the physical processor has sampled BPRI# asserted at the start of the clock in which the physical processor initiated its transaction request. It does not assert LOCK#, and it will therefore honor the BPRI# assertion. The Priority Agent cannot assume ownership, however, until 3 clocks after the physical processor starts its transaction request. This is a total of 3 clocks after BPRI# is asserted.

An arbitration event occurs on clock 2 in Figure 46-3 on page 1171 and physical processor 0 acquires ownership in clock 3 (BPRI# was not asserted at the start of clock 2, so physical processor 0 is not prevented from taking ownership). Also at the start of clock 2, the Priority Agent asserts BPRI# to request ownership, but this isn't detected by physical processor 0 until clock 3, the clock in which it starts to drive out a transaction request. This means that physical processor 0 has successfully acquired ownership and will proceed with the issuance of its transaction request.

When physical processor 0 starts its request in clock 3, it keeps BREQ0# asserted in case it has another transaction to issue later. Also in clock 3, physical processor 1 asserts BREQ1# to request ownership, but it won't gain ownership until physical processor 0 relinquishes ownership.

In this example, the Priority Agent uses the simple approach to test for ownership acquisition. It samples LOCK# on clocks 3 and 4 to see if any physical processor has asserted it. In this case, it is sampled deasserted both times, indicating that either no physical processor is issuing a request, or one is, but has not asserted LOCK#. In either case, it means the Priority Agent will be the next owner of the Request Phase signal group.

Physical processor 0 samples BREQ1# asserted on clock 4 and relinquishes ownership in clock 5.

An arbitration event occurs on clock 6 when BREQ0# is sampled deasserted indicating that physical processor 0 has relinquished ownership to physical processor 1. In clock 7, ownership passes to physical processor 1.

At the start of clock 5, 3 clocks after it asserted BPRI#, the Priority Agent takes ownership of the Request Phase signal group, initiates a transaction request and deasserts BPRI# to let the next physical processor in the rotation use the Request Phase signal group after it is done. Note that if none of the physical processors had their BREQn# lines asserted, the Priority Agent could have left BPRI# asserted to park ownership on itself in case it needed to issue another transaction request in the future. Since both physical processors 0 and 1 have asserted their respective BREQs, however, the Priority Agent is a gentleman and releases BPRI#.

At the start of clock 6, BPRI# is sampled deasserted by the physical processors, indicating that the next symmetric owner can start issuing a request one clock later (at the start of clock 7).

On clock 7, symmetric ownership passes to physical processor 1.

When physical processor 1 issues its transaction request at the start of clock 7, it keeps BREQ1# asserted to park symmetric ownership on itself in case it needs to issue another transaction request later.

Smarter Priority Agent Gets Ownership Faster

The previous section demonstrated that a Priority Agent that only checks the state of the LOCK# signal to determine if and when it has attained ownership takes at least three clocks to attain ownership (longer if LOCK# is sampled asserted). This section describes how a Priority Agent that checks both ADS# and LOCK# can attain ownership in 1 or 2, rather than 3 clocks.

Table 46-1 on page 1168 detailed the possibilities when a Priority Agent asserts BPRI# to request ownership. If the Priority Agent checks to see (by sampling ADS#) if a symmetric agent has actually started a transaction request in the same clock that it asserts BPRI# or in the clock immediately following its assertion, it can decrease the latency in gaining ownership from three to two clocks (Figure 46-5 on page 1174) or to one clock (Figure 46-4 on page 1173).

Ownership Attained in 1 BCLK

If the Priority Agent samples ADS# asserted (indicating that a symmetric agent has initiated a transaction request) and LOCK# deasserted (but it isn't locking the Request Phase signal group) in the same clock that it asserts BPRI#, the Priority Agent can assume ownership in 2 clocks. Refer to Figure 46-4 on page 1173.

In clock 1, processor 0 initiates a transaction, but does not assert LOCK#.

On clock 2, the Priority Agent begins to assert BPRI#. The Priority Agent also samples ADS# asserted and LOCK# deasserted, indicating that a symmetric agent has initiated a transaction request but has not locked the Request Phase signal group.

All of the symmetric agents sample BPRI# asserted on clock 3, indicating that the Priority Agent will be the next owner of the Request Phase signal group.

On clock 4, after agent 0 has completed issuance of its transaction request, the Priority Agent initiates its transaction request and deasserts BPRI#. BREQ1# is also sampled asserted (by the other symmetric agents as well as the Priority Agent), indicating that symmetric agent 1 wishes to issue a transaction request.

On clock 5, agent 0 deasserts BREQ0# to yield symmetric ownership to agent 1.

On clock 6, the symmetric agents detect BREQ0# deasserted and select the next symmetric owner, agent 1.

On clock 7, symmetric ownership passes to agent 1 and it initiates its transaction.

Ownership Attained in 2 BCLKs

If the Priority Agent samples ADS# asserted (indicating that a symmetric agent has initiated a transaction request) and LOCK# deasserted (the symmetric agent isn't locking the Request Phase signal group) in the clock after it asserts BPRI#, the Priority Agent can assume ownership in two clocks. Refer to Figure 46-5 on page 1174.

At the start of clock 1, physical processor 0 initiates a transaction request and the Priority Agent asserts BPRI# to request ownership. ADS# is sampled deasserted by the Priority Agent, indicating that a physical processor didn't start a transaction request in the previous BCLK. LOCK# is sampled deasserted. The Priority Agent checks ADS# and LOCK# again at the start of the next clock.

At the start of clock 2, ADS# is sampled asserted by the Priority Agent, indicating that a physical processor has just initiated a transaction request. In addition, LOCK# is sampled deasserted by the Priority Agent, indicating that the physical processor didn't lock the FSB.

The Priority Agent can assume ownership after the physical processor completes issuing its transaction request one clock later. This occurs at the start of clock 3.

Be Fair to the Common People

The spec dictates that the Priority Agent must keep BPRI# deasserted for at least two clocks after its last deassertion of BPRI#. This opens a window that permits one of the symmetric agents to acquire ownership of the Request Phase signal group if any of them need to issue a transaction request.

Priority Agent Parking

The spec states that the Priority Agent can keep BPRI# asserted when it asserts ADS# and initiates its final (or only) transaction request. The exact wording is “provided it can guarantee forward progress of the symmetric agents.” In other words, be fair to the physical processors. If the Priority Agent has parked ownership on itself by keeping it BPRI# asserted, it can retain ownership until:

It has to initiate another transaction request, or

It samples any of the BREQn# lines asserted, indicating that one or more of the physical processors require access to the Request Phase signal group,