The μop Pipeline

Introduction

The μop pipeline is the path that μops follow as they make their way through the processor core to be executed and then retired.

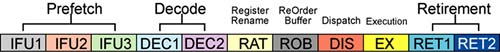

The P6 Processor's Instruction Pipeline

The μop pipeline in the P6 processor family (see Figure 35-2 on page 845) consisted of 10 stages divided into three sections:

The in-order front end of the pipeline. Guided by the processor's Branch Prediction logic, the IA32 instructions that comprise the currently executing program are fetched from memory (line-by-line) and are decoded in program order. The resulting μops are queued in strict program order. If any μop references one or more of the GPRs, those references are tagged to point to one or more of the processor's Alias Registers rather than to the GPRs. The μops are then placed (still in strict program order) in a 40 entry buffer called the Re-Order Buffer, or ROB. In addition, they are also placed in the Reservation Station (the RS; this is the μop scheduler).

The out-of-order middle section of the pipeline. Once the μops are placed in the ROB and the RS, they become visible to the instruction scheduler (which is part of the RS). The scheduler evaluates all of the μops in the RS and, as long as the data operands required for a μop's execution are available (or will become available by the time the μop arrives at the execution unit) and the appropriate execution unit is available, μops can be dispatched for execution out of program order.

The in-order rear end section of the pipeline. In the final stages of the pipeline, in each clock cycle the processor core copies the results of the execution of the next three μops in strict program order to the register set and then retires those three instructions.

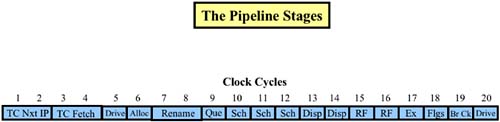

The Pentium® 4's μop Pipeline

The μop pipeline (see Figure 35-3 on page 846) in the Pentium® 4 processor family (up to but not including the 90nm version, Prescott) consists of 20 stages and, like the P6 pipeline, it is divided into an in-order front end, the out-of-order-middle section, and the in-order final section. A detailed discussion of the pipeline can be found in “Pentium® 4 Core Description” on page 897. The numbered of pipeline stages was doubled to enable the processor to be clocked at a significantly higher rate.

Figure 35-3. The Pentium® 4 μop Pipeline

The 90nm Pentium® 4's Instruction Pipeline

The μop pipeline in the 90nm Pentium® 4 processor family consists of 31 stages. Once again, the number of pipeline stages was increased to enable the processor to be clocked at a significantly higher rate. As of this writing, Intel® has not documented the stages that comprise the new pipeline. There's a lot of speculation regarding this, but the author chooses not to deal with speculative discussions.