The Debug Store (DS) Mechanism

Introduction

If enabled, the Debug Store mechanism permits the processor to automatically store branch (Branch Trace Store, or BTS) and PEBS records in a memory buffer referred to as the DS save area.

A detailed description of the PEBS feature can be found in “Precise Event-Based Sampling” on page 1414.

The DS mechanism is available in Real Mode.

Feature Detection

The programmer can determine if a processor supports the DS feature by executing a CPUID request type 1 and verifying that EDX[21] =1. Assuming that the bit is set to one, the programmer must also check the following two bits:

IA32_MISC_Enable[12] (see Figure 56-21 on page 1373) indicates whether or not a processor supports the PEBS feature.

IA32_MISC_Enable[11] (see Figure 56-21 on page 1373) indicates whether or not a processor supports the BTS feature.

Setting Up the DS Feature

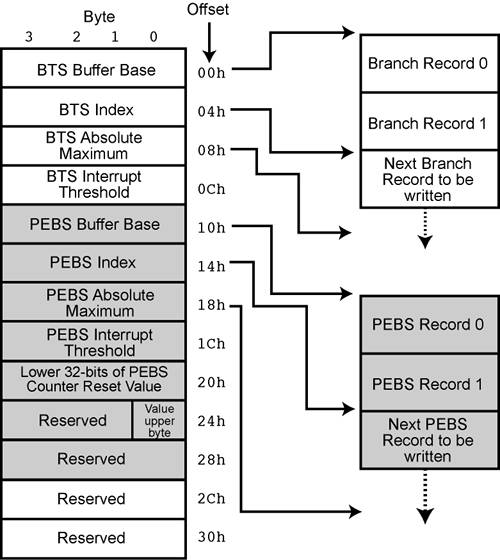

Before either the PEBS or BTS features are enabled, the programmer must first create the DS save area in memory (see Figure 56-18 on page 1369 and Table 56-4 on page 1367). The DS save area is divided into three parts:

The buffer management area defines the location and size of the BTS and PEBS buffers.

The PEBS buffer.

Figure 56-18. The DS Save Area Format

After setting up the buffer management area, the programmer may then safely enable the PEBS and/or BTS features.

Enabling the BTS Feature

The BTS feature is enabled by setting DEBUGCTL[BTS] (see Figure 54-4 on page 1311) = 1. Note that prior to enabling this feature, the DS feature must first be set up (see “Setting Up the DS Feature” on page 1367).

Enabling the PEBS Feature

The PEBS feature is enabled by setting IA32_PEBS_Enable[24] = 1 (see “Enabling PEBS” on page 1415 and Figure 56-26 on page 1417).

The PEBS Record Format

Each PEBS record consists of 40 bytes structured as shown in Figure 56-19 on page 1370.

Figure 56-19. The PEBS Record Format

The BTS Record Format

Each BTS record consists of 12 bytes structured as shown in Figure 56-20 on page 1371.

Figure 56-20. The BTS Record Format